Multi-Pulse Rectifier Based on an Optimal Pulse Doubling ...

Operation of the LCC-type parallel resonant converter as a low harmonic rectifier

-

Upload

independent -

Category

Documents

-

view

1 -

download

0

Transcript of Operation of the LCC-type parallel resonant converter as a low harmonic rectifier

288 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 46, NO. 2, APRIL 1999

Operation of the LCC-Type Parallel ResonantConverter as a Low Harmonic Rectifier

Vijayakumar Belaguli,Member, IEEE,and Ashoka K. S. Bhat,Fellow, IEEE

Abstract—A 1-��� high-frequency transformer isolated single-stage ac-to-dc controlled rectifier with low line current harmonicdistortion using a variable-frequency controlled LCC-type (orseries–parallel) resonant converter (SPRC) is presented. A simpleanalysis and design procedure is used for designing the converterfor low line current harmonic distortion and high power factoroperation. The converter performance characteristics have beenverified with SPICE3 simulations (without active control) andexperimental prototype SPRC (rated at 150 W, with and withoutactive control) for variation in load as well as line voltage. Whenoperated with active current shaping, this converter operatesin zero-voltage-switching mode for complete range, maintainingpower factor close to unity with low line current distortion andlow peak current compared to the parallel resonant converter.

Index Terms—AC-to-DC power converter, frequency control,HF transformer, power factor, resonant power conversion, zero-voltage switching.

I. INTRODUCTION

RECENTLY, operation of ac-to-dc converters with highpower factor (PF) and low line current total harmonic

distortion (THD) has formed an active research area [1]–[9].This is due to the enforcement (either already existing orbeing proposed) of strict harmonic regulations (e.g., IEC555).Advantages of high-frequency (HF) resonant converters havebeen utilized in ac-to-dc converters [1]–[7], [9] for realizingpower conversion with improved performance (high efficiency,high PF, and low line current THD, etc.) while reducing thesize, weight, and cost. Active line current control has beenused for a single-ended resonant converter to reduce the THDin [2].

In [1] and [4], operation of resonant converters with highline PF has been reported. The line current THD was veryhigh (18% around half load to about 48% at full load) and theswitch peak currents did not decrease with the load currentsince a parallel resonant converter (PRC) was used [4]. Theline current THD has been reduced by utilizing active currentcontrol scheme in a variable-frequency controlled PRC [5],[6]. It was operated in leading PF [zero-current switching(ZCS)] mode and results were given only for full load andat rated line voltage. In addition, due to ZCS operation,

Manuscript received October 12, 1997; revised August 21, 1998. Abstractpublished on the Internet January 18, 1999. An earlier version of this paperwas presented at the 1996 IEEE Applied Power Electronics Conference, SanJose, CA, March 3–9, 1996.

V. Belaguli is with the Department of Electrical Engineering, SingaporePolytechnic, Singapore 139651.

A. K. S. Bhat is with the Department of Electrical and Computer Engi-neering, University of Victoria, Victoria, B.C., V8W 3P6 Canada (e-mail:[email protected]).

Publisher Item Identifier S 0278-0046(99)02707-0.

switching frequency required at lower load currents will belower, resulting in an increase in the size of the transformer,while retaining all the well-known disadvantages of leadingPF operation [10]. Also, no voltage regulation loop wasincorporated.

The desirable features of LCC-type (or series–parallel)resonant converter (SPRC) are well established [10]. Variable-frequency operation of the SPRC on the utility line (withoutactive control) has been discussed briefly in [4]. However,the major problems were the requirement to keep the ratioof switching frequency to series resonance frequency high tomaintain lagging PF (ZVS) mode of operation, resulting inhigher switch peak currents.

In this paper, operation of the full-bridge SPRC with highPF and reduced line current THD is presented. It is shown that,with a proper design, it is possible to get reduced line currentTHD, even without active control of line current. However,at full load, the converter operates in leading PF mode nearzero crossings of line voltage. To reduce THD further, anactive current waveshaping feedback circuit is used to vary theswitching frequency. This method also keeps the converter inZVS mode for the complete line cycle. An additional feedbackcircuit is used to regulate the output load voltage, also. Someother main features of the proposed converter are single-stagepower conversion, HF isolation, leakage inductance is part ofresonant circuit, and lower peak current stresses.

II. CIRCUIT DESCRIPTION AND OPERATION

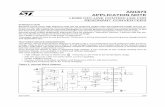

The HF transformer isolated ac-to-dc converter using thevariable-frequency full-bridge SPRC is shown in Fig. 1. Asmall dc-link capacitor is used to filter only the switchingfrequency components [1], [4], [7], [9]. The resonant tank cir-cuit is formed by the components (leakage inductanceof the HF transformer), , and placed on the secondaryside of the HF transformer. In the output section, andare designed to filter the switching frequency current rippleand the 120-Hz voltage ripple, respectively. The converteris designed for continuous current mode (CCM), to operateat rated minimum input ac voltage and maximum ratedload current . The output voltage regulation is achievedby increasing the switching frequency for both reduced loadcurrents and higher input voltages. In open-loop operation,the frequency is varied to regulate the output voltage (nocurrent control), while for closed-loop operation (i.e., withactive control), the switching frequency is varied all alongthe ac cycle to draw nearly sinusoidal line current, as well asfor voltage regulation. As the switching frequency,, is very

0278–0046/99$10.00 1999 IEEE

BELAGULI AND BHAT: OPERATION OF THE LCC-TYPE PARALLEL RESONANT CONVERTER AS A LOW HARMONIC RECTIFIER 289

Fig. 1. HF transformer isolated ac-to-dc converter employing SPRC bridgefor variable-frequency CCM operation. This converter is operated with orwithout active control. For active control, the control circuit schematic shownin Fig. 7 is used.

high as compared to the frequency of the 120-Hz pulsatingdc-link voltage , the converter can be considered to havereached steady state for each HF switching cycle to simplifythe analysis presented in Section III.

III. CONVERTER ANALYSIS AND DESIGN OF

SPRCFOR LOW LINE CURRENT THD

A. Analysis

Making simplified assumptions for the analysis of the SPRCand using complex ac circuit analysis method for an SPRC[4], [7], [10] operated with variable-frequency control, the dcconverter gain can be shown to be

(1)

where is the rated minimum peak input ac voltage,is the output voltage referred to primary,

is the series resonant frequency,, is the

transformer leakage inductance, and is theHF transformer turns ratio.

Fig. 2(a) and (b) shows the plot of the voltage gainas afunction of normalized switching frequency, for capacitanceratios of 0.5 and 1, respectively.

For sinusoidal line current operation, the currentthroughthe output inductor is double-frequency sinusoid (on 60-Hz scale) [4], [7] with peak value being equal to twicethe average current delivered to the load at constant output

(a)

(b)

Fig. 2. DC voltage gain,M , for CCM operation of the SPRC: (a) forCs=Ct = 0:5 and (b) forCs=Ct = 1.

voltage and is defined as (referred to primary side)

(2)

where .Also, the series resonant is given by

(3)

where ,.

The ac analysis required to determine the ZVS condition andthe component stresses is given in the Appendix. Using theconverter gain relation given in (1), one can plot the requiredvariation in converter gain , switching frequency ratio

and as shown in Fig. 3, over the 60-Hz ac cycleto draw nearly sinusoidal line current from the utility linewhen active control is used. The sharp dip in thecurve

290 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 46, NO. 2, APRIL 1999

(a)

(b)

Fig. 3. Variation of seriesQs(t), required converter gainM(t), and nor-malized switching frequency ratioys(t), to get sinusoidal line current overac half cycle at rated minimum input ac voltage and rated maximum loadconditions: (a) forCs=Ct = 0:5 and (b) forCs=Ct = 1.

around the region below 30and above 150 in Fig. 3 isdue to insufficient gain near the zero crossings at chosenoperating point. From this curve, it is evident that, for thechosen variation in , it is not possible to derive therequired gain from the converter and, hence, discontinuity inthe input current, as well as in the output inductor currentwaveform, is expected beyond this point, even with activecontrol irrespective of .

However, if no active control is used, one has to choosethe operating point very carefully to satisfy all the designconstraints, such as reduced peak current stresses, small vari-ation in frequency for output voltage regulation, and requiredconverter gain for at least 30–150 of ac line cycle (as themost part of total output power is delivered in this range)to obtain low line current distortion. Even though higher

will be the obvious choice to reduce the rms current,it increases the peak current stresses beyond a certain value,due to the decrease in converter gain and increase inoutput current for the same rated power output. For variable-frequency CCM operation, choosing the closer to theload-independent point on the gain curve reduces the rangeof variation in frequency required from full load to light load,in addition to reduction in inverter peak current stresses.

From the ac analysis given in (1)–(3) and the Appendix[7], it was found that, for a given peak value of

, good compromised design values obtained were, for . Similarly, for

, the design values were , .The above design values for the converter will ensure ZVSoperation, in addition to generating the required voltage gainfor most of the ac voltage cycle, while delivering rated outputpower at rated minimum input voltage.

B. Design ExampleDesign procedure is illustrated using a design example for

a converter having the following specifications:

average output power W;input rms voltage 85–110 V;output voltage V dc;output current ripple(peak-to-peak of ) 20% of ;

output voltage ripple(peak-to-peak of 120 Hz) 1% of ;

switching frequency 50 kHz.

The design calculations are done for an SPRC deliveringa peak power of by choosing the and at thepeak of the ac line cycle for low line condition (i.e.,V rms). Using the relations for and , the followingcomponent values are obtained for the two cases.

Case 1— : , ,V, ,

H, F, and F.Case 2— : , ,

V, , ,H, F, and F.

For the output section, for the specified ripple, using theequations given in [4] and [7], the filter components (for Case1) were found to be H and F.

IV. SPICE SIMULATION RESULTS

The 150-W 120-V output 50-kHz converter designed inthe earlier section was simulated in SPICE3 to evaluate theconverter performance without active current control.

For a capacitance ratio of , the harmonicdistortion in the line current waveform [Fig. 4(a)-(i)] is 14.1%at full load and rated minimum input voltage. The SPRCoperates in lagging PF mode near the peak, and leading PFmode near the zero crossings of the ac voltage cycle, as shownin Fig. 4(a)-(ii) and (a)-(iii), respectively. At full load, theSPRC operates in continuous capacitor voltage mode (CCVM),as shown in Fig. 4(a)-(iv). The line current waveform for 53%load shown in Fig. 4(b) has a THD of 15.5%. The SPRCoperated fully in lagging PF mode for decreased load currentsdue to increased for regulated output.

Similarly for a capacitance ratio , at full loadwith minimum input voltage, the line current THD is 19.8%[Fig. 4(c)-(i)]. The converter operated in lagging PF mode[Fig. 4(c)-(ii)] near peak of line cycle and in discontinuouscapacitor voltage mode (DCVM) [Fig. 4(c)-(iii)], while deliv-ering rated output power at rated minimum input ac voltage.Since the converter operated in DCVM at full load and inCCVM at reduced load, the range of variation in switchingfrequency to regulate the output was larger for a capacitanceratio of 1. In all these simulations, the switching frequencywas increased to regulate the output voltage at reduced loads.

BELAGULI AND BHAT: OPERATION OF THE LCC-TYPE PARALLEL RESONANT CONVERTER AS A LOW HARMONIC RECTIFIER 291

(a)-(i) (b)

(a)-(ii) (c)-(i)

(a)-(iii) (c)-(ii)

(a)-(iv) (c)-(iii)

Fig. 4. SPICE3 simulation waveforms for 150-W (full load) 50-kHz variable-frequency SPRC bridge operating on the utility line (Vac = 85 V rms) withoutactive control (Cs=Ct = 0:5 andV 0

o = 120 V). (a) At full load: (a)-(i) line voltagevac and line currentiac; (a)-(ii) lagging PF mode (near peak of line cycle);(a)-(iii) leading PF mode (near valleys of line cycle); (a)-(iv)vab; vCt; vCs (near peak). (b) At 53% load:vac; iac. (c) Full load (Cs=Ct = 1; V 0

o = 90

V): (c)-(i) vac; iac; (c)-(ii) lagging PF (near peak); (c)-(iii)vab; vCs; vCt (near peak).

292 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 46, NO. 2, APRIL 1999

(a)-(i) (b)-(i)

(a)-(ii) (b)-(ii)

(a)-(iii) (c)-(i)

(a)-(iv) (c)-(ii)

Fig. 5. Experimental waveforms and line current harmonic spectra for different load conditions for a variable-frequency SPRC bridge operating on theutility line (Fig. 1) without active control (Cs=Ct = 0:5, Ld = 500 �H, Cd = 1000 �F, V 0

o = 120 V). Minimum input voltage,Vac = 85 V rms:(a) full load (RL = 96 ); (b) 53% load (RL = 180 ). Maximum input voltage,Vac = 110 V rms: (c) full load (RL = 96 ). (a)-(i) vac; iac; id,and Vo; (a)-(ii) vab; iL; vCt, and vCs (near peak); (a)-(iii)vab; iL; vCt, and vCs (near valleys); (a)-(iv) harmonic spectra ofiac. (b)-(i) vac and iac;(b)-(ii) harmonic spectra ofiac. (c)-(i) vac and iac; (c)-(ii) harmonic spectra ofiac.

BELAGULI AND BHAT: OPERATION OF THE LCC-TYPE PARALLEL RESONANT CONVERTER AS A LOW HARMONIC RECTIFIER 293

(d)-(i) (d)-(ii)

Fig. 5. (Continued.)Experimental waveforms and line current harmonic spectra for different load conditions for a variable-frequency SPRC bridge operatingon the utility line (Fig. 1) without active control (Cs=Ct = 0:5, Ld = 500 �H, Cd = 1000 �F, V 0

o = 120 V). Maximum input voltage,Vac = 110

V rms: (d) 53% load (RL = 180 ). (d)-(i) vac and iac; (d)-(ii) harmonic spectra ofiac.

TABLE IEXPERIMENTAL RESULTS FOR A 150-W AC-TO-DC VARIABLE-FREQUENCY SPRCWITHOUT ACTIVE CONTROL

It must also be noted that the line current waveforms shownin Fig. 4(a)-(i), (b), and (c)-(i) are unfiltered and include HFripple.

V. EXPERIMENTAL RESULTS

Based on the design presented in Section III-B, a breadboardmodel of the SPRC rated at 150 W, operating on a 60-Hz,85–110 V utility line was built using IRF640 MOSFET’sin a bridge configuration using readily available 1 : 1 HFtransformer having 12 turns each. The SPRC was controlledusing a high-speed UC2825 pulsewidth modulation (PWM)controller, configured for variable-frequency operation.

A. Without Active Control

The various waveforms and line current harmonic spectraobtained from the prototype model are presented in Figs. 5and 6 for different loading conditions and ratios of 0.5and 1, respectively.

1) For —Fig. 5: The THD [harmonic spectrashown in Fig. 5(a)-(iv)] obtained for the line current waveform(full load, rated minimum input voltage) shown in Fig. 5(a)-(i)is 13.5%. The lagging PF and leading PF operation along withthe resonant capacitor voltage waveforms at full load, nearthe peak and the valleys of the ac voltage cycle are shownin Fig. 5(a)-(ii) and (a)-(iii), respectively. At full load, the

predominant harmonic components are the fifth and seventh.The THD reached a minimum of 11.9% at 53% load, asshown in the harmonic spectra [Fig. 5(b)-(ii)] of line current[Fig. 5(b)-(i)]. The maximum distortion occurred at an operat-ing frequency of 54.5 kHz, at 80% load, due to overboostingeffect at all points along the ac cycle. At 10% load, thePF decreased due to increased magnitude of third harmoniccomponent, with a THD of 22.3%. The switch peak switchcurrent reduced from 4.54 A (1.816 p.u.) at full load to 3.75 A(1.5 p.u.) at 10% load. At full load, the peak voltages across

and are 628 V (5.233 p.u.) and 218 V (1.817 p.u.),respectively.

For an input voltage of 110 V rms, the line current wave-forms obtained are presented in Fig. 5(c)-(i) and (d)-(i). TheTHD reached a maximum (due to square waveform) of 34.5%at full load and a minimum of 12.8% at 53% load, as shownin Fig. 5(c)-(ii) and (d)-(ii), respectively. At 53% load, thethird harmonic component is negligible. For regulated output,the required variation (increase) in switching frequency for thecomplete load and line variation is 50–63.93 kHz, as shown inTable I(a). The switch peak current reduced from 4.9 A (1.96p.u.) at full load to 3.5 A (1.4 p.u.) at 10% load.

2) For —Fig. 6: At full load and rated min-imum input voltage, the line current waveform shown inFig. 6(a)-(i) has a THD of 18.9% [Fig. 6(a)-(ii)]. The THDreached a maximum of 37.47% [Fig. 6(b)] and 37.35%, at 60%

294 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 46, NO. 2, APRIL 1999

(a)-(i) (b)-(i)

(a)-(ii) (b)-(ii)

(c)-(i) (d)-(i)

(c)-(ii) (d)-(ii)

Fig. 6. Experimental waveforms and line current harmonic spectra for the ac-to-dc converter (Fig. 1) without active control (Cs=Ct = 1, Ld = 500 �H,Cd = 1000 �F, V 0

o = 90 V). (i) Waveformsvac and iac; (ii) harmonic spectra ofiac, for the following operating conditions.Vac = 85 V rms: (a) full load(RL = 54 ); (b) 60% load (RL = 90 ). Vac = 110 V rms: (c) full load (RL = 54 ); (d) 50% load (RL = 108 ).

and 80% rated load, for rated minimum and maximum inputvoltage, respectively. This phenomenon occurs approximatelyat 60 kHz due to overboosting effect all along the valleysof the ac voltage and, hence, quasi-square waveform of linecurrent. The switch peak current reduced from 5.28 A (1.188p.u.) at full load to 3.2 A (0.72 p.u.) at 11.25% load, with ratedminimum voltage (85 V rms). At full load, the peak voltagesacross and are 377 V (3.14 p.u.) and 198 V (1.65p.u.), respectively. Fig. 6(c) and (d) shows the waveforms andharmonic spectra of line current for full load and half loadwith 110-V input. With rated maximum input voltage, thepeak current carried by the switches reduced from 4.95 A

(1.114 p.u.) at full load to 3.3 A (0.742 p.u.) at 11.25% load.Selected experimental results are given in Table I(b).

The overboosting effect observed in variable-frequency op-eration of the SPRC is due to the converter operating point(switching frequency ratio ) being close to the resonant peakpoint, where the achieve their maximum at their respective

. For example, Fig. 2(a) shows that achieves its maxi-mum, at a switching frequency ratio , approximatelyfor all values of . The same explanation holds goodfor ratio of 1 [Fig. 2(b)] and occurs at .

All these experimental waveforms and the results are ingood agreement with the SPICE3 simulation results. The line

BELAGULI AND BHAT: OPERATION OF THE LCC-TYPE PARALLEL RESONANT CONVERTER AS A LOW HARMONIC RECTIFIER 295

Fig. 7. Active current control scheme block diagram for SPRC bridge (Fig. 1) operating on the utility line.

(a)-(i) (b)-(i)

(a)-(ii) (b)-(ii)

(a)-(iii) (c)-(i)

(a)-(iv) (c)-(ii)

Fig. 8. Experimental waveforms for a variable-frequency SPRC bridge operating on the utility line with active current control (Cs=Ct = 0:5, Ld = 500 �H,Cd = 1000 �F, V 0

o = 120 V). Vac = 85 V rms: (a) full load (RL = 96 ); (b) 53% load (RL = 180 ). Vac = 110 V rms: (c) full load(RL = 96 ). (a)-(i) vac and iac; (a)-(ii) harmonic spectra ofiac; (a)-(iii) vab and iL (near peak); (a)-(iv)vab and iL (near valleys). (b)-(i)vac andiac; (b)-(ii) harmonic spectra ofiac. (c)-(i) vac and iac; (c)-(ii) harmonic spectra ofiac.

PF is maintained in the upper 90’s, for the entire load rangewith variable-frequency operation of the SPRC, even without

active control. It is shown in the next section that, by usingactive line current control, the THD is further reduced.

296 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 46, NO. 2, APRIL 1999

(c)-(iii) (d)-(i)

(c)-(iv) (d)-(ii)

Fig. 8. (Continued.)Experimental waveforms for a variable-frequency SPRC bridge operating on the utility line with active current control (Cs=Ct = 0:5,Ld = 500 �H, Cd = 1000 �F, V 0

o = 120 V). Vac = 110 V rms: (c) full load (RL = 96 ); (d) 53% load (RL = 180 ). (c)-(iii) vab and iL(near peak); (c)-(iv)vab and iL (near valleys). (d)-(i)vac and iac; (d)-(ii) harmonic spectra ofiac.s

B. With Active Current Control

In order to reduce the line current THD, a variable-frequency active current control scheme has been imple-mented, and the details are given below.1) Implementation of Active Current Control Scheme:The

block schematic of the active current control scheme imple-mented with the breadboard model is shown in Fig. 7. In orderto keep the output voltage constant for varying input voltageand output load, and also to keep the input line current closeto sinusoidal and in phase with the line voltage, the proposedcontrol scheme is equipped with two control loops.

a) The outer voltage feedback loop:The outer outputvoltage loop forces the ac-to-dc converter to work as a dcvoltage source at its output. This is a slow-varying loopconsisting of output voltage sensing amplifier, proportionalintegral (PI) compensator-1, and a multiplier. The outputvoltage is sensed by a voltage divider () and comparedwith a set reference signal ( ) using a PI compensator. Theerror signal in combination with sinusoidal referenceis used to generate the varying amplitude sinusoidal referencecurrent for referencing the inner current control loop.

b) The inner current control loop:The current-control-ling feedback loop is used to monitor the mains currentand force it to follow the mains voltage. This control loopconsists of a PI compensator-2, with inputs as conditionedline current waveform to be shaped and the referencecurrent . The reference current signal has quick controlof the line current, while the output voltage error has aslow control over the line current. The result is that the dc-linkcurrent varies as a rectified sinusoid and the voltage regulationis achieved by adjusting the amplitude of the voltage errorsignal . Finally, the control voltage to the UC2825controller is generated by summation of errorand afterproper scaling and limiting circuits. Note that the attenuator

block K4 is used to obtain the additional dc offset voltage sothat the controller input voltage for VCO section does not gobelow a lower limit (which decides the lowest frequency ofoperation) at any point of time and for changes in load, thusavoiding below resonance operation.

The various waveforms obtained from variable-frequencyactive control scheme are presented in Figs. 8 and 9, corre-sponding to capacitance ratios 0.5 and 1, respectively.

2) For —Fig. 8: The THD at full load[Fig. 8(a)-(i)] and 53% load [Fig. 8(b)-(i)] are 8% and 9.61%,at rated minimum input voltage, as shown in the harmonicspectra of Fig. 8(a)-(ii) and (b)-(ii), respectively. The converteroperated with ZVS for all the switches throughout the ac cyclewith active control at full load, as shown on the HF scale inFig. 8(a)-(iii) and (a)-(iv). The switching frequency variationis from 50 kHz (near peak of line voltage) to about 55 kHz(near valleys of line voltage) at full load. The switch peakcurrent variation is from 4.8 A (1.92 p.u.) at full load to3.7 A (1.48 p.u.) at 10% load with rated minimum inputvoltage.

Corresponding to an input voltage of 110 V rms, the THDfor the line current waveforms shown in Fig. 8(c)-(i) and (d)-(i) were 9.2% [Fig. 8(c)-(ii)] and 14.36% [Fig. 8(d)-(ii)], atfull load and 53% load, respectively. The switch peak currentreduced from 5.04 A (2.016 p.u.) at full load to 3.5 A (1.4p.u.) at 40% rated load.

3) For —Fig. 9: Corresponding to a capaci-tance ratio of 1 with rated minimum input voltage, the linecurrent waveforms shown in Fig. 9(a)-(i) and (b)-(i) have adistortion figure of 7.4% [Fig. 9(a)-(ii)] and 11.33% [Fig. 9(b)-(ii)], at full load and 50% load, respectively. As shown inFig. 9(a)-(iii) and (a)-(iv) for full load, the switching frequencynear the peak and valleys of line voltage are 51.28 and 58.82kHz, respectively. The inductor peak current carried by the

BELAGULI AND BHAT: OPERATION OF THE LCC-TYPE PARALLEL RESONANT CONVERTER AS A LOW HARMONIC RECTIFIER 297

(a)-(i) (b)-(i)

(a)-(ii) (b)-(ii)

(a)-(iii) (c)-(i)

(a)-(iv) (c)-(ii)

Fig. 9. Experimental waveforms for a variable-frequency SPRC bridge operating on the utility line with active current control (Cs=Ct = 1, Ld = 500 �H,Cd = 1000 �F, V 0

o = 90 V). Vac = 85 V rms: (a) full load (RL = 54 ); (b) 50% load (RL = 108 ). Vac = 110 V rms: (c) full load(RL = 54 ). (a)-(i) vac and iac; (a)-(ii) harmonic spectra ofiac; (a)-(iii) vab and iL (near peak); (a)-(iv)vab and iL (near valleys). (b)-(i)vac andiac; (b)-(ii) harmonic spectra ofiac. (c)-(i) vac and iac; (c)-(ii) harmonic spectra ofiac.

switch reduced from 4.75 A (1.068 p.u.) at full load to 2.9A (0.65 p.u.) at 22.5% load. At full load, the peak voltagesacross and are 270 V (2.25 p.u.) and 190 V (1.583p.u.), respectively.

For an input voltage of 110 V rms, the THD for the line cur-rent waveforms at full load and half load shown in Fig. 9(c)-(i)and (d)-(i) are 13% [Fig. 9(c)-(ii)] and 12.11% [Fig. 9(d)-(ii)],respectively. In all these line current waveforms presented, thethird harmonic component is either absent or reduced to lessthan 3%. Also, the converter operates in ZVS mode for thecomplete operating range [refer to Fig. 9(a)-(iii), (a)-(iv), (c)-(iii), and (c)-(iv)]. The switch peak current reduces from 4.4A (0.99 p.u.) at full load to 3.15 A (0.709 p.u.) at 22.5% rated

load. At full load, the peak voltages across and are 325V (2.71 p.u.) and 205 V (1.708 p.u.), respectively.

The key results have been tabulated in Table II(a) and (b),for ratios of 0.5 and 1, respectively. The utility linevoltage had 2% THD.

The 150-W experimental converter was built only to demon-strate the principles of operation. This converter can be usedfor power levels of the order of 500 W–1 kW. It can easily beverified that the proposed converter satisfies the line currenttotal harmonic distortion specified in the IEC 1000-3-2 stan-dards [11]. Referring to Fig. 3 of [11], it can be concludedthat, for power levels less than 1.5 kW, the most stringentclass C standard is satisfied, even without active control.

298 IEEE TRANSACTIONS ON INDUSTRIAL ELECTRONICS, VOL. 46, NO. 2, APRIL 1999

(c)-(iii) (d)-(i)

(c)-(iv) (d)-(ii)

Fig. 9. Fig. 9. (Continued.)Experimental waveforms for a variable-frequency SPRC bridge operating on the utility line with active current control(Cs=Ct = 1, Ld = 500 �H, Cd = 1000 �F, V 0

o = 90 V). Vac = 110 V rms: (c) full load (RL = 54 ); (d) 50% load (RL = 108 ). (c)-(iii)vab and iL (near peak); (c)-(iv)vab and iL (near valleys). (d)-(i)vac and iac; (d)-(ii) harmonic spectra ofiac.

TABLE IIEXPERIMENTAL RESULTS FOR A 150 W, AC-TO-DC VARIABLE FREQUENCY SPRCWITH ACTIVE CONTROL

VI. CONCLUSIONS

The SPICE3 simulation and experimental results show that,by proper converter design, one can get low line currentTHD and high PF ( ) with a full-bridge SPRC, evenwithout active control. The capacitance ratio 0.5 is preferredas the THD figures, the peak current stresses, and range ofvariation in frequency from full load to light load are lower ascompared to those figures obtained for ratio 1, whenno active control is used. With the implementation of activecontrol scheme, the PF is maintained close to unity (0.99)with further reduction in THD. For active current control, acapacitance ratio of 1 is recommended as the THD figuresare lower (8% at full load). Switch peak current stresses arealso lower for ratio of 1. Due to DCVM operation, therectifier diode voltage stresses are slightly higher and requirelarger variation in frequency to regulate the output voltage. Theexperimental converter built had a switching frequency of 50kHz at full load and this was used only to demonstrate the highPF, low THD that can be obtained with variable-frequencyoperation of SPRC. However, higher switching frequency canbe used with active control scheme, as ZVS operation ismaintained over the entire 60-Hz ac cycle.

APPENDIX

AC ANALYSIS FOR ZVS AND COMPONENT STRESSES

The impedance (in per unit) looking into the terminalsand is

p.u. (A1)

where

(A2)

(A3)

Peak inductor current or transistor peak current,

p.u. (A4)

The initial inductor current (at ) is given by

p.u. (A5)

where

rad (A6)

For above resonance (or lagging PF) operation, i.e., for ZVS,must be negative.

BELAGULI AND BHAT: OPERATION OF THE LCC-TYPE PARALLEL RESONANT CONVERTER AS A LOW HARMONIC RECTIFIER 299

Peak voltage across the series capacitor,

p.u. (A7)

Peak voltage across the parallel capacitor,

V (A8)

REFERENCES

[1] D. Chambers, “A new high frequency resonant technique for dynamiccorrection of off-line converter input current waveforms,” inProc.Powercon-10,1983, pp. 1–7.

[2] J. He and N. Mohan, “Input-current shaping in line-rectification byresonant converters,” inConf. Rec. IEEE-IAS Annu. Meeting,1987, pp.990–995.

[3] E. B. G. Nijhof, “Resonant power supply (RPS) converters: The solutionfor mains/line pollution problems,”PCI, pp. 104–139, June 1986.

[4] M. J. Schutten, R. L. Steigarwald, and M. H. Keraluwala, “Character-istics of load resonant converters in high power factor mode,” inConf.Rec. IEEE APEC’91,1991, pp. 5–16.

[5] J. Hong, E. Ismail, I. Khan, and R. Erickson, “Design of the parallelresonant converter as a low harmonic rectifier,” inConf. Rec. IEEEAPEC’93, 1993, pp. 833–840.

[6] J. Hong, D. Maksimovic, R. Erickson, and I. Khan, “Half cyclecontrol of the parallel resonant converter operated as high power factorrectifier,” in Conf. Rec. IEEE APEC’94,1994, pp. 556–562.

[7] V. Belaguli, “Series-parallel and parallel series resonant convertersoperating on the utility line—Analysis, simulation and experimentalresults,” Ph. D. dissertation, Dep. Elect. Comput. Eng., Univ. Victoria,Victoria, B.C., Canada, Jan. 1996.

[8] G. Rim and R. Krishnan, “AC to DC power conversion with unity powerfactor and sinusoidal input current,” inConf. Rec. IEEE APEC’91,1991,pp. 400–406.

[9] H. Seidel, “A high power factor tuned class D converter,” inConf. Rec.IEEE Power Electronics Specialists Conf.,Apr. 1988, pp. 1038–1042.

[10] R. L. Steigerwald, “A comparison of half-bridge resonant convertertopologies,” IEEE Trans. Power Electron.,vol. 3, pp. 174–182, Apr.1988.

[11] R. Redl, A. S. Kislovski, and B. P. Erisman, “Input-current clamping:An inexpensive novel control technique to achieve compliance withharmonic distortion,” inConf. Rec. IEEE APEC’96,San Jose, CA, 1996,pp. 145–151.

Vijayakumar Belaguli (S’93–M’95) received theM.E. degree from the Indian Institute of Science,Bangalore, India, and the Ph.D. degree from theUniversity of Victoria, Victoria, B.C., Canada, in1986 and 1996, respectively, both in electrical en-gineering.

From 1986 to 1991, he was a Software/HardwareDesign Engineer in the Switching Research and De-velopment Department, Indian Telephone Industries,Bangalore, India. Since 1996, he has been a Lecturerin the Electrical Engineering Department, Singapore

Polytechnic, Singapore. His areas of interest include modeling, analysis, anddesign of switch-mode resonant power supplies, power factor correction,microprocessor application in power electronics, and drives for EV’s.

Ashoka K. S. Bhat (S’82–M’84–SM’87–F’98) re-ceived the B.Sc. degree in physics and mathematicsfrom Mysore University, India, in 1972, the B.E.degree in electrical technology and electronics andthe M.E. degree in electrical engineering from theIndian Institute of Science, Bangalore, India, in1975 and 1977, respectively. and the M.A.Sc. andPh.D. degrees in electrical engineering from theUniversity of Toronto, Toronto, Ont., Canada, in1982 and 1985, respectively.

From 1977 to 1981, he was a Scientist in thePower Electronics Group, National Aeronautical Laboratory, Bangalore, In-dia, and was responsible for the completion of a number of research anddevelopment projects. He was also a Research Scholar at the Indian Instituteof Science during 1980–1981. After working as a Postdoctoral Fellow for ashort time, he joined the Department of Electrical Engineering, University ofVictoria, Victoria, B.C., Canada, where he is currently a Professor of ElectricalEngineering and is engaged in teaching and conducting research in the areaof power electronics. He has been responsible for the development of theElectromechanical Energy Conversion and Power Electronics Laboratories.

Dr. Bhat is a Fellow of the Institution of Electronics and TelecommunicationEngineers (India) and a member of the Association of Professional Engineersof British Columbia, Canada.