Illumination of the plasmasphere by terrestrial very low frequency transmitters: Model validation

Thermal design and experimental validation for optical transmitters

-

Upload

independent -

Category

Documents

-

view

2 -

download

0

Transcript of Thermal design and experimental validation for optical transmitters

Microelectronics Reliability 44 (2004) 755–769

www.elsevier.com/locate/microrel

Thermal design and experimental validationfor optical transmitters

Peter Z.F. Shi a,*, Albert C.W. Lu a, Y.M. Tan a, Stephen C.K. Wong a,Eric Tan b, Ronson Tan b

a Singapore Institute of Manufacturing Technology, 71 Nanyang Drive, Singapore 638075, Singaporeb E2O Communications Pte Ltd., 52 Serangoon North Avenue 4, Singapore 555853, Singapore

Received 26 February 2003; received in revised form 10 February 2004

Abstract

This paper describes a thermal design methodology for a 2.5 Gbps optical transmitter that mainly comprises a laser

array of 12 VCSELs and a laser driver module. An integrated heat sink design was performed and optimized through

modeling and simulation. Temperature regulation of the laser array has been performed through design and optimi-

zation of the thermal path (cavity and heat spreader) and separations (wire bonding lengths). Detailed module simu-

lation was performed after the heat sink design and the temperature regulations. To validate the simulation results, a

test vehicle of 2.5 Gbps transmitter was built up and tested under various thermal conditions. The airflow rate and

ambient temperature were controlled by a wind tunnel. It has shown that the experimental and detailed module sim-

ulation results are comparable. A cooling solution with natural convection has been achieved so that the case tem-

perature can be kept under 70 �C without using a fan. The modeling and simulation were done by using a

computational fluid dynamics (CFD) program.

� 2004 Elsevier Ltd. All rights reserved.

1. Background

In optical networking applications, especially LAN,

transponders hold the key to high-speed data bandwidth

where electro-optic conversion is presently inevitable.

Higher operating speed beyond 1 Gbps to meet the de-

mand for bandwidth in data- and telecommunications,

along with miniaturization of transponder modules, is

driving the need for enhanced thermal management

solutions. As the need for smaller and faster optical

transmitters and transponders arises, the need to under-

stand their thermal effects also gains importance [1–4].

Two main thermal issues facing optoelectronic

module designers are the thermal crosstalk between the

optochip (laser for the transmitter module or photodi-

ode for the receiver module) and the IC (laser driver for

* Corresponding author. Tel.: +65-6793-8515; fax: +65-6791-

6377/+65-6792-2779.

E-mail address: [email protected] (P.Z.F. Shi).

0026-2714/$ - see front matter � 2004 Elsevier Ltd. All rights reserv

doi:10.1016/j.microrel.2004.02.002

the transmitter or integrated pre- and limiting amplifier

for the receiver), and the module reliability if heat can-

not be dissipated and channeled away from the com-

ponent efficiently [5–8]. Optoelectronic modules are very

sensitive to temperature change which has harmful

effects on the module performance: (a) increasing the

emitted wavelength––one to two degree temperature

change could dramatically increase the crosstalk be-

tween two channels; (b) increasing threshold current

density which may result in failure of a device; (c)

decreasing output power of a laser; and (d) broadening

the spectral line width which affects its speed [9,10].

This paper describes a thermal design methodology

for a SNAP12 MSA (multi-source agreement) optical

module which is a 12 channel pluggable parallel optical

transmitter. It is electrically, optically and mechanically

compatible and connectorized, and helps to avoid data

congestion in networking equipment. The MSA-parallel

optical modules are based on vertical cavity surface

emitting laser (VCSEL) technology. By replacing copper

backplanes, the modules form the heart of the high

ed.

Nomenclature

A area, m2

cp specific heat at constant pressure, J/kgK

g gravitational acceleration, m/s2

k thermal conductivity, W/mK

P pressure, N/m2

S source term

T temperature, �Cu, v, w component of velocity vector in x, y, and z

directions, m/s

Greek Letters

e emissivity

l viscosity, kg/sm

q mass density, kg/m3

r Stefan–Boltzmann constant

Subscripts

a ambient

j junction

rad radiation

s surface

756 P.Z.F. Shi et al. / Microelectronics Reliability 44 (2004) 755–769

bandwidth networking products and solve the bottle-

necks in the core routers. This optical transmitter can be

used for applications up to a data rate of 2.5 Gbps per

channel, or an aggregate data rate of 30 Gbps with 12

independent optical signals for a transmission distance

up to 300 m. The module mainly consists of an array of

12 VCSELs with a wavelength of 850 nm, a driver IC

and a heat sink.

The case temperature requirements for the SNAP12

MSA optical transmitter are from 0 to 80 �C [11]. In this

study the maximum case temperature was targeted at 70

�C according to its application requirements. The normal

ambient temperature is around 25 �C and it is also tar-

geted at relatively high temperature at 50 �C in real

applications. The driver IC heat flux is about 14 W/cm2

for this application. With the continued miniaturization,

the maximum chip heat flux is expected to rise up

approximately from 16 W/cm2 in 2002 to 29 W/cm2 in

2010 for high performance in telecommunication appli-

cations [12]. In this study a driver IC heat flux of 24 W/

cm2 was investigated for potential high power applica-

tions. Thermal crosstalk was addressed to study the effect

of power loss on the thermal performance of the optical

transmitter. For a single power source, the thermal

resistance of a device is independent of its power. How-

ever for a multiple power source device, like in the optical

transmitter where there are two power sources, the driver

IC and the VCSEL array, powers on each of them will

affect their thermal resistances mutually.

In this work, an integrated heat sink design was

investigated. A DOE was performed to analyze the im-

pact of fin and pin fin configurations. An optimal heat

sink design was achieved based on the simulation. We

have attempted to regulate the temperature of the

VCSEL array by design and optimization of the thermal

path and the separations between the VCSEL array and

the driver IC. To ensure minimum wire bonding paras-

itics for enhanced electrical performance especially at

high data rate regions, it is desirable to keep bond wires

between the optical device and the driving or receiving

IC chip as short as possible. This, however, will increase

the thermal density significantly and therefore thermal

crosstalk between them. Attempt has been made to

separate them to isolate the heat dissipation from the

driver IC to the laser array. The heat transfer path has

been optimized through design of a cavity in the sub-

strate and a heat spreader under the substrate, and

assembly of the laser array in the cavity on the spreader.

After the heat sink design and optimization, and the

laser array temperature regulations, the full module and

the test vehicle of the optical transmitter were built up.

Detailed module numerical simulation and experimental

validation were performed. The thermal environments

used for this evaluation include the ambient temperature

at both normal and high ambient temperature 25 and 50

�C, and both natural and forced convections at the air

flow rate of 1 and 3 m/s. The power or heat flux is about

1.2 W or 14.3 W/cm2 for the driver IC, and 24 mW or

1.9 W/cm2 for the VCSEL array. In the experiment, the

ambient temperature and the wind flow rate were con-

trolled by using a Wind Tunnel. The modeling and

simulation were done by using a CFD (computational

fluid dynamics) program.

2. Methodology

The objective of this study is to perform thermal de-

sign for a 2.5 Gbps optical transmitter module through

heat sink design, thermal path optimization, detailed

module simulation and experimental validation. The

thermal budget is to maintain the case temperature of

the OE module below 70 �C. An uncooled cooling

solution is preferable under normal operation condi-

P.Z.F. Shi et al. / Microelectronics Reliability 44 (2004) 755–769 757

tions. Air-cooling needs to be explored for higher power

applications.

A 2.5 Gbps optical transmitter module was chosen as

the test vehicle for thermal design and optimization

through numerical simulation and experimental valida-

tion. The thermal modeling and simulation were per-

formed by using a computational fluid dynamics (CFD)

program, Flotherm. The thermal experimental valida-

tion was carried out by using a thermal characterization

system including a wind tunnel and a thermal analyzer.

2.1. Mathematical models

The solution procedures are based on CFD tech-

niques for the numerical simulation of fluid flow, heat

transfer and related processes such as radiation occur-

ring within and around optoelectronic modules. The

general governing equations are conservation of mass,

momentum and energy. They are shown in compact

form for an incompressible liquid of constant viscosity

as follows [6,7]:

• Conservation of mass

r �~u ¼ 0 ð1Þwhich is also a form of the continuity equation, from

which the pressure is derived.

• Conservation of momentum

qo~uot

þ qð~u � rÞ~u ¼ �rP þ lr2~uþ q~gbðT � T1Þ

ð2Þwhich is often called the Navier–Stokes equation if

the viscosity is constant and the flow is laminar.

• Conservation of energy

qcpoTot

þ qcp~u � rT ¼ r � krT þ S ð3Þ

which is the thermal energy equation, from which the

convective heat transfer coefficients are determined.

The above are basically the convection transfer

equations. For conjugate heat transfer, we need to obtain

a balance of the energy equation, to work out the con-

tribution of power from conduction and radiation sep-

arately, and to add to the energy equation. A fully

conservative exchange factor calculation for all surfaces

and sub-divided segments on these surfaces has to be

performed for radiation. The same is for conduction so

that the heat transfer has to be accounted for from cell to

cell in the three directions. Radiation and conduction are

another two non-linear phenomena and the heat transfer

from them can be described in simplified forms as [8]:

qrad ¼ eArðT 4s � T 4

surÞ ð4Þ

qcond ¼ kADTL

ð5Þ

The finite volume method is used to analyze three-

dimensional geometry and to discretize the conversation

equations by sub-division of the domain of integration

into a set of non-overlapping, contiguous finite volumes

over each of which the conservation equations are ex-

pressed in algebraic forms. The algebraic equations then

replace the differential equations from which they orig-

inated. They are solved in a computational grid by

iteration.

In the modeling, radiation is always applied. The

view factors are automatically calculated between all

pairs of surfaces for which radiation has been activated.

If the path between the surfaces is blocked, then the view

factor is calculated based on the proportion of radiation

that can pass. Airflows are set to laminar flows in nat-

ural convection, and turbulent flows in forced convec-

tion. There are three turbulence-modeling options in

Flotherm. The Automatic Algebraic turbulence model

calculates the turbulent viscosity based on the distance

from the wall and the local speed, and there are no user

settings. It is recommended for most problems, and is

also chosen in this study.

2.2. Package and materials

The illustration of the package is shown in Fig. 1

where a laser driver IC sits on a heat spreader and a laser

array is mounted parallel to the IC about 1.3 mm away

from their edges for wire bonding. The substrate in this

case is a 3-layer flex with an opening where the IC sits,

and is laminated to the heat spreader. The driver IC

dimensions are 4.15· 2.025· 0.535 mm, and the laser

array dimensions are 3.2 · 0.4 · 0.26 mm. The materials

properties are shown in Table 1.

2.3. Modeling and simulation

The solution procedures are based on CFD tech-

niques for the numerical simulation of fluid flow, heat

transfer and related processes such as radiation occur-

ring within and around optoelectronic modules in

Flotherm. The general governing equations are conser-

vation of mass, momentum and energy for convective

heat transfer [13,14]. For conjugate heat transfer, we

need to obtain a balance of the energy equation, to work

out the contribution of power from conduction and

radiation separately, and to add to the energy equation.

A fully conservative exchange factor calculation for all

surfaces and sub-divided segments on these surfaces has

to be performed for radiation. The same is for conduc-

tion so that the heat transfer has to be accounted for

from cell to cell in the three directions [15].

The finite volume method is used to analyze three-

dimensional geometry and to discretize the conservation

equations by sub-division of the domain of integration

into a set of non-overlapping, contiguous finite volumes

Fig. 1. SNAP12 MSA 2.5 Gbps transmitter package.

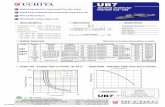

Table 1

Materials properties of the package and the heat sink

Components Materials Dimensions (mm3) Thermal conductivity (W/mK)

Driver IC Si 4.2· 2 · 0.5 117.5–0.42 (T � 100)a

Laser array (OC) GaAs (gallium arsenide) 3.2· 0.4 · 0.3 50

Substrate (flex) Polyimide 15· 8.8 · 0.2 0.25

Heat spreader Al 15· 8.8 · 0.5 201

Substrate adhesive Rogers/R-Flex 15· 8.8 · 0.025 3.5

IC adhesive Silver epoxy 0.5· 0.3 · 0.025 3

Encapsulant Liquid, transparent 15· 8.8 · 0.8 0.68

Filled adhesive Thermalbond 4951 15· 8.8 · 1.5 1.34

VCSEL thermal pad Copper 3.95· 0.65· 0.2 395

a T is the circulating temperature in degree Centigrade.

758 P.Z.F. Shi et al. / Microelectronics Reliability 44 (2004) 755–769

over each of which the conservation equations are ex-

pressed in algebraic forms. The algebraic equations then

replace the differential equations from which they orig-

inated. They are solved in a computational grid by

iteration [15]. One example of the CFD modeling and

the grid cell distribution is shown in Fig. 2.

The computer used in the simulation is Intel P4 CPU

1.8 GHz/RAM 1 GB. The CPU time for the normal grid

size is approximately 2.5 h for the heat sink design, 2.2 h

for the thermal path improvement, and 2.7–3.5 h for the

detailed module validation. The CPU time for the fine

grid cell size is about 1.5–2 times that of the normal grid

cell size.

2.4. Heat sink design

An optimal heat sink design is necessary to dissipate

heat efficiently from the optoelectronic module. Based

on the optical module structure, different heat sinks were

designed as shown in Fig. 3. Heat sink 1, HS1 in Fig.

3(a), is in a form of fins that is parallel to the die sub-

strate, while HS2 in Fig. 3(b) is perpendicular to the die

substrate with fine fins. HS3 in Fig. 3(c) is in the same

form as HS2 but it has fewer fins. HS4 in Fig. 3(d) is a

pin fin heat sink in the same orientation as HS3. HS5 in

Fig. 3(e) is a solid block heat sink and HS6 in Fig. 3(f) is

the case where a heat sink is not applied.

2.5. Thermal path optimization

It is important to regulate or isolate the temperature

of the laser array due to the sensitivity of optical module

performance to temperature change. Thermal perfor-

mance is directly related to not only the surface area but

also the heat transfer path. A cavity in the substrate and

a VCSEL thermal pad (as shown in Table 1) to replace

the cavity were designed to improve the thermal path as

shown in Fig. 4, where no cavity means that the VCSEL

array sits on the substrate directly, cavity means that the

laser array sits on the thermal pad in the cavity in the

substrate on the top of a heat spreader.

For high-speed applications, the smaller the separa-

tion between the laser array and the driver IC, the

smaller the wire bonding length, and the better the

electrical performance due to the smaller inductance

Fig. 2. Grid cell distribution of one module (full module).

Fig. 3. Different heat sink designs: (a) HS1––fins parallel to package, (b) HS2––fine fins, (c) HS3––moderate fins, (d) HS4––pin fin heat

sink, (e) HS5––block heat sink and (f) HS6––no heat sink.

P.Z.F. Shi et al. / Microelectronics Reliability 44 (2004) 755–769 759

introduced by the wire. However the smaller separation

is likely to create a higher thermal crosstalk between

them. To study the trade-off between the thermal per-

formance and the electrical performance of the module,

different separation distances (1.3, 2.5, and 5.0 mm) are

simulated to evaluate the thermal performance. The

power is 1.2 W on the driver IC and 24 mW on the laser

array. In addition, the effect of forced-air convection

along the X -axis was also considered in the simulation

for applications with potentially higher power.

Fig. 4. Cavity in the substrate and separation between the laser array and driver IC: (a) cavity, separation¼ 1.3 mm, (b) separa-

tion¼ 2.5 mm and (c) separation¼ 5.0 mm.

760 P.Z.F. Shi et al. / Microelectronics Reliability 44 (2004) 755–769

2.6. Detailed module modeling and thermal characteriza-

tion

After the heat sink design and optimization of the

heat sink and the temperature regulations, three full

modules of the optical transmitter were modeled and

simulated. The three types of the modules are Module 1

without housing, Module 2 with housing, and Module

Fig. 5. Illustration of the three modules

Fig. 6. Thermal meas

3 or full module with a pin fin heat sink as shown in

Fig. 5.

The test vehicle includes a 2.5 Gbps transmitter core

module and a heat sink or and a fan. The thermal

environments for the evaluation include two types of

ambient temperature, 25 �C and 50 �C, and both natural

and forced-air convections. In the forced-air convection,

the flow rates are 1 and 3 m/s. During the measurement

and the thermocouple locations.

urement setup.

P.Z.F. Shi et al. / Microelectronics Reliability 44 (2004) 755–769 761

a voltage control power supply was used and the voltage

was fixed at 3.3 V. A wind tunnel was used to control the

ambient temperature and the airflow rate.

Thermocouples were used for the module case tem-

perature measurement while a thermistor was built in

the module close to the VCSEL array to measure the

laser array junction temperature. For Module 1, the

thermocouple was fixed at the center of the two pin holes

on the back of the package. For Module 2, it was at

about 1 mm up from the center of the intersection line of

horizontal and the vertical planes of the housing. For

Module 3, it was at the top center between the heat sink

and the housing, as shown in Fig. 5.

Fig. 7. Temperature distributions for different heat sink designs:

The experimental setup includes the optical trans-

mitter test vehicle, wind tunnel, and thermal analyzer, as

shown in Fig. 6.

3. Results and discussion

3.1. Heat sink design and optimization

Six types of heat sinks were designed and simulated.

The grid cell size is about 600k to 650k. The ambient

temperature was assumed to be 25 �C. The power dis-

sipated by the driver IC is 1.2 W, and 24 mW by the

(a) HS1, (b) HS2, (c) HS3, (d) HS4, (e) HS5 and (f) HS6.

Table 2

Simulation matrix for thermal path improvement and separa-

tion evaluation

Run

No.

Airflow

rate (m/s)

IC power

(W)

Cavity and

thermal pad

Separation

distance (mm)

101 0 1.2 No 1.3

102 0 2.0 No 1.3

762 P.Z.F. Shi et al. / Microelectronics Reliability 44 (2004) 755–769

VCSEL array. The temperature distributions are shown

in Fig. 7. All the visualization contours are plotted

within 20 �C from their highest temperature for com-

parison purpose except for HS6 where the plot is done in

its total temperature range. It can be seen that HS4 is the

best design and can remove the heat more efficiently as

the temperature is gradually changed from the heat

source to the pin tip end. HS1 is not efficient as the heat

is more concentrated at the first few fins and the end part

of the heat sink dissipates little heat, which could be

removed. For HS2, HS3 and HS5, the temperature is

still quite high at the tip of the heat sinks and there is

still more heat to be dissipated although HS3 is better

than HS2 for heat removal. HS6 could not even dissi-

pate heat away from its sources. The densely packed fins

of HS2 prevent effective convection within the narrow

boundary layers of the still air. On the other hand it is

expected that under forced-air convection, a high fin

density is better because the high flow rate air overcomes

the pressure resistance between the fins and removes

heat freely from the pins. However high flow rate forced-

air convection is not expected due to the application

constraints.

The simulation results are shown in Fig. 8. The

junction temperatures of the driver IC and the laser

array are very close and the difference is less than 1 �C.The junction–ambient thermal resistances of the driver

IC are about 52–58.5 �C/W except for the one without a

heat sink. In conclusion, HS4 gives the best thermal

performance in terms of both the driver IC and the

VCSEL junction temperatures, and reduces the junction

temperature of the driver IC to 87.5 �C from 141.7 �C or

by 38% as compared to HS6 where there is no heat sink.

3.2. Thermal path optimization

The thermal path improvement was done by design-

ing a cavity within the substrate and replacing the cavity

with a thermal pad. The VCSEL array sits on the ther-

0

20

40

60

80

100

120

140

hsd1 hsd2 hsd3 hsd4 hsd5 hsd6

Heat Sink Design

Th

erm

al P

erfo

rman

ce

IC junction temperature (°C)

IC thermal resistance (°C/W)

VCSEL junction temperature (°C)

Fig. 8. Simulation results under natural convection for heat

sink design.

mal pad and the substrate is on the top of a heat

spreader. The effect of wire bonding length on the

module thermal performance was evaluated by using

different separation distances. In the modeling, the heat

sink was not used, which means HS6 was used as shown

in Fig. 3, and the substrate length was increased from

8.83 to 11.33 mm to suit for different wire bonding

lengths. Simulations were done under three volume flow

rates (0 m/s or natural convection, 1 and 3 m/s), two

different power dissipation levels (1.2 and 2.0 W), with

and without a cavity and a thermal pad, and three

separation distances (1.3, 2.5 and 5.0 mm) between the

laser diode array and the driver IC. The laser array was

powered at 24 mW.

The simulation matrix is shown in Table 2. The

visualizations of the temperature distributions over the

package are shown in Fig. 9. It can be seen approxi-

mately that the cavity and thermal pad, the separation

and the air flow all affect the temperature distributions

of the package. The simulation results of the junction

temperatures were plotted in Figs. 10 and 11. Fig. 10

shows that the difference in the IC junction temperatures

with and without the cavity and thermal pad is very

small, at about 0.05 �C, while that in the VCSEL array

junction temperatures is much higher, 0.85 �C if the

power on the IC is 1.2 W and 0.21 �C if the power on the

IC is 2.0 W. The reason for this could be that there is not

enough volume for the high power of 2.0 W. However

the real power applied to the driver IC is about the 1.2

W. It can also be seen that the effect of airflow rates on

111 1 1.2 No 1.3

112 1 2.0 No 1.3

131 3 1.2 No 1.3

132 3 2.0 No 1.3

201 0 1.2 Yes 1.3

202 0 2.0 Yes 1.3

211 1 1.2 Yes 1.3

212 1 2.0 Yes 1.3

231 3 1.2 Yes 1.3

232 3 2.0 Yes 1.3

401 0 1.2 No 2.5

402 0 2.0 No 2.5

411 1 1.2 No 2.5

412 1 2.0 No 2.5

501 0 1.2 No 5.0

502 0 2.0 No 5.0

511 1 1.2 No 5.0

512 1 2.0 No 5.0

Fig. 9. Visualizations of the temperature distributions over the package under different cavities, separations and a fan: (a) Run

No. 101, (b) Run No. 132, (c) Run No. 201, (d) Run No. 232, (e) Run No. 401, (f) Run No. 412, (g) Run No. 501 and (h) Run

No. 512.

P.Z.F. Shi et al. / Microelectronics Reliability 44 (2004) 755–769 763

50

70

90

110

130

150

170

190

210

0m/s, 1.2W 0m/s, 2W 1m/s, 1.2W 1m/s, 2W 3m/s,1.2W 3m/s, 2W

Thermal conditions

Jun

ctio

n t

emp

erat

ure

(˚C

)

IC, no cavity

IC, cavity

VCSEL, no cavity

VCSEL, cavity

Fig. 10. Junction temperature under different cavities.

70

90

110

130

150

170

190

210

0m/s, 1.2W 0m/s, 2W 1m/s, 1.2W 1m/s, 2W

Thermal conditions

Jun

ctio

n t

emp

erat

ure

(˚C

)

1.3mm, IC

2.5mm, IC

5.0mm, IC

1.3mm, VCSEL

2.5mm, VCSEL

5.0mm, VCSEL

Fig. 11. Junction temperature under different separations.

30

40

50

60

70

80

90

100

0m/s, 1.2W 0m/s, 2W 1m/s, 1.2W 3m/s, 1.2W 3m/s, 2W

Thermal conditions

IC t

her

mal

ch

arac

teri

stic

par

amet

er

(˚C

/W)

1.3mm1.3mm, cavity2.5mm5.0mm

1m/s, 2W

Fig. 12. Junction–ambient thermal resistances of the driver IC.

764 P.Z.F. Shi et al. / Microelectronics Reliability 44 (2004) 755–769

the junction temperatures is insignificant. Therefore the

effect of the cavity and thermal pad on the temperature

drop of the VCSEL array is significant.

Fig. 11 shows that the effect of the separations be-

tween the VCSEL array and the driver IC on the dif-

ference of the IC junction temperatures among the

different separations is negligible, which is 0.005 �C be-

tween 1.3 and 2.5 mm and 0.05 �C between 1.3 and 5.0

mm. However the effect for the VCSEL array is signifi-

cant. It can be seen that the power on the driver IC

affects the temperature difference of the VCSEL junction

among different separations. The VCSEL junction tem-

perature differences are 0.31 and 0.55 �C between 1.3

and 2.5 mm, and 0.80 and 1.39 �C between 1.3 and 5.0

mm for the power acting on the driver IC of 1.2 and 2.0

W respectively. The airflow rate also affects the tem-

perature difference of the VCSEL junction but such

difference is less than 0.3 �C. On average the difference of

the VCSEL junction temperatures is 0.43 �C between the

separations of 1.3 and 2.5 mm, and 1.09 �C between

those of 1.3 and 5.0 mm.

The IC junction–ambient thermal resistances or

thermal characteristic parameters are plotted in Fig. 12,

in which the IC junction–ambient thermal resistance or

thermal characteristic parameter is calculated by divid-

ing the temperature difference between the junction and

the ambient by the power acting on the driver IC. It can

be found that both the cavity and thermal pad in the

substrate and the separation between the VCSEL array

and the driver IC have little effect on the IC thermal

resistance, and the difference is less than 0.1 �C/W.

However the airflow rate affects the thermal resistance

significantly. The IC thermal resistance is about 90.31,

50.29 and 32.51 �C/W under the airflow rate of 0 m/s

(natural convection), 1 and 3 m/s respectively. In addi-

tion, the power level also affects the IC thermal resis-

tance. The thermal resistance difference is 5.14, 0.49 and

0.24 �C/W under the airflow rate of 0, 1 and 3 m/s for the

power applied to the driver IC of 1.2 and 2.0 W

respectively. Therefore there is a thermal crosstalk be-

tween the VCSEL array and the driver IC because the

power affects the thermal resistance significantly espe-

cially under the natural convection condition, and it can

be seen that there is a direct shift of the VCSEL’s tem-

perature distribution due to the power loss of the driver

IC on the same substrate.

3.3. Detailed module simulation and experimental valida-

tion

The thermal performance evaluation of three typical

detailed transmitter modules was carried out through

both numerical simulation and experimental verifica-

tion. Fig. 13 shows the simulation temperature and

velocity distributions of the three modules, and Fig. 14

shows the simulation results. Table 3 shows the simu-

lation and experimental matrix and results, in which the

power includes those acting on both the VCSEL array

that was fixed at 24 mW and the driver IC. The low and

high ambient temperatures could not be fixed because

the environmental temperature was changing and the

power was also changing with the ambient temperature

Fig. 13. (a) Visualizations of temperature and velocity for the detailed modules: (a1) Module 1––without housing, (a2) Temperature-

No. 10, (a3) Temperature-No. 13 and (a4) Velocity-No. 13. (b) Visualizations of temperature and velocity for the detailed modules:

(b1) Module 2––with housing, (b2) Temperature-No. 20, (b3) Temperature-No. 23 and (b4) Velocity-No. 23. (c) Visualizations of

temperature and velocity for the detailed modules: (c1) Module 3-full module, (c2) Temperature-No. 30, (c3) Temperature-No. 33 and

(c4) Velocity-No. 33.

P.Z.F. Shi et al. / Microelectronics Reliability 44 (2004) 755–769 765

0

10

20

30

40

50

60

70

80

10 11 13 13ha 20 21 23 23ha 30 31 33 33haWithout housing With housing Full module

Tem

pera

ture

(°C

)

CaseVCSELIC Driver

Fig. 14. Simulation results of the detailed modules.

Fig. 13 (continued)

766 P.Z.F. Shi et al. / Microelectronics Reliability 44 (2004) 755–769

and the airflow rate in the wind tunnel. Fig. 15 shows the

comparison between the experimental and simulation

results. As the thermistor was built in close to the

VCSEL array, the measurement junction is approxi-

mately the VCSEL junction. Based on the case temper-

ature measurement, the module cases in the simulation

were defined as the Z-Low of heat spreader for Module

1, the Z-Low of house 5 for Module 2, and the Y-High

of house 5 for Module 3 in the modeling in Flotherm.

The simulation thermal resistance of the driver IC

junction to ambient was calculated based on the tem-

perature difference divided by the power acting on the

IC, and plotted in Fig. 16.

Fig. 13 shows that the airflow speed is from 0 to 4.2

m/s for Module 1, 0 to 4.5 m/s for Module 2, and 0 to 4.6

m/s for Module 3 for an average airflow rate of 3 m/s.

Figs. 13 and 14 show that the junction temperature of

the driver IC is higher than these of the case and the

VCSEL junction in all the three modules. Temperatures

in Module 1 are the highest and those in Module 3 are

the lowest due to the housing and heat sink effects. Fig.

13 also shows that Module 3 has higher surface areas for

better forced-air convection as the pin fin heat sink can

increase the effective convection area. Fig. 15 shows that

in all the three modules, the simulation and experimental

results of the case and VCSEL junction temperatures are

comparable. The maximum correlation errors are 13.3%

and 15.4% for the case and the VCSEL respectively. The

average correlation error is 5.92% as a whole and

4.6% and 7.3% for the case and VCSEL separately. The

possible reasons for the case temperature discrepancy

are the location of the thermocouple assembly, and the

thermocouple accuracy. For the VCSEL junction tem-

perature difference, the reasons could be the location of

the thermistor that is close to the VCSEL but not inside

the VCSEL, and the calibration of the thermistor which

was done within the temperature range from 20 to 60 �C

0

5

10

15

20

25

30

35

40

0 0.5 1 1.5 2 2.5 3Airflow Rate (m/s)

Ther

mal

Res

ista

nce

(°C

/W) Module 1

Module 2Module 3

Fig. 16. IC junction–ambient thermal resistance of detailed

modules from simulation.

Table 3

Experimental and simulation matrix for the detailed modules

Run No. Ambient temperature (�C) Air flow velocity (m/s) Power (W)

Module 1––without housing

10 24.2 0 1.10

11 24.0 1 1.07

13 24.2 3 1.06

13 ha 49.0 3 1.09

Module 2––with housing

20 23.2 0 1.16

21 24.4 1 1.19

23 24.4 3 1.18

23 ha 48.5 3 1.16

Module 3––full module with housing and heat sink

30 24.4 0 0.904

31 24.1 1 0.898

33 24.2 3 0.891

33 ha 49.1 3 0.917

0

10

20

30

40

50

60

70

80

10 11 13 13ha 20 21 23 23ha 30 31 33 33ha

Without housing With housing Full module

Tem

per

atu

re (

˚C)

Case_exp

Case_sim

VCSEL junction_exp

VCSEL junction_sim

Fig. 15. Comparison between experimental and simulation

results.

P.Z.F. Shi et al. / Microelectronics Reliability 44 (2004) 755–769 767

due to constraints and therefore any extrapolation may

cause errors. Other potential reasons for the discrepancy

are the module modeling simplification, grid cell size

(which is discussed later), the materials properties, and

the numerical models for turbulence problems. Due to

the limited number of the test vehicles available there

was only one sample for each of the three physical

modules, and the physical differences of each modules

may cause the variation too.

Fig. 16 show that the thermal performance of Mod-

ule 3 is the best while that of Module 1 is worst. The IC

junction–ambient thermal resistance is 36.6 �C/W under

natural convection (the highest) and 7.34 �C/W under an

airflow rate of 3 m/s for Module 3. Module 3 with a heat

sink can reduce the thermal resistance by 47% under

natural convection and by 61% under an airflow rate of

1 m/s from Module 1, and by 14.5% under an airflow

rate of 1 m/s from Module 2. However there is no

improvement of the thermal performance under natural

convection condition between Module 3 and Module 2,

which means that an additional heat sink to the housing

is not necessary under natural convection condition.

For Module 1, the case temperature is higher than 70

�C under natural convection condition. A forced con-

vection is required to keep the case temperature below

70 �C. For the high ambient temperature at about 50 �C,forced-air convection is still needed to keep the case

temperature below 70 �C. Under natural convection and

normal ambient temperature, the case temperatures are

well below 70 �C for Modules 2 and 3, which is an un-

cooled cooling solution.

3.4. Grid cell size sensitivity study

To make sure that simulation results are independent

of grid cell sizes and as one way to validate the simu-

lation results, the following simulation was performed

under normal ambient temperature at 25 �C. Nor-

Table 4

Simulation results for grid cell size sensitivity study

Run No.� Grid cell size Junction temperature (�C)

Diver IC VCSEL

Normal Fine Normal Fine Difference (%) Normal Fine Difference (%)

Hsd4 646,282 1,306,008 87.54 87.26 )0.32 88.15 87.74 )0.47Hsd6 608,475 1,075,620 141.74 141.04 )0.50 141.56 140.73 )0.59

101 681,450 997,120 136.41 136.1 )0.23 136.13 135.82 )0.23132 89.8 90.13 0.37 87.04 87.38 0.39

10 755,568 1,146,600 63.54 63.58 0.06 62.49 62.58 0.14

13 46.00 46.91 1.94 44.95 45.89 2.05

20 1,029,420 1,608,576 44.99 45.96 2.11 43.32 44.25 2.10

23 34.52 34.90 1.09 32.80 33.23 1.29

30 1,095,984 1,817,312 41.40 42.13 1.73 40.12 40.86 1.81

33 30.55 30.86 1.00 29.27 29.56 0.98

*Hsd4 and Hsd6 are for the heat sink design, 101 and 132 are for the thermal path improvement, and the rest are for the detailed

module simulation and experimental validation.

20

40

60

80

100

120

140

160

hsd 4 hsd 6 101 132 10 13 20 23 30 33Run No.

Junc

tion

Tem

pera

ture

(°C

)

IC_normalIC_fineVCSEL-normalVCSEL-fine

Fig. 17. Simulation results from grid cell size sensitivity study.

768 P.Z.F. Shi et al. / Microelectronics Reliability 44 (2004) 755–769

mal grid cell size and fine grid cell size were used for

comparison purpose. The simulation results are shown

in Table 4, and plotted in Fig. 17. The average and

maximum correlation differences are 0.47% and 0.59%,

0.30% and 0.39%, and 1.36% and 2.11% (Run No. 20)

for the modules without housing and with housing and

the full module. As a whole the differences of the sim-

ulation results due to the fine grid cells and the normal

grid cells are very small, and it is reasonably correct to

use the normal grid cell sizes for the simulation.

4. Conclusions

From the above thermal simulation and experimental

validation, it can be concluded:

• Heat sink designs were optimized for the optical

transmitter application. The optimized heat sink de-

sign with a pin fin heat sink (HS4) is able to reduce

the driver IC junction temperature by 38% compared

to the case (HS6) if there was no heat sink under the

natural convection condition.

• The thermal path improvement through designing a

cavity and a thermal pad that were integrated into

the substrate together with the VCSEL array, and

varying the separation distances between the VCSEL

array and the driver IC was simulated and evaluated.

It has been found that the VCSEL junction tempera-

ture can be reduced by 0.9 �C with the cavity and

thermal pad, and by 1.4 �C with the separation.

• The detailed module simulation and experimental

validation show that the simulation and experimental

results of the case and VCSEL junction temperatures

are comparable. The average and the maximum cor-

relation errors are 6% and 15% respectively for all the

three transmitter modules. The potential reasons for

the discrepancy were analyzed.

• A natural convection cooling solution to maintain

the case temperature below 70 �C without using a

fan through thermal design and optimization of heat

sink and heat transfer path has been achieved.

Acknowledgements

This work is conducted by the Broadband Packaging

Consortium in Singapore, comprising 3M, Ansoft Cor-

poration, DSO, E2O Communications, Finisar Corpo-

ration, SIMTech, Gul Technologies, HiDEC, Micron

Semiconductor Asia and Venture Manufacturing. The

authors would also like to acknowledge financial sup-

port from A*STAR (Agency for Science, Technology

and Research, Singapore).

P.Z.F. Shi et al. / Microelectronics Reliability 44 (2004) 755–769 769

References

[1] Rahman BMA, Lepkowski SP. Thermal modeling of

vertical-cavity surface-emitting lasers using the finite-

element method. IEE Proc Optoelectron 1995;142(2).

[2] Chen X, Zhu J. Thermal performance study for a MCMS

infrared transmitter by FEM. In: Proceedings of

IPACK’01, Hawaii, July 2001.

[3] Lee YC, Swirhum SE. Thermal management of VCSEL-

based optoelectronic modules. IEEE Trans Compon Pack

Manufact Technol B 1996;19(3).

[4] Shi ZF, Lu ACW, Tan E, Tan R. Numerical study and

experimental validation of the thermal performance for a

parallel channel optical module. In: InterPack2003-35141,

July 2003.

[5] Kasap SO. Optoelectronics and photonics: principles and

practices. Prentice Hall; 2001.

[6] Tummala RR. Fundamentals of optoelectronics, fun-

damentals of microsystems packaging. McGraw-Hill;

2001.

[7] Cheng J, Dutta NK. Vertical-cavity surface-emitting lasers:

technology and applications. Gordon and Breach Science

Publishers; 2000.

[8] Shi ZF, Lu ACW, Tan YM, Ang KH, Tan R, Tan E. Heat

sink design optimization for optical transponders. In: The

35th International Symposium on Microelectronics, IM-

APS, Denver, September 2002.

[9] Siva Gurrum et al. Thermal issues in next generation

integrated circuits. In: InerPack2003-35309, July 2003.

[10] Zhang Y et al. Thin film coolers for localized temperature

control in optoelectronic integrated circuits. In: ECTC’03,

May 2003. p. 312–6.

[11] SNAP12 MSA Specifications––12 channel pluggable opti-

cal module. Appendix to SNAP12 Multi-Source Agree-

ment, Rev. 1.1, May 2002.

[12] NEMI Technology Roadmaps, Design Technologies––

Thermal Management, December 2002.

[13] Mills AF. Basic heat and mass transfer, 2/E. Prentice Hall;

1999. p. 428–39.

[14] Incropera FP, DeWitt DP. Fundamentals of heat and mass

transfer, 5/E. John Wiley Sons Inc; 2002. p. 3–13, 954–62.

[15] Gauch�e P. Linearized superposition using CFD for ther-

mal and power characterization of electronic equipment

with significant thermal radiation and natural convection.

In: The 35th International Symposium on Microelectron-

ics, IMAPS Denver, September 2002.