Job 7 Sabilal

-

Upload

handokoprabowo -

Category

Documents

-

view

230 -

download

0

description

Transcript of Job 7 Sabilal

PERCOBAAN VII : COUNTER MAJU TAK SEREMPAK (UP COUNTER ASINKRON)

I. TUJUAN Mahasiswa dapat merakit rangkaina counter maju tak serempak Mahasiswa dapat mengamati cara kerja counter maju tak serempak Mahasiswa dapat membuat table kbenaran untuk rangkaian tipe ini Mahasiswa dapat menggambarkan timing diagram counter maju tak

serempak untuk bentuk-bentuk gelombang yang ditampilkan pada osiloskop

II. PERALATAN DAN KOMPONEN Rangkaian catu daya 1 Set Oscilloscope dual trace 1 Buah Rangkaian MVB dengan ic 555 1 Buah IC7473/7476 2 Buah Resistor R: 100 ohm 4 Buah Led 4 Buah Switch push button 2 Buah Mini project board 1 Buah Multimeter 1 Buah Banana 6 Buah Probe 2 Buah Jumper-kit

III. TEORI DASARCounter adalah rangkaian digital yang dibuat dari beberapa FF dan

gerbang-gerbang logika untuk mendapatkan angka-angka biner pulsa pulsa yang diberikan pada input-inputnya. Counter dibagi dalam dua bagian utama yaitu sebagai counter asinkron (tak serempak) dan counter sinkron (serempak).

Counter asinkron atau ripple counter adalah counter yang paling sering digunakan. Counter ini dapat dibentuk dari JK-FF. Clock untuk setiap FF didapat dari output FF sebelumnya FF pertama yag didapat dari pulsa pembangkit.

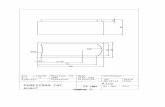

Counter maju asinkron seperti gambar 22(a) dimana terdapat 4 JK-FF yang dihubungkan secara kaskade (bertingkat). Counter ini menhitung dalam biner dari 010 (0000) ke 1510 (1111). Output Q dari setiap FF memberikan satu nilai tempat dalam angka biner. Input clock yang dihubungakan pada FFA adalah sebagai input counter, setiap pulsa clock yang akan dating akan menghadirkan bit-bit biner pada masing-masng output FF. Output Q FA mempunyai nilai tempat 1s,output Q FFB mempunyai nilai tempat 2s,output Q FFC mempunyai nilai tempat 4s dan terakhir output Q FFD mempunyai nilai tempat 8s dari counter.

Cara kerja counter maju asinkron ini dapat dilihat dengan gambar, timing, diagram dan table kebenaran seperti gambar 22(a) ,22(b) dan tabel kebenara hitungannya seperti gambar 22(c)

IV. PROSEDUR PRAKTIKUM1. Buatlah rangkaian seperti gambar 23

2. Gunakan switch push button sebagai input clock couner dan periksa bahwa fungsi flip flop adalah benar

3. Kerjakan rangkaian dan isilah tabel kebenaran nya

4. Gantilah switch push button dengan rangkaian pembangkit pulsa TTL secara otomatis dan gambarka timing diagramnya dengan melihat input clock