Copy of USART I

Transcript of Copy of USART I

USART I/O Data Register – UDR

Register UDR yaitu register yang berfungsi sebagai buffer atau tempat sementara dimana buffer

data ini dipakai untuk data yang akan di kirim dan data yang akan di terima. Untuk transmitter, buffernya

hanya dapat dipakai saat flag UDRE dalam kondisi high (1) di dalam register UCSRA. Pada register

UDR mempunyai 1 byte yaitu 8 bit dimana terdapat UDR read dan write. Read yaitu RXB untuk receiver

dan write yaitu TXB untuk transmitter. Untuk TXB dan RXB mempunyai alamat yang sama. Untuk RXB

sebagai buffer/tempat data di terima sedangkan TXB untuk buffer/tempat data yang akan dikirim ke

receiver.

USART Control and Status Register A – UCSRA

Register UCSRA adalah register yang terdiri dari 8 bit dimana register ini berfungsi untuk

mengendalikan mode komunikasi dan juga dapat membaca status yang sedang terjadi di USART. Pada bit

0 adalah MPCM yaitu multi processor communication mode yang memiliki fungsi untuk mengaktifkan

mode multi prosesor communication, sehingga saat mode ini di aktifkan maka ketika data yang di terima

oleh USART dimana data tersebut tidak terdapat informasi alamatnya maka data tersebut akan di abaikan.

Bit 1 yaitu U2X adalah double the USART transmission speed, yaitu memiliki fungsi untuk melibatkan

boudrate yang akan digunakan, ini beroperasi pada mode operasi asinkron. Pada bit 2 yaitu PE adalah

Parity Error dimama bit ini dapat mendeteksi terjadinya error parity jika terjadi error maka flag akan di

set 1 sedangkan jika tidak terjadi error maka flag akan di clearkan 0. Pada bit 3 yaitu DOR adalah data

overrun dimana fungsiny adalah untuk mendeteksi jika data menjadi overrun atau data tersebut tumpang

tindih jika terjadi demikian flag akan bernilai 1 tetapi jika tidak terjadi overrun maka flag akan bernilai 0.

Bit 4 yaitu frame error fungsinya sebagai penanda jika data yang di terima terjadi error jadi sebagai

contoh saat data di terima kemudian pada stop bit bernilai 0 maka flag frame error akan bernilai 1, flag

akan bernilai 0 saat stop bit tersebut bernilai 1.

Pada bit 5 adalah UDRE yaitu USART data register Empty dimana sebagai penanda isi dari UDR

jadi saat flag ini bernilai 1 maka UDR siap menerima data baru artinya UDR pada keadaan kosong

sebalikny jika flag bernilai 0 maka di dalam UDR masih terdapat data sehingga belum siap menerima

data baru. Bit 6 yaitu TXC adalah USART Transmit Complete adalah penanda dimana akan bernilai 1

saat data yang di transmit telah keluar kemudian flag ini akan 0 saat data belum di kirimkan. TXC dapat

dipakai sebagai interupsi TX complet sehingga ketika bernilai 1 dan akan bernilai 0 secara otomatis

besamaan dapat mengeksekusi interrupt vector yang bersangkutan dan flag ini dapat dipakai sebagai

pooling data. Dan yang terakhir bit ke 7 adalah RXC atau USART receive complete dimana flag ini akan

bernilai 1 saat data berhasil masuk ke dalam UDR tetapi belum di baca, setelah di baca maka flag ini akan

0 dan UDR akan menjadi kosong. RXC dapat dipakai sebagai interupsi RX complet sehingga ketika

bernilai 1 dan akan bernilai 0 secara otomatis besamaan dapat mengeksekusi interrupt vector yang

bersangkutan dan flag ini dapat dipakai sebagai pooling data

USART Control and Status Register B – UCSRB

Register UCSRB terdiri dari 8 bit dimana berfungsi untuk mengaktifkan register-register seperti

receiver enable, transmitter enable, Data register empty enable. Bedanya dengan UCSRA dimana pada

UCSRA bit bit nya berisikan flag-flag sedangkan pada register ini untuk mengaktifkan dan

menonaktifkan. Pada bit 0 yaitu TXB8 adalah transmit data bit 8 yang berfungsi saat memakai format

data 9-bit sehingga bit ini harus ditulis terlebih dahulu sebelum kita menulis ke UDR. Bit 1 yaitu RXB8

atau receive data bit 8 adalah berfungsi saat memakai format data 9-bit sehingga bit ini harus ditulis

terlebih dahulu sebelum kita membaca UDR. Bit 2 yaitu UCSZ2 / character size digunakan untuk

memilih format character size yang akan digunakan. Bit 3 TXEN / transmitter enable berfungsi untuk

mengaktifkan pin TX dimana bernilai 1 untuk mengaktifkannya dan bernilai 0 untuk

menonaktifkan.tetapi saat kita mengaktifkan pin TX maka pin tersebut tidak dapat digunakan sebagai I/O.

bit 4 RXEN/ Receiver Enable berfungsi untuk mengaktifkan pin RX dimana bernilai 1 untuk

mengaktifkannya dan bernilai 0 untuk menonaktifkan.tetapi saat kita mengaktifkan pin RX maka pin

tersebut tidak dapat digunakan sebagai I/O. bit 5 UDRIE / USART Data register empty Interrupt enable

mempunyai fungsi untuk mengaktifkan interrupt data register empty dimana 1 untuk mengaktifkan dan 0

untuk menonaktifkan saat data yang kita tulis ke UDR tersebut telah di kirim maka UDR akan kosong

sehingga dapat membangkitkan interrupt data register empty tersebut. Bit 6 TXCIE / TX complete

interrupt enable yang mempunyai fungsi mengaktifkan interrupt TX complete dimana 1 untuk

mengaktifkan dan 0 untuk menonaktifkan saat data di kirim oleh UDR maka flag TXC akan bernilai 1

pada UCSRA sehingga dapat membangkitkan interruput TX complete tersebut. Bit 7 RXCIE / RX

complete interrupt enable yang mempunyai fungsi mengaktifkan interrupt RX complete dimana 1 untuk

mengaktifkan dan 0 untuk menonaktifkan saat data diterima UDR maka flag RXC akan bernilai 1 pada

UCSRA sehingga dapat membangkitkan interruput RX complete tersebut.

USART Control and Status Register C – UCSRC

UCSRC atau USART control and status register ini beada dalam lokasi yang sama dengan register

UBRRH sehingga kedua register ini tidak dapat di pakai secara bersama-sama karena di atur oleh URSEL

pada bit 7. Dimana bit 7 atau URSEL Register select berfungsi untuk memilih antara UBRRH atau

UCSRC dimana jika di berikan 0 (diclear) maka membaca UBRRH sebaliknya jika di set (1) maka akan

mengakses register UCSRC. Bit berikutnya adalah UMSEL (USART mode select) bit 6 ini

menenentukan mode select yang di gunakan yaitu jika clear maka modenya adalah asynchronous dan jika

di set maka modeny adalah synchronous operation.

Bit 5 dan bit 4 adalah UPM1 dan UPM0 yaitu parity mode sehingga dapat memilih partiy mode yang

cocok untuk dipakai. Jika bit ini di pakai maka secara otomatis akan membangkitkan parity pada setiap

data-data yang dikirimkan dan juga dapat memeriksa data yang di terima. Jika bit parity tidak cocok/

tidak diperoleh maka pada register UCSRA tepatnya pada bit parity error akan di set. Untuk UPM1-

UPM0 : 0-0 maka mode parity tidak dipakai untuk 0-1 mode partiy akan di siapkan. Untuk 1-0 mode

parity di pakai dan bersifat parity genap sedangkan 1-1 mode parity di pakai dan bersifat parity ganjil.

USBS atau stopbit select pada bit 3 ini digunakan untuk dimana berfungsi untuk menentukan jumlah

stop bit yang akan digunakan jika USBS bernilai 0 maka stopbit yang di gunakan sebesar 1 bit sedangkan

bernilai 1 maka stop bit yang digunakan sebesar 2 bit. Stopbit ini dipakai untuk memvaliditas suatu data

tersebut.

Bit 2 dan bit 1 adalah UCSZ1 dan UCSZ0 dimana UCSZ2 berada pada register UCSRB pada bit 2.

Fungsiny sama yaitu memilih character size yang akan di pakai yang hendak di kirim atau di terima

sehingga besarnya ditentukan oleh character size tersebut. Untuk menentukan character size maka dapat

di lihat pada table UCSZ bits setting di bawah ini.

UCPOL berada pada bit 0 UCPOL adalah clock polarity yang digunakan hanya pada mode

synkronus. Dimana pada bit ini berkaitan dengan adanya perubahan sample input, output data dan XCK

atau clock synkronus. Dapat di lihat UCPOl bit setting nya jika UCPOl bernilai 0 maka output TxD saat

rising XCK edge sebaliknya input RxD saat falling XCK edge. Dan jika UCPOL 1 maka output TxD saat

falling XCK edge dan intput RxD saat rising XCK edge

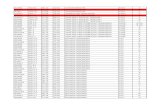

USART Baud Rate Registers – UBRRL and UBRRH

Register ini digunakan untuk menentukan baud rate yang akan di pakai. Register ini terdapat UBRRH

dan UBRRL tetapi untuk dapat mengakses UBRRH maka harus di setting pada register UCSRC.

Bit 15 yaitu register selecet URSEL digunakan untuk menentukan register mana yang akan di akses

jika ingin baru di clear jika ingin menggunakan rehister UBRRH. Pada bit 14 sampai bit 12 tidak di

gunakan tetapi harus di clear jika ingin menuliskan ke UBRRH. Pada bit 11 sampai 0 adalah USART

baud rate register yaitu UBRR jadi register ini memiliki besar 12 bit dimana dari bit tersebut dapat

mengatur baud rate yang akan di gunakan. Untuk lebih jelasnya dapat melihat table baudrate di bawah ini.

Sebagai contoh jika kita menggunakan frekuensi osilator 4.0000 Mhz maka kita menginginkan

baudratenya sebesar 9600 jadi memiliki kemungkinan error sangatlah kecil hanya 0.2% . dimana kita

harus mengeset U2X=1 oleh karena itu jika di lihat UBRR nya dalah 47 maka kita dapat menggunakan

UBRRL = 47; sehingga baudrate yang di gunakan 9600 dengan error 0.2% pada frekuensi osilator 4 Mhz

Operasi ADC memerlukan Vref dan clock Fad. Untuk tegangan pada pin Aref harus di

bawah dari tegngan Avcc. Jika kita menggunakan port A sebagai ADC maka port A tidak dapat

digunakan sebagai I/O. hasil dari ADC dapat kita hitung dengan menggunakan rumus. Jika kita

menggunakan resolusi sebesar 10 bit maka rumusny adalah ADC = (Vin/Vref)x1024 sedangkan

untuk resolusi sevesar 8 bit rumusnya adalah ADC = (Vin/Vref)x256 sebagai contoh jika kita

menggunakan ADC dengan resolusi 8 bit dimana V in=2500mV dan Vref = 2560mV maka hasil

ADC ny adalah (2500mV/2560mV)x256=250 atau 0xFA sehingga hasil digitalny adalah 0xFA.

Resolusi pada AVR adalah hal yang menentukan seberapa bagus sampling yang di dapat

dimana menunjukkan banyaknya nilai diskrit yang di dapat dari tegangan tertentu dimana di

nyatakan dalam bit resolusi juga di katakan rentang sinyal analog yang di dapat ddan dinyatakan

ke dalam bilangan digital sehingga besar resolusi tersebut sebanding dengan 2^n dimana n

tersebut adalah jumlah bit output digital maka semakin besar jumlah bit tersebut maka resolusi

akan semakin bagus juga. Sebagai contoh jika kita mempunay Vref : 5v dan menggunakan

resolusi 8 bit maka 8 bit di sini = 2^8 = 256 jadi dimulai dari 0 sampai 255 jika tegangan yang di

dapat 5v maka hasil ADC adalah 255 jika tegangan melebihi Vref maka ADC akan menghitung

hasilnya adalah 255. Beberapa register yang harus di setting terlebih dahulu sebelum

menggunakan ADC dimana register tersebut adalah ADMUX / ADC Multiplexer selection

register, ADCSRA / ADC control and status register A, ADCL & ADCH / The ADC data

register, dan SFIOR/Special function IO register. Vref atau tengangan refrensi merupakan

tegangan refrensi ADC yang berfungsi sebagai tegangan acuan terhadap sinyal dimana jika

resolusi 8 bit memiliki nilai berkisar 0-255 dan Vref : 2v jika pada pin ADC di berikan tegangan

3v maka hasil ADC tersebut adalah 255 karena acuan tegangan nya adalah 2v. tegangan refrensi

juga di sebut batas maksimal level tegangan input analog atau dengan kata lain Vref merupakan

tegangan yang akan menjadi acuan dalam melakukan convert dari analog ke digital.

ADMUX / ADC Multiplexer selection register

Pada bit 7 dan 6 adalah REFS1 dan REFS0 yaitu refrence selection bit dimana

mempunyai fungsi untuk memilih Vref yang akan di gunakan. Jika REFS1 – REFS0 = 0-0 maka

AREF, internal Vref di matikan jadi pin AREF sebagai Vref sehingga kita harus memberikan

tegangan pada pin ini. Jika 0-1 maka AVcc dengan kapastior ekternal di pin AREF jadi pin aref

akan di hubungkan pada pin avcc dengan syarat harus menggunakan kapasitor pada pin avcc

agar menstabilkan tegangan, 1-0 adalah reserved dan 1-1 Vref internal sebesar 2.56v dengan

menggunakan kapasitor eksternal pada pin AREF kado aref ,emggumalam tegangan internal

yaitu 2.56v tetapi dengan syarat harus mendambahkan kapasitor pada pin aref agar dapat di baca

tegangannya adalah 2.56v. Kemudian bit ke 5 adalah ADLAR/ADC left adjust result dimana

akan membaca ny dari kiri ke atas dari hasil ADC. Untuk bit 4 sampai 0 adalah MUX4:0 /

analog channel selection bit dimana bit ini berfungsi untuk menentukan jalur input untuk ADC.

ADCSRA / ADC control and status register A

Bit 7 yaitu ADEN/ADC enable berfungsi untuk mengaktifkan ADC dimana ADEN=1

untuk enable dan sebaliknya ADEN=0 untuk disable. Bit 6 yaitu ADSC/ADC start conversion

digunakan untuk melakukan pengambilan data dimana jika selesai mengambil data akan bernilai

0 dan saat ambil data maka bernilai 1. Di dalam mode konversi tunggal maka start conversion

ADC hanya terjadi sekali konversi. Sebaliknya pada free running start conversion di lakukan

secara kontinyu. bit berikutnya yaitu bit 5 adalah ADFR/ ADC free running select bit ini

berfungsi untuk memilih mode dari ADC. Jika di set maka akan menggunakan mode free

running dimana akan selalu di sample dan di update secara kontinyu. dan jika di clear maka

mode free running tidak di gunakan dan kembali ke single conversion. Bit 4 ADIF/ADC

interrupt flag akan bernilai 1 saat konbersi ADC complete. Dan clear jika eksekusi interrupt

ADC conversion complete. Untuk bit 3 ADIE/ADC interrupt enable digunakan untuk

mengaktifkan interrupt ADC conversion complete untuk mengaktifkannya cukup di set jika

menonaktifkan cukup di clear. Bit 2 sampai 0 adalah bit yang digunakan untuk menentukan

besar prescaler atau faktor pembagi frekuensi CPU yang di gunakan untuk clock ADC karena

clock pada ATmega8535 sangat inggi hingga 16Mhz sehingga di perlukannya prescaler untuk

menurunkan frekuensi tersebut yang akan di pakai oleh ADC. Dimana presclaer ini terbuat dari

beberapa flip-flop saja sehingga bit ini dinamakan ADPS2:0 / ADC prescaler select bits.

ADCL & ADCH / The ADC data register

ADCL dan ADCH merupakan kumpulan bit-bit yang berisi hasil dari konversi dari

analog ke digital tersebut. Saat ADCL di baca maka ADC data register tidak dapat di update

sampai ADCH tersebut di baca sehingga jika hasilnya left adjusted dan tidak lebih dari 8 bit

maka cukup untuk membaca ADCH saja. Jadi jika kita ingin menggunakan resolusi 8 bit

disarankan untuk menggunakan ADLAR = 1 dan menggunakan ADCH saja. Jadi bit ADLAR

juga memperngaruhi ADC data register mana yang akan kita gunakan.

SFIOR/Special function IO register

Pada bit 7 sampai 5 yaitu ADTS2:0 /ADC autotriger dimana jika ADATE di ADCSRA di

tulis 1 . tetapi jika ADATE tersebut di clear (0) maka ADTS2:0 ditdak memiliki effect

apa=apa.bit ini juga dapat mengatur trigger dari operasi ADC. Dimana mode-mode trigger

tersebut dapat dilihat pada table di atas. conversion akan di trigger risig edge maka akan terjadi

interrupt flag. Pad abit 4 tidak di gunakan dan selalu bernilai 0. Pada bit 3 sampai 0 bit ini tidak

di gunakan dalam proses ADC.

Mode-mode operasi pada ADC di AVR terdapat 2 mode operasi yaitu mode operasi

single conversion dan mode operasi free running. Mode operasi single converision adalah mode

dimana pembacaan sample tengan input yanf di dapat hanyalah sekali. Sehingga jika pada mode

operasi ini kita dapat melakukan sample sesuai dengan kenginnan kita. Jika kita ingin

melakukan sample lagi maka kita dapat mengkonversi tengangan input untuk setiap saat yang di

butuhkan. Mode operasi single conversion ini diaktifkan dengan cara clear kan bit ADFR di

dalam register ADCSRA sehingga ADFR = 0. Mode ini beroperasi saat bit ADSC di berikan

nilai 1 dan tetap bernilai 1 hingga konversi tersebut complete. Setelah complete bit ADSC akan

secara otomatis bernilai 0. Mode operasi free running yaitu mode dimana melakukan konversi

secara kontinyu yaitu secara terus menerus dimana ADC akan membaca sample tegangan input

yang di dapat kemudan di konversi dan hasilnya tersebut di masukkan ke ADCH:ADCL. saat

kita membaca ADC pada saat ADC tersebut sedang mengkonversi maka yang di baca adalah

hasil ADC yang terakhir di baca oleh ADC tersebut. Untuk mode operasi free running

mengaktidkan nya dengan cara bit ADFT di berikan nilai 1 dalam register ADCSRA. Sehingga

mode ini bekerja secara independen dari flag interrupt ADC makusnya adalah walaupun ADIF

bernilai 1 ataupun 0 maka mode ini tetap berjalan.