Register Siso

-

Upload

lita-sry-angraeni -

Category

Documents

-

view

64 -

download

3

Transcript of Register Siso

Tugas Pengantar Arsitektur Komputer

PAPER

RANGKAIAN REGISTER

SISO, SIPO, PIPO, DAN PISO

DISUSUN OLEH :

NAMA : LITA SRI ANGRAENI

NIM : 1229041047

KELAS : PTIK 03

PRODI PENDIDIKAN TEKNIK INFORMATIKA DAN KOMPUTER

JURUSAN PENDIDIKAN TEKNIK ELEKTRO

UNIVERSITAS NEGERI MAKASSAR

2012/2013

1. REGISTER SISO (Serial Input Serial Output)

Saat sinyal clock diberikan pertama kali, data dari Si masuk ke flipflop

A, pada saat clock kedua, data dari flipflop A masuk ke flipflop B,

demikian seterusnya, sampai keluar ke So. Jadi pada register SISO

untuk membaca data pertama kali dibutuhkan jumlah clock yang sama

banyak dengan jumlah flipflop yang ada pada register (dalam hal ini

adalah empat).

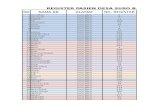

Tabel Kebenaran (Misal masuknya 1101)

Clock ke Word in Q1 Q2 Q3 Q4

0 0 0 0 0 0

1 1 1 0 0 0

2 0 0 1 0 0

3 1 1 0 1 0

4 1 1 1 0 1

2. REGISTER SIPO (Serial Input Paralel Output)

Masukan-masukan data secara deret akan dikeluarkan oleh D-

FF setelah masukan denyut lonceng dari 0 ke 1. Keluaran data

/informasi serial akan dapat dibaca secara paralel setelah diberikan

satu komando (Read Out). Bila dijalan masuk Read Out diberi logik 0,

maka semua keluaran AND adalah 0 dan bila Read Out diberi logik 1,

maka pintu-pintu AND menghubung langsungkan sinyal-sinyal yang

ada di Q masing-masing flip-flop.

Contoh: Bila masukan data 1101

TABEL KEBENARAN

Read Out Clock Input Q1 Q2 Q3 Q4 A B C D

0 0 0 0 0 0 0 0 0 0 0

0 1 1 1 0 0 0 0 0 0 0

0 2 1 1 1 0 0 0 0 0 0

0 3 0 0 1 1 0 0 0 0 0

0 4 1 1 0 1 1 0 0 0 0

1 1 0 1 1 1 0 1 1

3. REGISTER PIPO (Paralel Input dan Paralel Output)

A, B, C, dan D adalah sinyal masukan. Saat clock (pemicu) diaktifkan

(Logika 1), maka data yang ada akan dikeluarkan secara bersama-

sama ke Q3, Q2, Q1, dan Q0. Saat clock kembali tidak dipicu (Logika

0), maka apapun masukannya, keluaran Q akan tetap.

TABEL KEBENARAN:

Clock D1 D2 D3 D4 QD QC QB QA

0 1 1 0 1 0 0 0 0

1 1 1 0 1 1 1 0 1

2 1 0 0 1 1 0 0 1

3 0 0 0 1 0 0 0 1

4. REGISTER PISO (Paralel Input Serial Output)

Cara Kerja Jenis Shift Register Geser PISO :

Mula-mula jalan masuk Data Load = 0, maka semua pintu NAND mengeluarkan 1,

sehingga jalan masuk set dan rerset semuanya 1 berarti bahwa jalan masuk set dan

reset tidak berpengaruh. Jika Data Load = 1, maka semua input paralel akan

dilewatkan oleh NAND. Misal jalan masuk A=1, maka pintu NAND 1 mengeluarkan 0

adapun pintu NAND 2 mengeluarkan 1. Dengan demikian flip -flop diset sehingga

menjadi Q=1. Karena flip-flop yang lainpun dihubungkan dengan cara yang sama,

maka mereka juga mengoper informasi pada saat Data Load diberi logik 1. Setelah

informasi berada didalam register, Data Load diberi logik 0. Informasi akan dapat

dikeluarkan dari register dengan cara memasukkan denyut lonceng, denyut-demi denyut

keluar deret/seri. Untuk keperluan ini jalan masuk D dihubungkan kepada keluaran Q.

Ada juga register yang dapat digunakan sebagai Shift register SISO maupun PIPO

dengan bantuan suatu control

TABEL KEBENARAN:

Data IC Preset Reset

0 1 1 0

1 1 0 1

0 0 1 1

1 0 1 1