UNIVERSIDAD TÉCNICA DE AMBATO

-

Upload

independent -

Category

Documents

-

view

0 -

download

0

Transcript of UNIVERSIDAD TÉCNICA DE AMBATO

UNIVERSIDAD TÉCNICA DE AMBATO

Facultad de Ingeniería en Sistemas,

Electrónica e Industrial

PROYECTO ACADEMICO DE FIN DE SEMESTRE

Título: Sumador-Restador de 4 bits en

código BCD.

Carrera: Ingeniería en Electrónica y

Comunicaciones

Área académica: Física y

Electrónica

Línea de Investigación: Sistemas

Electrónicos

Ciclo Académico y paralelo: Cuarto

semestre “B”

UNIVERSIDAD TÉCNICA DE AMBATOFACULTAD DE INGENIERÍA EN SISTEMAS, ELECTRÓNICA E INDUSTRIAL

PERÍODO ACADÉMICO: SEPTIEMBREO/2013 – FEBRERO/2014

Alumnos participantes:Balarezo Constante

Juan Carlos

Campaña Escalante John

Wagner

Jiménez Zúñiga Deisy

Carolina

Vivanco Correa Jessica

Andrea

Modulo y Docente: Electrónica Digital I

Ing. Patricio Córdova.

1. INFORME DEL PROYECTO

1.1. Titulo

Sumado-Restador de 4 bits en código BCD.

1.2. Objetivos

Implementar un sumador-restador de dos números

binarios de 4 bits.

Verificar el correcto funcionamiento del esquema

del circuito desarrollado para la presente

práctica.

UNIVERSIDAD TÉCNICA DE AMBATOFACULTAD DE INGENIERÍA EN SISTEMAS, ELECTRÓNICA E INDUSTRIAL

PERÍODO ACADÉMICO: SEPTIEMBREO/2013 – FEBRERO/2014

Determinar los elementos electrónicos necesarios

para el montaje de dicha práctica en una

protoboard.

1.3. Resumen

El presente proyecto tiene como finalidad implementar un

sumador-restador de 4 bits en código BCD, su función

principal es sumar o restar dos números de acuerdo a la

señal de control establecida por un multiplexor 4:1,

dichos números serán ingresados mediante un dip switch

de 8 entradas. Estas operaciones se realizaran mediante

un sumador paralelo y el complemento a1 para el caso de

la resta.

El resultado de las operaciones mencionadas

anteriormente será visualizado a través de tres display

de 7 segmentos ánodo común, los mismos están

establecidos en el orden siguiente: el primero mostrará

el signo de la operación y en los dos restantes el valor

obtenido.

1.4. Palabras clave: sumador, restador, bits, BCD.

1.5. Introducción

Desde el principio de la revolución tecnológica la

Electrónica Digital ha sido una de las ramas

fundamentales para el desarrollo de la sociedad

tecnológica ya que la mayoría de la información detrás

de nuestros dispositivos electrónicos se encuentra

codificada por ceros y unos, dos estados fundamentales

en la Electrónica.

UNIVERSIDAD TÉCNICA DE AMBATOFACULTAD DE INGENIERÍA EN SISTEMAS, ELECTRÓNICA E INDUSTRIAL

PERÍODO ACADÉMICO: SEPTIEMBREO/2013 – FEBRERO/2014

Es por tal motivo que el presente proyecto se

desarrolló con el objetivo de dar una guía práctica y

sencilla para la elaboración de un sumador-restador en

BCD, con sus respectivos esquemas, listados de

materiales y metodología empleada para la implementación

y verificación del funcionamiento de nuestro circuito.

Así los estudiantes optimizaran su aprendizaje, llevando

los conocimientos de la teoría a la práctica.

1.6. Materiales y Metodología

1.6..1. Marco Teórico

Según: MANO, M. Morris, 2003, Diseño Digital,

Tercera Edición, Pearson Educación, México, pág.:

118-126

Circuitos Combinacionales: Un circuito

combinacional consta de compuertas lógicas cuyas

salidas en cualquier momento están determinadas en

forma directa por la combinación presente de las

entradas sin tomar en cuenta las entradas previas.

Un circuito combinacional realiza una operación

especifica de procesamiento de información,

especificada por completo en forma lógica por un

conjunto de funciones booleanas.

Un circuito Combinacional consta de variables de

entrada, compuertas lógicas y variables de salida.

Las compuertas lógicas aceptan las señales de las

entradas y generan señales a las salidas. Este

proceso transforma la información binaria de los

datos dados de entrada en los datos requeridos de

UNIVERSIDAD TÉCNICA DE AMBATOFACULTAD DE INGENIERÍA EN SISTEMAS, ELECTRÓNICA E INDUSTRIAL

PERÍODO ACADÉMICO: SEPTIEMBREO/2013 – FEBRERO/2014

salida. En forma obvia, tanto los datos de entrada

y salida se representan por señales binarias, estos

es, existen en dos valores posibles, uno representa

la lógica 1 y el otro la lógica 0.En la figura 4-1,

se muestra un diagrama d bloques de un circuito.

Las n variables de entrada provienen de una fuente

externa; las m variables de salida van a un destino

externo.

Según: MANO, M. Morris, 2003, Diseño Digital,

Tercera Edición, Pearson Educación, México,

Capítulo 4, pág.: 160-165.

Sumador binario paralelo: La suma de dos números

binarios de n bits, A y B pueden generarse de dos

maneras: en serie o en paralelo. Un sumador paralelo

binario es una función digital que produce una suma

aritmética de dos números binarios en paralelo.

Este consiste en sumadores completos conectados en

cascada con la salida de arrastre de un sumador

completo conectado al arrastre de entrada del

siguiente sumador completo.

UNIVERSIDAD TÉCNICA DE AMBATOFACULTAD DE INGENIERÍA EN SISTEMAS, ELECTRÓNICA E INDUSTRIAL

PERÍODO ACADÉMICO: SEPTIEMBREO/2013 – FEBRERO/2014

La suma de dos números binarios en paralelo

implica que todos los bits de los sumandos están

disponibles para el cálculo al mismo tiempo. Como

en cualquier circuito combinacional, la señal

debe propagarse por las compuertas antes que la

suma de salida correcta esté disponible en los

terminales de salida. El tiempo de propagación

total es igual al retardo de propagación de una

compuerta típica multiplicando por el número de

niveles de compuertas en el circuito. El mayor

tiempo de propagación en un sumador paralelo es

el tiempo que se toma el bit de arrastre en

propagarse. Como cada bit de la salida de suma

depende del valor del arrastre de entrada, el

valor de S, en cualquier estado dado en el

sumador, estará en su valor final estable

solamente hasta que el bit de arrastre de entrada

a este estado se haya propagado.

UNIVERSIDAD TÉCNICA DE AMBATOFACULTAD DE INGENIERÍA EN SISTEMAS, ELECTRÓNICA E INDUSTRIAL

PERÍODO ACADÉMICO: SEPTIEMBREO/2013 – FEBRERO/2014

Recuperado de:

www.scribd.com/doc/43220345/Decodificador-7447

DECODIFICADOR: El decodificador integrado 7447 esun circuito lógico que convierte el código binariode entrada en formato BCD a niveles lógicos quepermiten activar un display de 7 segmentos en dondela posición de cada barra forma el númerodecodificado.

Muchas presentaciones numéricas en dispositivos devisualización utilizan una configuración de 7segmentos para formar los caracteres decimales de 0a 9 y algunas veces los caracteres hexadecimales deA a F. Cada segmento está hecho de un material queemite luz (Display) cuando pasa corriente a travésde él, los patrones de segmentos que sirven parapresentar los diversos dígitos.

El decodificador 7447 está diseñado para activarsegmentos específicos, aun de códigos de entradamayores que 1001 (9). La figura Nº 2 muestra lasrepresentaciones para los códigos desde 0000 hasta1111. Note que un código de entrada de 1111 borrarátodos los segmentos.

La codificación y la decodificación serán siempreoperaciones necesarias en sistemas digitales quetraten información, o en procesos industrialesdonde sea necesario suministrar datos o presentarresultados. En algunos sistemas cibernéticos o decontrol es posible prescindir de este tipo deoperaciones, siendo suficiente la aplicación deseñales digitales mediante transductores y aplicarlas salidas del circuito sobre elementos depotencia tales como lámparas, motores, etc.

Un decodificador es un circuito lógico queconvierte un código binario de entrada de N bits,

UNIVERSIDAD TÉCNICA DE AMBATOFACULTAD DE INGENIERÍA EN SISTEMAS, ELECTRÓNICA E INDUSTRIAL

PERÍODO ACADÉMICO: SEPTIEMBREO/2013 – FEBRERO/2014

en líneas de salida de manera tal, que cada una deestas líneas sólo sea activada para una posiblecombinación de entrada, la figura Nº1 muestra eldiagrama general del decodificador con N entradas y2N salidas.

Recuperado de:

http://es.scribd.com/doc/4918593/Multiplexor

MULTIPLEXOR 2:1.- Los multiplexores son circuitoscombinacionales que tienen varias entradas, unasola salida y varias líneas de selección. Sufuncionamiento podría asemejarse a un conmutador devarias posiciones que simularían las entradas y elterminal común, la salida; la conmutación serealizaría por medio de la línea de selección, detal modo que las señales presentes en las entradasaparecerán en la salida en el orden indicado por lalínea de selección; es decir, un multiplexorpermite el envío por una sola línea de los datospresentes en varias líneas.

Uso básico del multiplexor 74157

UNIVERSIDAD TÉCNICA DE AMBATOFACULTAD DE INGENIERÍA EN SISTEMAS, ELECTRÓNICA E INDUSTRIAL

PERÍODO ACADÉMICO: SEPTIEMBREO/2013 – FEBRERO/2014

Este circuito muestra cómo se utiliza unmultiplexor 74157 de forma simple, permite ingresarusando switch dos números de 4 bits, y seleccionarcon el

multiplexor cuál de los dos números se muestra enun display a la salida del multiplexor.

MULTIPLEXOR 4:1.- Contiene dos multiplexores consus cuatro entradas de datos y su salida cada uno.Tiene dos entradas de inhibición (STROBE 1G y 2G)activas a nivel bajo (0V) para cada multiplexor ydos entradas de selección (SELECT A y B) comunes alos cuatro multiplexores. El 74153 es un doblemultiplexor de cuatro canales, con dos bits de

UNIVERSIDAD TÉCNICA DE AMBATOFACULTAD DE INGENIERÍA EN SISTEMAS, ELECTRÓNICA E INDUSTRIAL

PERÍODO ACADÉMICO: SEPTIEMBREO/2013 – FEBRERO/2014

control para determinar el canal que sale, unaseñal de strobe para cada multiplexor.

Lo que deberías hacer es usar dos 74153 para tenerlos 16 canales de entrada, y hacer una lógicadigital con compuertas para que con 4 bits deentradas puedas controlar las 8 señales de controlde los 2 74513 (2 select inputs + 2 strobe por cada74153)

1.6..2.Materiales

Cables de Conexión

1 Circuito Integrado 7485

2 Compuertas 7404

2 Decodificadores 7447

1 Dip Switch 2 entradas

1 Dip Switch 8 entradas

3 Display 7 segmentos ánodo común

5 Multiplexores 74lLS153

1 Multiplexor 74LS157

Resistencias 220 Ω y 330 Ω

UNIVERSIDAD TÉCNICA DE AMBATOFACULTAD DE INGENIERÍA EN SISTEMAS, ELECTRÓNICA E INDUSTRIAL

PERÍODO ACADÉMICO: SEPTIEMBREO/2013 – FEBRERO/2014

2 Sumadores en paralelo 7483

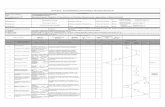

1.7. Procedimiento y Desarrollo

Partiendo del esquema realizado en el simulador Proteus,

previamente verificado su funcionamiento procedemos a

implementar el circuito sumador-restador en la

protoboard.

Sacamos las entradas del dip switch hacia el 7485 que

compara si A es mayor que B para obtener una de dos

señales de control que utilizaremos para el multiplexor

74LS153. La otra señal se obtiene del dip switch de 2

entradas y así tenemos:

Si es 0 se realiza la suma.

Si es 1 se realiza la resta.

También realizará el complemento a1 ya sea al número A o

al número B.

Finalmente tenemos un decodificador (74LS47) que cumple

con la función de decodificar los bits recibidos del

sumador paralelo y mostrarlo en el display de 7

segmentos. En el caso del signo no utilizamos el

decodificador simplemente recibirá las señales del

multiplexor 74153 y se mostrará en el display.

1.8. Resultados y Discusión

Se obtuvo en la práctica el funcionamiento de un

sumador-restador de 4 bits que realiza tanto la suma

como la resta, estas dos operaciones son reguladas

UNIVERSIDAD TÉCNICA DE AMBATOFACULTAD DE INGENIERÍA EN SISTEMAS, ELECTRÓNICA E INDUSTRIAL

PERÍODO ACADÉMICO: SEPTIEMBREO/2013 – FEBRERO/2014

mediante la señal de control de un multiplexor 2:1, en

el caso de la resta cuando el resultado es negativo se

mostrara el número y el signo se mostrará en el display.

1.9. Conclusiones

Se verificó que el sumador-restador cumple con el

esquema simulado en Proteus.

Se logró comprobar la teoría de multiplexores y

compuertas lógicas con circuitos implementados en

la práctica.

Se comprobó el correcto funcionamiento del esquema

realizado.

1.10. Bibliografía

Morris Mano M., (2003), Diseño Digital, (Tercera

Edición), México: Pearson Educación S. A.

Documentos de Internet:

www.scribd.com/doc/43220345/Decodificador-7447

http://es.scribd.com/doc/4918593/Multiplexor

1.11. Fotografías y Esquemas

UNIVERSIDAD TÉCNICA DE AMBATOFACULTAD DE INGENIERÍA EN SISTEMAS, ELECTRÓNICA E INDUSTRIAL

PERÍODO ACADÉMICO: SEPTIEMBREO/2013 – FEBRERO/2014

UNIVERSIDAD TÉCNICA DE AMBATOFACULTAD DE INGENIERÍA EN SISTEMAS, ELECTRÓNICA E INDUSTRIAL

PERÍODO ACADÉMICO: SEPTIEMBREO/2013 – FEBRERO/2014