Limits of nano-gate fabrication

Transcript of Limits of nano-gate fabrication

Limits of Nano-Gate Fabrication DAVID R. ALLEE, ALEC N. BROERS, AND R. FABIAN W. PEASE

This paper reviews the limits of nanometer scale gate electrode (nano-gate) fabrication. The technology to fabricate nano-gates has become increasingly important in recent years as the scaling limits of conventional electronic devices and the quantum effects of novel devices are investigated. Consistant with the technology used to fabricate virtually all of the smallest devices to date, the emphasis is on the resolution limits of electron beam lithography and associated ultrahigh resolution resists. Recent results of di- rectly patterning Si02 with nanometer scale resolution by e-beam exposure through a sacrificial layer are also presented. Finally, because the high resistance normally associated with nanometer scale electrodes seriously limits the performance of high frequency devices, various techniques to reduce the gate resistance are compared.

I. INTRODUCTION There has been a great deal of interest in recent years

in ultrasmall electronic devices both to investigate the scaling limits of conventional devices and various quan- tum interference effects upon which future generations of electronic switches might be based. The central feature of many of these devices is nanometer scale (~100 nm linewidth) gate electrodes. Several laboratories have fabri- cated 111-V field effect transistors (FET’s) with nano-gates to improve high frequency performance [l], [2] and or to study electron transport [3], [4]. We (at Stanford University) have fabricated metal semiconductor field effect transistors (MESFET’s) with gate lengths down to 65 nm (51, [6] and are currently (at Cambridge University) involved in a consortia to fabricate and study pseudomorphic modulation doped field effect transistors (MODFET’s) with gate lengths down to 20 nm. Several laboratories have also observed lateral quantum interference effects using various combina- tions of nano-gates in place of a single gate in a MODFET structure [7]-[13]. In this paper, the limits of nano-gate fabrication will be reviewed.

Nanometer scale electrodes incorporated in devices have been fabricated almost exclusively with electron beam lithography. There are several other promising lithographic technologies in various stages of development including

Manuscript received August 7, 1990; revised December 13, 1990. D. R. Allee and A. N. Broers are with the Department of Engineering,

R. F. W. Pease is with the Department of Electrical Engineering, Stan-

IEEE Log Number 9143322.

Cambridge University, Cambridge, U.K.

dord University, Stanford, CA 943054055,

focused ion beam [14], scanning X-ray [15], and scanning tunneling lithography [16]. Of these, only scanning tun- neling lithography is thought to have an ultimate resolution equal to or greater than electron beam lithography [17], [18] but several alignment and registration problems remain to be solved before devices can be fabricated. As of now, the limits of nano-gate fabrication are the limits of electron beam lithography, and we will begin with the physics of beam formation and beam substrate interactions followed by the resolution limits of various resists including our recently obtained results on the direct nanometer scale pat- terning of SiOz. Finally, since gate resistance in nanometer scale electrodes degrades the high frequency performance of FET’s, various techniques to reduce the gate resistance are compared.

11. PHYSICS OF BEAM FORMATION An electron beam lithography column (Fig. 1) consists

of a source of electrons and a series of magnetic lenses that demagnify either a crossover or a virtual image of the source to form the electron probe. The physical limit of probe formation is one of the fundamental limits of nano- gate fabrication. The principle characteristic of an electron source is its brightness or the current it emits per unit area into a unit solid angle. The brightness relation is

where J , is the peak current density at the virtual source or crossover, q is the charge on an electron, 4 is the beam potential, Icg is Boltzmann’s constant, and T is the temperature of the source. Note that q is negative for electrons. The importance of brightness is that it determines the maximum current density one can achieve at the image plane. Assuming that the thermal energy of the electron is much less than the accelerating potential, and that semi- angle of convergence, a, at the image plane is small, the current density at the target, Ji, is given as [19]:

Heated tungsten filaments have a brightness around 2.0 x lo5 A/(cm2 sr) whereas a lanthanum hexaboride

0018-9219/91/0800-1093$01.00 0 1991 IEEE

PROCEEDINGS OF THE IEEE, VOL. 79, NO. 8, AUGUST 1991 1093

’ I I TRAVERSE PUMPING )

SYSTEM

11 Fikz:s MECHANICAL

PMT

L I ,

I ELECTRON BEAM

(b )

Fig. 1. (a) A schematic drawing of the Stanford high resolution electron beam lithography column. Three magnetic lenses demagnify the crossover from the tungsten filament thermionic emitter. The scanning coils deflect the beam writing the pattern on the sample. (b) A schematic of the single bore objective lens gap and sample stage. Silicon photodetectors mounted on the tip of the upper polepiece detect backscattered electrons from the sample allowing registration and focusing.

thermionic emitter has a higher brightness around 3.0 x lo6 A/(cm2 sr) assuming a beam potential of 40 kV. Field emission sources have a very high brightness of about lo9 A/(cm2 sr) but require a very high vacuum for proper operation. Recently, thermally assisted field emitters have been developed that have properties in between the thermionic and field emitters [20].

A magnetic lens is a suitably shaped toroid of high permeability material with a single gap. Current in the lens windings drives magnetic flux through the magnetic

circuit. Fringing fields at the gap extend in to the axis focusing the electron beam. The focusing of electrons with a magnetic lens is analogous to the focusing of light with refracting surfaces; first order focusing can be described by principal planes, nodal points, and focal lengths. In fact, both Snell’s law and the paraxial ray equation which define the first order focusing properties of light and electron optical systems can be derived from Fermat’s principle if the electron optical index of refraction is defined to be the electron’s canonical momentum. Deviations from first order

1094 PROCEEDINGS OF THE IEEE, VOL. 19, NO. 8, AUGUST 1991

focusing can be described in terms of geometric aberra- tions, chromatic aberrations, and diffraction. The principle difference is that for light optics, refracting surfaces can be arbitrarily shaped whereas for electron optics, the focusing fields must be solutions of the Laplace equation.

The paraxial ray equation describes first order focusing of electrons, possibly relativistic, by a magnetic lens [21]:

4* = d( 1 - 2 4 ) (3)

r is the particle radius as a function of axial position z . B, and 4 are the magnetic flux density and electrostatic potential on axis; q/mo is the charge to mass ratio of the particle and c is the speed of light. The primes indicate derivatives with respect to 2. For a magnetic lens, the electrostatic potential, 4, is constant along the axis and is equal to the beam potential. This equation is valid for particles whose trajectories are sufficiently close to the axis; the fact that this equation is a linear second order differential equation assures ideal imaging.

Diffraction which usually limits the resolution of light optical systems is much smaller in a magnetic lens because the deBroglie wavelength of an electron is typically five orders of magnitude smaller than a visible photon. A 100 kV electron has a relativistically corrected wavelength of 0.0037 nm. The minimum diameter of the blurred spot due to diffraction is proportional to the electron wavelength and inversely proportional to the convergence angle:

0.6X

1.226 A=----

d d = - cy

m X is in nanometers, cr in radians, and 4* in volts.

The paraxial ray equation does not describe the tra- jectories of electrons that are not paraxial, that is nearly on axis. The blurring and distortion of the image by electrons not sufficiently close to axis can be characterized by the geometrical aberrations of the lens. These aberrations can be categorized by their dependence on convergence angle, a, and radial position at the image plane; the five types of aberrations are spherical aberration, coma, field curvature, astigmatism, and distortion. Because of the severe restriction that the focusing fields be solutions of the Laplace equation, a must be kept small, typically about 10 mrad, to minimize these aberrations. The third order aberrations are usually limiting and therefore particularly important for a magnetic lens.

Just as light with a spread in wavelengths results in a blurred image through the chromatic aberrations of a lens, electrons with a spread in energy about the beam potential also result in a blurred image. The spread in beam energy is due to the thermal energy the particles have when they are emitted from the source and due to random energy exchanging collisions between particles

after emission. Furthermore, any ripple in the lens current results in additional chromatic blurring of the image.

The aberrations that are proportional to the radial position in the image plane are known as deflection aberrations, and can be made insignificant by writing the nanometer scale patterns close to the axis. Spherical aberration and axial chromatic aberration are not proportional to radial position at the image plane and therefore do not disappear on axis. Furthermore Scherzer's theorem [22] states that spherical aberration can never be negative for an axially symmetric lens in which the fields are static, continuous, and free of space charge. This theorem implies that, unlike light optics, lenses with positive spherical aberration cannot be placed in series with lenses with negative spherical aberration to achieve a lens system with net zero spherical aberration. For these reasons, spherical and axial chromatic aberration are typically the most serious aberrations for nanometer scale patterning. The minimum diameter of the blurred spot or disc of least confusion for spherical and chromatic aberration are proportional to a3 and a, respectively:

(7)

C, and C, are the spherical and axial chromatic aberration coefficients and are functions of lens excitation and lens geometry; 64 is the spread in beam energy in electron volts. For a well designed lens, Liebmann [23] showed that these aberration coefficients are approximately equal to the focal length of the lens.

The final contribution to the beam diameter is the gauss- ian spot, the spot size necessary, neglecting aberrations, to contain a given beam current, It,, for a specific source brightness. The gaussian spot size is

The probe diameter is usually approximated by adding do in quadrature with the spherical, axial chromatic and diffraction least discs of confusion:

d i = d m . (9)

To achieve a small probe diameter, the spherical and axial chromatic discs of confusion must be reduced by reducing a. The semiangle of convergence cannot be re- duced indefinitely because of diffraction and the gaussian spot diameter which are inversely proportional to a. As an example illustrating the approximate limits of probe forma- tion, we will use data corresponding to our JEOL 4000EX transmission electron microscope that has been modified to pattern bulk substrates (Fig. 2). From the objective lens geometry and operating conditions, the spherical and chromatic aberration coefficients, C, and C,, are calculated to be 0.26 and 0.28 cm. Although most electron beam lithography is done at 50 kV or below, diffraction and the effect of the electron energy spread can be greatly reduced by increasing the beam voltage. Furthermore, the

ALLEE et al.: LIMITS OF NANO-GATE FABRICATION 1095

10" 10.) 10.' i n - ' .. alpha ( rad j

Fig. 2. The four contributions to the beam diameter, diffraction disc, spherical aberration disc, chromatic aberration disc and gauss- ian spot, are plotted versus the semiangle of convergence, alpha, for the modified TEM at Cambridge. The optimum convergence angle is about 5 mrad with a calculated overall beam diameter of 0.32 nm. Under these conditions, the probe diameter on our column has been measured to be 0.4 nm.

beam brightness is increased which decreases the gaussian spot diameter for a given beam current. These advantages are partly offset by a slightly increased focal length and aberration coefficients because the high energy electrons are more difficult to focus. Our column can be operated fiom 75 kV to 400 kV; for this calculation we will use our standard operating voltage of 350 kV. With a lanthanum boride source, the beam brightness was measured at the sample to be 2.5 x IO' A/(cm2 sr) [24]. Prior measure- ments for lanthanum boride cathodes at similar emitted currents indicate an electron energy spread of less than 3 eV [25]. The beam current will be set at 0.4 PA. With this data, the optimum convergence angle is 5 mrad. The gaussian spot, diffraction disc, spherical aberration disc, and chromatic aberration disc have diameters of 0.16 nm, 0.19 nm, 0.16 nm, and 0.12 nm, respectively. The over- all beam diameter is 0.32 nm. Under these conditions, the probe size on our column has been measured to be 0.4 nm [24].

The focal length and hence the spherical and chtomatic aberrations can not be reduced indefinitely by generating a higher magnetic field in the pole piece gap. If this were possible, the optimum convergence angle would increase and the minimum obtainable probe diameter would de- crease even further. The fundamental limit is the satu- ration flux density in the pole piece. For iron, this is approximately 1.8 T. This is the highest magnetic flux density that can be achieved in the pole piece gap. For a given beam voltage, this sets a limit on the shortest focal length possible and hence the lowest possible spherical and chromatic aberration coefficients. Reducing the beam voltage to reduce the focal length has the deleterious effects previously mentioned. Superconducting lenses can generate higher flux densities but have not proved practical because of the difficulty in maintaining the extremely tight mechanical tolerances in the presence of superconducting temperatures. [26].

111. BEAM SUBSTRATE INTERACTIONS AND EXPOSURE OF CONVENTIONAL RESIST

As a focused electron beam penetrates a solid substrate,

the electrons are elastically scattered through large angles by the atomic nuclei. Numerous small angle inelastic col- lisions gradually slow the primary electrons and generate low energy (several tens of eV) secondary electrons along the paths. Using a single scattering Monte Carlo program developed by David Joy [27] at the University of Tennessee, the trajectories of 50 primary electrons in Ge (or approxi- mately GaAs) are plotted in Fig. 3. The beam voltage for this example is 50 kV; the generation secondaries long the trajectories is not shown. Some of the primary electrons reemerge from the surface of the substrate several microns from the point of impact. These electrons are referred to as backscattered electrons.

For electron beam lithography, the surface of the sub- strate is coated with an electron sensitive material or resist. As the beam penetrates the resist, the beam is broadened or forward scattered. A Monte Carlo plot of the trajectories of 250 electrons (50 kV) as they penetrate a 100 nm resist film is shown in Fig. 4. The resist was approximated as a carbon film with a 1 gm/cm3 density, and an infinitely narrow incident beam was assumed. At the base of the resist 90% of the electrons are contained in a 6-nm diameter disc. Typically the resist is exposed both by forward scattered primary and associated secondary electrons in the incident beam and by backscattered primary and associated secondary electrons over a region extending several microns away. Very roughly, half of the expo- sure is due to the incident electrons and half due to the backscattered electrons. However, since the backscattered electrons are distributed over a relatively large region, the dose (C/cm2) is much lower. The exposure distribution is usually approximated with a proximity function, F'(T), that contains two Gaussian distributions corresponding to the forward (aj) and backscattered (cb) electrons [28]:

r is the distance from the incident beam center, IC is a normalizing constant and 77 is the ratio between the forward and backscattered exposures. For nanometer scale lithography, a better fit is obtained by adding a third exponential term [29].

The broadening or forward scattering of the beam as it penetrates the resist is one of the limits on the minimum feature size that can be defined in the resist. The forward scattering can be made negligible however by using a high beam voltage and or a thin resist. Again using a Monte Carlo model [27] approximating the resist as a carbon film with 1 gm/cm3 density, and assuming an infinitely narrow initial beam, the beam diameter at the base of the resist that contains 90% of the electrons is plotted as a function of resist thickness and beam voltage in Fig. 5. For a resist thickness 50 nm or less and beam voltages of 50 kV and up, the beam spread is less than 2 nm. Note that at 350 kV, the forward scattering is only 10 nm in 0.5 pm of resist.

The range of backscattered electrons increases with in- creasing beam voltage and is greater than 5 pm at 50 kV

1096 PROCEEDINGS OF THE IEEE, VOL. 79, NO. 8, AUGUST 1991

I I I

Fig. 3. from the Monte Carlo programs developed by David Joy [27]. The beam voltage is 50 kV.

A plot of the trajectories of 50 incident electrons in Ge (or equivalently GaAs) obtained

Fig. 4. A Monte Carlo plot [27] of the trajectories of 250 electrons (50 kV) penetrating an organic resist film 100-nm thick. The resist is approximated as a carbon film with a density of 1 gm/cm3. The forward scattering diameter at the base of the resist that contains 90% of the electrons is 6 nm.

100

75

50

25

0

4

+ 4

+

l0kV 5OkV IOokV 350kV

0 100 200 300 400 500 Resist Thickness (nm)

Fig. 5. A plot based on Monte Carlo simulations [27] of the forward scattering diameter versus the resist thickness as a function of beam voltage. The resist is again approximated as a carbon film with a density of 1 gm/cm3. Forward scattering can be made negligible with thin resists and or high beam voltages.

[29]. For an isolated feature, backscattered electrons do not affect the minimum feature size that can be defined in the resist. However, for dense structures that extend over a region equal to or greater than the backscatter range,

the image contrast is reduced. For equal lines and spaces and assuming equal incident electron and backscatter elec- tron exposures, elementary calculations indicate an image contrast of 0.5. If it is consistant with the device being fabricated, backscattered electrons can be eliminated by exposing a resist on a thin membrane.

For nanometer scale patterning, polymethylmethacrylate (PMMA) is the most widely used and the highest resolution conventional electron beam resist. As with most positive e-beam resists, exposure to electrops breaks the polymer chains enhancing the solubility in developer. Most all electrodes fabricated with PMMA use the liftoff process. After the PMMA is patterned, a layer of metal is evaporated over the sample. The metal adheres to the substrate in the patterned regions and the metal on the surface of the resist is removed by dissolving the resist in a solvent. Structures have been fabricated with PMMA down to approximately 10 nm, and the densest structures fabricated have had 50 nm periods [30], [31]. A series of Au lines on a GaAs substrate formed by PMMA liftoff is shown in Fig. 6;

ALLEE et al.: LIMITS OF NANO-GATE FABRlCATlON 1097

I

Fig. 6. PMMA liftoff of Au on a GaAs substrate. The lines from top to bottom are 270 nm, 170 nm, Y4 nm, 56 nm, 31 nm, and 16 nm.

the smallest line is 16 nm. Numerous laboratories have fabricated 111-V field effect transistors and lateral quantum effect devices with nanometer scale gate electrodes using the PMMA liftoff process [1]-[13]. Working devices with gate lengths down to 25 nm have been achieved [4]. A high magnification micrograph of an 80-nm gate in self-aligned gate recess for a GaAs FET is shown in Fig. 7 along with the current voltage characteristics [ 5 ] .

The point exposure distribution of PMMA has been measured by one of us (ANB) by exposing a thin layer of resist (30 nm) on a thin SiSN4 membrane (60 nm) with a sub-1-nm beam [32]. The experiment avoided unreliable measurements of linewidths in the resist by exposing a test pattern at several doses and noting the dose necessary for a given linewidth to develop out. Assuming the point spread function is Guassian, sigma was determined to be approximately 12.5 nm. This corresponds to the slightly smaller minimum feature size of 10 nm that has been observed because one can slightly underexpose and or underdevelop. Furthermore, using this point spread sigma of 12.5 nm and assuming a minimum useful contrast of 0.60, an estimate of the minimum possible period was calculated to be 45 nm. This estimate corresponds to the densest structures that have been fabricated.

The question naturally arises; why is the resolution limit of PMMA more than an order of magnitude larger than the electron beam diameter especially when forward scattering and backscattering are eliminated by exposing a thin resist on a thin membrane? The answer to this important question is not entirely known. It has been suggested that the resolution limit is due to the lateral range of the low energy secondary electrons [32]. Secondary electrons are capable of breaking bonds with energies as low as 5 eV and have a range of several nanometers depending on the material (2 nm in Cu, 5 nm in AI) [26]. It is well known that the range of secondaries limits the resolution of secondary electron micrographs [26]. However, Rishton and coworkers have measured the range with which low energy electrons can expose PMMA [33], [34]. Exposure with 100 eV electrons developed away less than 5 nm of resist. Computer simulations based on this data indicate that at line doses that experimentally result in 10-nm features, the secondary electrons should only limit the resolution

Scaled MESFET I V Characteristics

CnA) 10

284 1 / d l v

0.1 volt steps

0000 2.000

VOS .2000/div < V) . 0000

( b)

Fig. 7. (a) High magnification micrograph of the gate of a MESFET [6]. The gate is 80 nm long in a 160 nm recess. (b) Current-voltage characteristics for this device. The gate voltage varies from 0.5 to -0.4 V in 0.1-V steps.

to 2 nm. An alternative explanation for the resolution limit is the size of a PMMA molecule [34]. Electron beam exposure breaks the PMMA chain into fragments with molecular weights below the entanglement threshold (16 000) dramatically enhancing solubility in developer. A fragment of 16000 molecular weight would occupy a sphere of approximately 4-nm in diameter; the minimum feature size that can be fabricated is about twice this size allowing for random positions of the molecules. Other explanations involve gas evolution and pore formation upon exposure and the dynamics of development [35].

Iv . CONTAMINATION RESIST In the 1960’s, a lithographic process was discovered by

R. F. W. Pease [36] and developed by A. N. Broers [37] in which a finely focused, high current density electron beam polymerizes residual vacuum pump oil on the specimen surface. This negative acting “contamination resist” can be used to mask a wet chemical etch or ion milling. The latter approach was used to fabricate 8-nm AuPd lines on Si3N4 membranes [38]. More recently a 5-nm AuPd

1098 PROCEEDINGS OF THE IEEE, VOL. 79, NO. 8, AUGUST 1991

Fig. 8. resist. The lines are 25 nm on a 65-nm period.

Ion milled AuPd on Si substrate using contamination

line was achieved [24]. Although the resolution is slightly higher, contamination resist is not as widely used as PMMA because of the large dose, 0.1 to 1 C/cm2, required to build up a sufficiently thick ion milling mask and because

w e have attempted to push the limits of contamination resist for dense structures. An AuPd grating has been formed on a Si substrate with 25-nm linewidths on a 65-nm period (Fig. 8). To the authors’ knowledge, this is the densest grating fabricated with this technique.

Several devices have been fabricated using contamination resist including microbridges [39], SQUID’S [40], wires to study localization effects [41], X-ray zone plates [42], and Aharonov Bohm rings [43]. In Fig. 9, a 160-nm diameter Aharonov Bohm ring is shown that was fabricated with 350-kV electrons on a Si3N4 membrane; the AuPd wirewidth is 15 nm &1 nm [24]. The high beam voltage reduces forward scattering and allows very high aspect

depletion effects hinder the patterning of dense Fig. 9. A 160-nm diameter Aharonov Bohm ring fabricated On a Si3 iX4 membrane using contamination resist and ion milling; the Aupd wirewidth is 15 nm fl nm p].

ratios, up to 50 : 1, in the contamination resist. In addition to the standard PMMA liftoff, we are also interested in using contamination resist and ion milling to fabricate nanometer scale gate electrodes for pseudomorphic MODFET’s. A device structure is shown in Fig. 10 with a 35-hm gate aligned in a 0.4-pm source drain gap. The device is 25-pm wide and will have a central gate feed.

V. INORGANIC RESISTS Several inorganic resists have resolutions that more

closely approach the beam diameter. In 1978, 5-nm holes were first drilled into 250-nm thick NaCl [44], [45]. Subsequently, 1- to 2-nm features were achieved in thinner layers of AlF3, LiF, MgF2, NaCl [46], [47], and metal P-aluminas 1481. CaF2 [49] and SrF2 [50] have also been directly exposed with electron beam irradiation. The required doses are heavy ranging from to lo3 C/cm2 for the metal halides. These resists are self- developing; although the reaction mechanisms are not clearly understood, a common denominator appears to be electron stimulated desorption of the more electronegative element. The metal atoms may or may not be removed depending on the dose, feature size, and particular inorganic resist. In the case of CaF2, the metal remains as CaO and can be removed with a water rinse. Other studies of

( b)

Fig. 10. (a) A 35-nm gate electrode aligned in the source drain gap of a device structure fabricated using contamination resist and ion milling. (b) A high magnification view of the gate in the source drain gap.

the physics of electron stimulated desorption of anions from ionic solids reveal an energy threshold of 30 to 40 eV [51], [52]. If these mechanisms are applicable, the lower energy secondary electrons would be unable to initiate an exposure event possibly explaining the higher resolution. The densest structures fabricated with these inorganic resists have had periods of 3 to 4 nm [47]. The

ALLEE et al.: LIMITS OF NANO-GATE FABRICATION 1099

scanning electron beam

contamination

\ forward scattered beam

Fig. 11. Schematic view of electron beam exposure through a sacrificial layer. The sacrificial layer along with the surface con- tamination is stripped prior to the development of the underlying oxide.

limit appears to be redeposition of material to an adjacent feature. Pattern transfer processes, however, that replicate this 1-nm resolution have yet to be developed and these resists have therefore not been used to fabricate devices. In general, the metal halides do not hold up well to wet and dry etches. The smallest features transferred to date range between 8 and 20 nm and have been fabricated in Si, Au or Si3N4 with reactive ion etching or ion milling [47], [53].

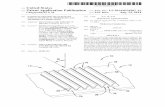

We have recently directly patterned Si02 with nanometer scale resolution by exposing through a sacrificial layer [54]. Si02 was first directly patterned with electron beam irradiation (1 to 15 kV) in 1967 when O’Keeffe and Handy found that regions bombarded with a dose of 1 C/cm2 etched 3 to 4 times faster in p-etch (15 : 10 : 30; H F : HN03 : H20) [ S I . The major difficulty in repeating these experiments has been the build-up of contamination on the surface of the oxide in the presence of the electron beam. Even trace amounts of contamination completely block the wet etch. To the author’s knowledge, the smallest feature size previously achieved was the 0.6-pm trench reported by O’Keeffe and Handy [%I. We have overcome this contamination problem by electron beam exposure through a sacrificial layer (Fig. 11). The contamination builds up on the surface of the sacrificial layer which is subsequently stripped before etching the Si02.

For our preliminary experiments, 100 nm of PMMA was used as a sacrificial layer on 250 nm of thermally grown oxide. Periodic lines were written with a line dose of 750 x C/m at a beam voltage of 300 kV to minimize the forward scattering. Monte Carlo simulations [27] indi- cate that for these conditions, the forward scattering should be less than 12 nm at the base of the oxide. The PMMA was stripped along with the contamination in ultrasonic acetone. Some polymerized PMMA (negatively exposed) remained in the regions of exposure and was removed by rubbing with a q-tip leaving the surface of the oxide clean and smooth. In the optical microscope there was no visual difference in the exposed and unexposed regions. The exposed regions were

( b)

Fig. 12. An array of lines or trenches in S i02 with decreasing period. The second smallest period is 42 nm with sharply defined 12-nm wide trenches. The smallest period, 21 nm, can also be seen. (a) Low magnification, and (b) high magnification.

then developed away with buffered HF or p-etch timed to remove 100 nm of the field oxide. An array of lines in Si02 shadowed at 45’ with Au is shown in Fig. 12. There arc five periods decreasing in factors of 2 from 340 nm. The second smallest period has sharply defined 12-nm trenches on a 42-nm period. The smallest period, 21 nm, is also clearly discernable and is close to the limit we would expect due to forward scattering. The actual width of these trenches is not clear because of the fundamental resolution limit of secondary electron images and the grain size of Au.

Again, the mechanism of the exposure is not clearly understood, but the electronegativity difference between Si and 0 (1.7) is sufficiently large that the exposure mechanism may have some similarities to that of the metal halides. It is known that e-beam irradiation of Si02 causes surface oxygen desorption and stable bulk vacancy centers [56]; the interactions usually thought to be responsible for the formation of these defects have a energy threshold of 30 to 40 eV [51]. Unlike the metal halides, this process is not self-developing. The Si02 etch rate of the HF based developers, in particular p-etch, are known to be sensitive to oxide density, bond strain, etc. [57].

In search of an electron beam lithography process that matches the minimum probe diameter of 0.3 nm, there have been attempts to find a suitable material and developer for radiation lithography [%I. In this process an electron with sufficient energy (above 150 keV for Si) will knock

1 loo PROCEEDINGS OF THE IEEE. VOL. 79, NO. 8, AUGUST 1991

a substrate atom out of its lattice site. If an electron has an energy less than twice the damage threshold, only one exposure event can occur per incident electron resulting in a feature size equal to the beam diameter. Since we have been able to expose Si02 at 100 kV, and in light of O’Keeffe and Handy’s experiments at 1 to 15 kV, it is unlikely that radiation damage is a significant part of the Si02 exposure mechanism.

These preliminary experiments indicate that the resolu- tion of Si02 for dense structures, lines and spaces on a 21-nm period, is better than PMMA where measurements of the point spread function suggests a minimum period of 45 nm [32]. A thin oxide on a membrane must be patterned and imaged in transmission to determine the ultimate reso- lution of this process. Because of the unique properties of SiOz and its widespread application in the integrated circuit industry, the nanometer scale patterns in Si02 may be more readily transferred to the underlying material and will enhance the techniques available to fabricate ultrasmall devices. Experiments are underway along these lines for both thermally grown and deposited oxide.

VI. GATE RESISTANCE

A. Normally Conducting Gates

Although not a resolution limit, the resistance of a gate electrode is a parasitic that can seriously limit the performance of some devices. This is particularly true for field effect transistors where although the fundamental limit to device switching speed is the carrier transit time deter- mined primarily by the gate length, the device parasitics, particularly the source and gate resistance, must also be minimized in order to approach this limit. The need for good uniformity and sharp edge definition as well as low resistance in the source and drain contacts of FET’s with submicron source drain spacings has led to the development of InGaAs grown contacts [59] and solid phase epitaxial PdGe contacts [60]. Maintaining a low gate resistance as the gate length is reduced below 100 nm is particularly difficult because in order to maintain the same gate cross section and hence the same gate resistance, and unrealistic aspect ratio is necessary. Measured gate resistances for typical sub-100 nm gate lengths fabricated with PMMA liftoff are several hundred ohms [6], two orders of magnitude too high for high performance devices. These extremely high gate resistances offset the principle advantage of reduced carrier transit time. As a result, the fastest FET’s to date have had larger gate lengths between 80 and 150 nm [2], [61]. The FET’s with the shortest gate lengths and higher gate resistances have been primarily useful for the investigation of dc phenomenon such as electron velocity overshoot and quantum interference effects. In order to make further improvements in the performance of high frequency FET’s, it is important to examine how much the resistance can be reduced for nanometer scale gate electrodes.

First we will analyze various approaches to reduce the gate resistance for normally conducting gate metals. In the next section, superconducting gate electrodes are

multi-fingered gate multiple gate feeds

(b) Fig. 13. (a) Approximate cross sections of two common gate structures. Structure I is a simple rectangular gate with aspect ratio H / L g . Structure I1 is a T-gate. Lg is the gate length. (b) Multifingered gate and multiple gate feeds can be used to reduce gate resistance by nz by breaking the gate into n equivalent segments.

considered. There are several possible techniques to reduce the gate resistance to a few ohms. The most obvious though often impractical approach is to increase the thickness of the gate metallization forming a rectangular high aspect ratio electrode (Fig. 13(a), structure I). Another approach is to fabricate a mushroom gate structure (Fig. 13(a), structure 11) with a very small footprint [62], [63]. Both of these techniques are limited primarily by the mechanical stability of the gate electrodes and secondarily by the parasitic sidewall gate to source capacitance. A third approach is to break the gate electrode into several segments (Fig. 13(b)). Each segment is placed in the interstice between an interdigitated source and drain forming a multifingered gate. While maintaining the same total device width, the gate resistance is reduced by a factor of n2 where n is the number of segments. One factor of n arises from each gate segment being shorter, the second factor of n from the segments being in parallel. Alternatively, n equiv- alent gate segments can be formed with multiple gate taps.

The dimensional parameters H and Lg are defined for the two gate structures in Fig. 13. Lg is the gate length. H is the thickness of the gate metallization for the rectangular gate (structure I ) and the vertical and horizontal dimensions of the upper portion of the T-gate (structure 11). The value of H necessary to achieve a total dc gate resistance of 10 R is plotted as a function of gate length for a rectangular gate (Fig. 14(a)), a 2’-gate (Fig. 14(b)), and 10 rectangular gates in parallel (Fig. 14(c)). The calculations assume the gate metal is gold at room temperature with a

ALLEE er al.: LIMITS OF NANO-GATE FABRICATION 1101

1

1 o4

1 o3 h

E 2 E 102

10’

1”

20 40 60 80 100 Gate length (nm)

Fig. 14. The size of H necessary to achieve a total gate resistance of 10 R as a function of gate length, L g , for various gate structures. The gate metal is assumed to be Au at 300 K ( p n = 2.04 pRcm). The total device width is 100 pm. (a) A simple rectangular gate (structure I ) , (b) a T-gate (structure 11), (c) ten simple rectangular gates (structure I ) in parallel; each gate is 10-pm wide to maintain the total device width of 100 pm.

bulk resistivity of 2.04 pQcm. The actual resistivity and magnitude of H would be somewhat higher because of the extremely small dimensions of these structures. The total device width is assumed to be 100 pm; a device width typical of commercial quarter micron microwave HFET’s. A single rectangular gate is clearly implausible for gate lengths below 100 nm because of the difficulty of fabricating gates with at least 20 : 1 aspect ratios. For the T - gate, H must be around 400 nm almost independent of the gate length below 100 nm because most of the conductivity is in the upper portion of the “T”. These dimensions are just plausible for 100-nm gate lengths but not for 20-nm gate lengths. The only technique that appears promising for gate lengths all the way down to 20 nm is placing ten IO-pm gate segments in parallel. For a gate length of 20 nm, the aspect ratio need only be 5 : 1.

These calculations are repeated assuming device opera- tion at 77 K where gold has a resistivity of 0.5 pncm (Fig. 15(a)-(c)). A single rectangular gate still requires an unreasonably large aspect ratio for gate lengths less than 100 nm. The T-gate might be possible to fabricate down to a gate length of 50 nm with an H of about 200 nm. Again the parallel gate segments is the most promising technique with a gate length of 20 nm requiring as aspect ratio of only 1.5: 1.

Although dc resistance has been calculated, the data in Figs. 14 and 15 are valid up to the frequency at which the current is localized at the conductor surface due to the skin effect. The most limiting case in the T-gate where uniform current is assumed in the large upper portion. This assumption will break down when the skin depth is approximately equal to H / 2 . Using the well known formula for skin depth [64],

(11) 1

A, = di...- where .L is the frequency in rad/s, po is the permeability of free space, and g,, is the conductivity, the current in the T-gate will be uniform for frequencies up to 126 GHz at 300 K and 127 GHz at 77 K.

Fig. 15. The size of H necessary to achieve a total gate resistance of 10 R as a function of gate length, Ly, for various gate structures. The total device width is 100 pm. For structures a-c, the gate metal is assumed to be Au at 77 K ( p n = 0.5 pRcm). (a) A simple rectangular gate (structure I ) , (b) a T-gate (structure II) , (c) ten simple rectangular gates (structure I ) in parallel; each gate is 10-pm wide to maintain the total device width of 100 pm. (d) A simple rectangular gate (structure I ) made of superconduct- ing YBaCuO at 77 K. The superconducting material properties are assumed to be: T, = 90 K, pn(lOO Ii) = 1,jO pRcm, XL(O I<) = 140 nm.

B. Superconducting Gates With the advent of high T, superconductors [65] , it

may be possible to reduce the gate resistance with a superconducting gate electrode operating at liquid nitrogen temperature. This assumes that the current technological problems with the epitaxial growth of good high T, super- conducting films on 111-V substrates are ultimately solved. The gate resistance, however, is strictly zero only at dc and increases with the square of frequency. We are particularly interested in frequencies deep into the millimeter wave band (30-300 GHz) beyond the fmax of longer gate length HFET’s. This phenomenon can best be understood with the London two fluid model [66]. The superconductor is modeled as a parallel combination of a superconducting channel and a normally conducting channel. The supercon- ducting channel has no resistance but has inductance due to the inertia of the Cooper pairs. The normal channel has resistance and inductance due to the inertia of the electrons. This inertial or kinetic reactance of the normal channel is negligible compared the resistance and is usually ignored (Fig. 16). At dc, the inductance of the superconducting channel shorts out the normal channel resistance resulting in a perfectly conducting wire. As the frequency increases, the reactance of the superconducting channel increases causing current to flow in the normal channel and resulting in a net series resistance for the superconductor.

In order to determine the magnitude of this resistance at microwave and millimeter wave frequencies, lets as- sume we have a gate electrode made of c axis oriented YBanCus07-e, the most thoroughly studied high T, su- perconductor. From the measurements on thin films by Kapitulnik and Char [67], it has a critical temperature, T,, of 90 K, a coherence length parallel to the plane, <, of 1.2 nm, an energy gap at 0 K of 54 meV, a normal state resistivity at 100 K of 150 pLRcm, and a dc critical current density at 77 K greater than 2 x lo6 A/cm2. In bulk form the London penetration depth at 0 K, AL (0),

1101 PROCEEDIVGS OF THE IEEE VOL 79 YO 8 AL‘GCST 1991

io3

lo2

I I m Ls

Fig. 16. The London two-fluid model of a superconductor. A superconducting inductance, L,, whose physical origin is the inertia of the Cooper pairs is in parallel with a normal channel resistance, R,.

has been measured to be 140 nm [68]. There are several assumptions in the London two-fluid

model. The normal electron mean free path and the co- herence length of the superconducting electrons must be less than the London penetration depth in order to use the local theory, J = aE. Since the penetration depth is proportional to (1 - t4)-'/z where t , is the temperature normalized to T,, XL at 77 K is 205 nm. This is much larger than the coherence length and also larger than the mean free path of the normal electrons if we assume sufficiently "dirty" material. Furthermore, the cross section dimensions of the gate electrode must be equal to or less than twice the penetration depth in order to assume uniform current density. This is also true since the largest gate length we are considering is 100 nm. Finally, the operating frequency must be less than the energy gap frequency at which the electric field will break the Cooper pairs. Since the energy gap is proportional to (1 - t,), the energy gap at 77 K is 20.7 meV corresponding to a frequency of 5.02 THz. The largest frequency we will be considering is 300 GHz, the upper limit of the millimeter wave band. Under these conditions, the London two-fluid model is applicable.

The total current through the superconductor can be written as

J = (an + a,)E (12)

where an and us are the normal channel and superconduct- ing channel conductivities, respectfully. J is the current density and E is the electric field. These conductivities can be conveniently expressed in terms of measured parameters as follows:

an0 is the normal channel conductivity just above T,; j is the square root of negative 1. The remaining variables maintain their previous definitions. The normal channel resistance, Rn, and the superconducting inductance, L,, are

where 2 is the device width. A rectangular cross section of length, L,, and height, H , is assumed (structure I). The equivalent series resistance, Rseries, is

Rseries = Rnw2L: Ra + w2L:

h 5 10' : .4 100 ;;

10-1

Fig. 17. The gate resistance as a function of frequency for superconducting YBaCuO at 77 K. The superconducting material properties are assumed to be: T, = 90 K, pnormal(lOO K) = 150 pRcm, XL(O K) = 140 nm. The total device width is 100 pm. The three gate electrodes shown all have square cross sections (structure I, Lg = H). (a) Lg = H = 20 nm, (b) Lg = H = 50 nm, and (c) Lg = H = 1 0 0 nm.

The end-to-end gate resistance for a 100-pm wide device as a function of frequency for H = Lg = 20 nm, 50 nm, and 100 nm are plotted (Fig. 17). While the gate resistances are all less than 1 R at 10 GHz, they reach lo00 R at 300 GHz. At 100 GHz, the value of H required for a total gate resistance of 10 fl as a function of gate length is also plotted for a superconducting gate electrode (Fig. 15(d)). It is significant that H for a superconducting electrode at 100 GHz is still an order of magnitude larger than the H required for the ten normally conducting gate electrodes in parallel. While the superconducting gate electrode could be fabricated in a parallel structure as well, there isn't much motivation to do so because of the sufficiently low aspect ratio of the normally conducting gate electrodes in parallel. This is particularly true in view of the current processing difficulties associated with high T, superconductors: the difficulty of depositing films on GaAs substrates and the high temperature anneal that is incompatible with GaAs.

For completeness, the current carrying capabilities of high T, superconductors at millimeter wave frequencies must also be considered. To the author's knowledge, this measurement has not yet been made. Kwon has estimated the ac critical current to be 50 A/pm based on the low critical magnetic field of the high T, superconductor [69]. This current density would be sufficient for small signal applications.

VII. CONCLUSIONS The resolution limit of probe formation is fundamentally

limited by the source brightness and the saturation flux density in iron. Experimentally measured probe diameters just under 0.5 nm have been achieved. This resolution is one to two orders of magnitude smaller than nano-gates can be fabricated in a working device. The most commonly used resists, PMMA and contamination, do not have sufficient resolution. Inorganic resists that have a resolution approach- ing the beam diameter have been found but suitable transfer processes have yet to be developed generally because of poor wet and dry etch resistance. Preliminary results indicate that Si02 can be patterned with nanometer scale

ALLEE et al.: LIMITS OF NANO-GATE FABRICATION 1103

resolution by direct e-beam exposure through a sacrificial layer; the ultimate resolution of Si02 has yet to determined. Because of the unique physical properties of Si02 and its widespread use in the integrated circuits industry, this litho- graphic technique should enhance the tools available to fab- ricate nanometer scale devices. Finally, the most promising approach to reduce the resistance of a nano-gate and hence dramatically improve the performance of some high fre- quency devices is the uqe of multifingered gates or multiple gate taps with a normally conducting gate metal, and gate aspect ratios should be as large as is practical to fabricate.

REFERENCES

U.K. Mishra, R. S. Beaubien, M. J. Delaney, A. S. Brown, and L. H. Hackett, “Low noise O.lpm GaAs MESFET’s by MBE,” in Proc. IEEEICornell Conf Advanced Concepts in High Speed Semiconductor Devices and Circuits, Ithaca, NY, Aug. 10- 12, 1987,

P.C. Chao, M. S. Shur, R. C. Tiberio, K. H. G. Duh, P. M. Smith, J. M. Ballingall, P. Ho, and A. A. Jabra, “DC and microwave char- acteristics of sub-0. lpm gate length planar doped pseudomorphic HEMT’s,” IEEE Trans. Electron Devices, vol. 36, pp. 461-471, Mar. 1989. W. Patrick, W. S. Mackie, S. P. Beaumont, C. D. W. Wilkinson, and C.H. Oxley, “Very short gate length GaAs MESFET’s,” IEEE Electron Device Lett., vol. 6, pp. 471-472, 1985. J. Han, D. K. Ferry, and P. Newman, “Ultra-submicron gate length AlGaAs/GaAs HEMT’s,” IEEfi Electron Device Lett., vol. 11, pp. 209-211, May 1990. D. R. Allee, P. R. de la Houssaye, D. G. Schlom, J. S. Harris Jr., and R. F. W. Pease, “Sub-100nm gate length GaAs MESFET’s and MODFET’s fabricated by molecular beam epitaxy and electron beam lithography,” J. Vac. Sci. Technol. B, vol. 6, no. 1, pp. 328-332, JanJFeb. 1988. D. R. Allee, P. R. de la Houssaye, D. G. Schlom, B. W. Langley, J. S. Harris, and R. F. W. Pease, “Sub-100nm gate length GaAs MESFET’s fabricated by molecular beam epitaxy and electron beam lithography,” in Proc. IEEEICornell Conf. Advanced Concepts in High Speed Semiconductor Devices and Circuits, Ithaca, NY,

C. P. Umbach, A. Palevski, M. Heiblum, and U. Sivan, “Lateral tunneling and ballistic transport in two dimensional electron gas devices defined by nanostructure gates,” J. Vac. Sci. Technol. B, vol. 7, no. 6, pp. 2003-2006, Nov./Dec. 1989. K. Ismail, W. Chu, D. A. Antoniadis, and H. I. Smith, “Surface su- perlattice effects in a grating gate GaAs/GaAAs modulation doped field effect transistor,” Appl. Phys. Lett., vol. 52, pp. 1071 - 1073, 1988. K. Ismail, W. Chu, D. A. Antoniadis, and H. I. Smith, “Negative transconductance and negative differential resistance in a grid gate modulation doped field effect transistor,” Appl. Phys. Lett., vol. 54, pp. 460-462, 1989. K. Ismail, W. Chu, R. Tiberio, A. Yen, H. J. Lezec, M.I. Shepard, C. R. Musil, J. Melngailis, D. A. Antoniadis, and H. I. Smith, “Reso- nant tunneling across and mobility modulation along surface structured quantum wells,” J. Vac. Sci. Technol. B, vol. 7, no. 6, pp. 2025-2029, Nov./Dec. 1989. S. Y. Chou, D. R. Allee, R. F. W. Pease, and J. S. Harris Jr., “Obser- vation of electron resonant tunneling in a lateral dual gate resonant tunneling field effect transistor,” Appl. Phys. Lett., vol. 55, no. 2, pp. 176-178, 1989. D. R. Allee, S.Y. Chou, J. S. Harris Jr., and R. F. W. Pease, “Engi- neering lateral quantum interference devices using electron beam lithography and molecular beam epitaxy,” J. Vac. Sci. Technol. B, vol. 7, no. 6, pp. 2015-2019, Nov./Dec. 1989. G. Bernstein and D. K. Ferry, “Negative differential conductivity in lateral surface superlattices,” J. Vac. Sci. Technol. B, vol. 5, no. 4, pp. 964-966, 1987. R.L. Kubena, R. J. Joyce, J. W. Ward, H. L. Gamin, F. P. Sratton, and R. G. Brault, “Dot lithography for zero-dimensional quantum wells using focused ion beams,” J. Vac. Sci. Technol. B, vol. 6, pp. 353-356, 1988.

pp. 177-189.

Aug. 10-12, 1987, pp. 190-198.

[15] H. Rarback, D. Shu, S.C. Feng, H. Ade, J. Krz, I. McNulty, D.P. Kern, T.H.P. Chang, Y. Vladimirsky, N. Iskander, D. Attwood, K. McQuaid, and S. Rothman, “A scanning x-ray microscope with 75nm resolution,” Rev. Sci. Instrum., vol. 59, pp. 52-59, 1988.

[16] M.A. McCord and R. F. W. Pease, “Lift-off metalization using PMMA exposed with a scanning tunneling microscope,” J. Vac. Sci. Technol. B, vol. 4, pp. 86-88, 1986.

1171 M. A. McCord and R. F. W. Pease, “High resolution low voltage probes from a field emission source close to the target plane,” J. Vac. Sci. Technol. B, vol. 3, pp. 198-201, 1985.

[18] D. M. Eigler and E. K. Schweizer, “Positioning single atoms with the scanning tunneling microscope,” Nature, vol. 344, pp. 524-526, Apr. 5, 1990.

[I91 D. B. Langmuir, “Theoretical limitations of cathode ray tubes,” Proc. IRE, vol. 25, no. 8, pp. 977-991, 1937.

[20] N. Samoto, R. Shimizu, H. Hashimoto, N. Tamura, K. Gamo, and S. Nambo, “A stable high brightness electron gun with Zr/W-tip for nanometer lithography: I emission properties in Schottky and thermal field emission regions,” Japan. J . Appl. Phys., vol. 24, p. 766, 1985.

[21] J. R. Pierce, Theory and Design of Electron Beams. New York: Van Nostrand, 1954, p. 124.

[22] 0. Scherzer, “Uber einige Fehler von Elektronenlinsen,” Z. Phys.,

[23] G. Leibmann, “A unified representation of magnetic electron lens properties,” Proc. Phys. Soc. W I I I , no. 10B, pp. 737-745, 1955.

[24] A.N. Broers and A.E. Timbs, “Nanolithography at 350kV in a TEM,” Microelecrronic Engineering, vol. 9, pp. 187- 190, 1989.

[25] A. N. Broers and H. C. Pfeiffer, Record of the 11th Symp. on Electron Ion and Laser Beam Technology, R. F. M. Thornley, Ed. New York: IEEE Press, 1971, pp. 205-207.

[26] A. N. Broers, “Factors affecting resolution in the SEM,” in Scanning Electron Microscopyll969, Proc. 3rd Annual Scanning Electron Mi- croscope Symp., I l T Research Institute, Chicago, IL, 1970, pp. 1-8.

[27] D.C. Joy, “An introduction to Monte Carlo simulations,” in Proc. European Meeting on Electron Microscopy 1988, A. J. Craven and H. Elder, Eds. London, U.K.: Inst. of Physics, Inst. Phys. Conf. Ser., vol. 93, no. 1, 1988, pp. 23-32.

[28] T. H. P. Chang, “Proximity effect in electron beam lithography,” J. Vac. Sci. Technol., vol. 12, pp. 1271-1275, 1975.

(291 S. A. Rishton and D. P. Kern, “Point exposure distribution mea- surements for proximity correction in electron beam lithography on a sub-100nm scale,” J. Vac. Sci. Technol. B, vol. 5 , no. 1, pp. 135-141, Jan./Feb. 1987.

[30] H. G. Craighead, R. E. Howard, L. D. Jackel, and P. M. Mankiewich, “10-nm linewidth electron beam lithography on GaAs,” Appl. Phys. Lett., vol. 42, no. 1, pp. 38-40, 1983.

[31] A. N. Broers, J. M. E. Harper, and W. W. Molzen, “25-nm linewidths with PMMA electron resist,” Appl. Phys. Lett., vol. 33, no. 5,

[32] A. N. Broers, “Resolution limits of PMMA resist for exposure with 50kV electrons,”J. Electrochem. Soc., vol. 128, no. 1, pp. 166-170, 1981.

[33] S. A. Rishton, S. P. Beaumont, and C. D. W. Wilkinson, “Measure- ment of the effect of secondary electrons on the resolution limit of PMMA,” in Proc. Microcircuit Engineering 82, Grenoble, Sitecmo Dieppe, Paris, 1982, pp. 341-346.

[34] T. H. P. Chang, D. P. Kern, E. Kratschmer, K.Y. Lee, H. E. Luhn, M. A. McCord, S. A. Rishton, and Y. Vladimirshy, “Nanostructure technology,” IBM J. Res. Develop., vol. 32, no. 4, pp. 478-479, 1988.

[35] A. C. Ouano, E. Gipstein, D. Johnson, and 0. U. Need 111, “Param- eters affecting the sensitivity of poly (methyl methacrylate) as a positive electron resist’’ Polymer Engineering and Science, vol. 17,

[36] R. F. W. Pease, “High resolution scanning electron microscopy,” Ph.D. dissertation, Cambridge University, U.K., Jan. 1964.

[37] A. N. Broers, “Combined electron and ion beam processes for mi- croelectronics,” Microelectron. Rel., vol. 4, p. 103, 1965.

[38] A. N. Broers, W. W. Molzen, J. J. Cuomo, and N. D. Wittels, “Elec- tron beam beam fabrication of 80A metal structures,” Appl. Phys. Lett., vol. 29, no. 9, pp. 596-598, 1976.

[39] R. B. Laibowitz, A.N. Broers, J.T. C. Yeh, and J. M. Viggiano, “Josephson effect in Nb nanostructures,” Appl. Phys. Lett., vol. 37,

[40] R. Voss, R. B. Laibowitz, and A. N. Broers, “Niobium nanobridge DC SQUID,” Appl. Phys. Lett., vol. 37, pp. 656-658, 1980.

(411 P. Chaudhari, A.N. Broers, C .C . Chi, R.B. Laibowitz, E. Spiller,

vol. 101, pp. 593-603, 1936b.

pp. 392-394, 1978.

pp. 396-401, 1977.

pp. 656-658, 1980.

PROCEEDINGS OF THE IEEE, VOL. 79, NO. 8 , AUGUST 1991

and J. Viggiano, “Phase-slip and localization diffusion lengths in amorphous W-Re alloys,” Phys. Rev. Lett., vol. 45, pp. 930-932, 1980. C. J. Buckley, M. T. Browne, and P. Charalambous, “Contamination lithography for the fabrication of zone plate x-ray lenses,” Proc. SPIE, vol. 537, pp. 213-217, 1985. C. P. Umbach, S. Washbum, R.A. Webb, R. Koch, M. Bucci, A. N. Broers, and R. B. Laibowitz, “Observation of h/e Aharonov- Bohm interference effects in sub-micron diameter, normal metal rings,’’ J. Vuc. Sci. Technol. B, vol. 4, pp. 383-385, 1986. A. N. Broers, J. J . Cuomo, J. Harper, W. Molzen, R. B. Laibowitz, and M. Pomerantz, “High resolution electron beam fabrication using an STEM,” Electron Microscopy 1978, Vol. III, J. M. Sturgess, Ed., Microscopical Society of Canada, Toronto, pp. 343-354, 1978. A. N. Broers, J. J. Cuomo, and W. Krakow, “Method for producing lithographic structures using high energy electron beams,” IBM Tech. Disclosure Bull., vol. 24, p. 1534, 1981. M. Isaacson and A. Muray, “In situ vaporization of very low molecular weight resists using l/2nm diameter electron beams,” J . Vac. Sci. Technol., vol. 19, pp. 1117-1120, 1981. A. Muray, M. Scheinfein, M. Isaacson, and 1. Adesida, “Radiolysis and resolution limits of inorganic halide resists,” J. Vac. Sri. Technol. B, vol. 3, no. 1, pp. 367-372, 1985. M. E. Mochel, C. J. Humphreys, J.A. Eades, J . M. Mochel, and A.M. Petford, “Electron beam writing on a 2nm scale in metal b-aluminas,” Appl. Phys. Lert., vol. 42, no. 4, pp. 392-394, 1983. P. M. Mankiewich, H. G. Craighead, T. R. Harrison, and A. H. Dayem, “High resolution electron beam lithography on CaF2 .” Appl. Phys. Lett., vol. 44, no. 4, pp. 468-469, Feb. 1984. P. W. Sullivan, “Summary Abstract: single crystal SrF2 on GaAs(001)-an electron beam resist and dielectric for insula- tor/semiconductor structures,” J . Vac. Sci. Technol. B, vol. 2, no. 2, pp. 203-204, Apr./June 1984. P. J. Feibelman and M. L. Knotek, “Reinterpretation of electron- stimulated desorption data from chemisorption systems,” Phys. Rev. 8, vol. 18, no. 12, pp. 6531-6539, Dec. 1978. M. L. Knotek, “Stimulated desorption from surfaces,” Phys. Today, pp. 24-32, Sept. 1984. E. Kratschmer and M. Isaacson, “Nanostructure fabrication in met- als, insulators, and semiconductors using self-developing metal inorganic resists,”J. Vac. Sci. Technol. B, vol. 4, no. 1 , pp. 361 -364, Jan./Feb. 1986. D. R. Allee and A. N. Broers, “Direct nanometer scale patterning of S i02 with electron beam irradiation through a sacrificial layer,” Appl. Phys. Lett., vol. 57, no. 21, pp. 2271-2273, Nov. 1990. T. W. O’Keeffe and R. M. Handy, “Fabrication of planar silicon transistors without photoresist,” Solid-State Electron., vol. 11,

W. Beall Fowler, “Point defects and production mechanisms in SiOz,” Semicond. Insul., vol. 5 , pp. 583-598, 1983. W. A. Pliskin, “Comparison of properties of dielectric films de- posited by various methods,” J . Vac. Sci. Technol., vol. 14, no. 5,

G.A.C. Jones, S . Blythe, and H. Ahmed, “Very high voltage (500kV) electron beam lithography for thick resists and high resolution,”J. Vac. Sri. Technol. B, vol. 5 , no. 1, pp. 120-123, 1987. I . Mehdi, U.K. Reddy, J . Oh, J.R. East and G. I . Haddad, “Non- alloyed and alloyed low resistance ohmic contacts with good mor- phology for GaAs using a graded InGaAs cap layer,” J . Appl. Phys., vol. 65, no. 2, pp. 867-869, 1989. Ph. Jansen, W. De Raedt, M. Van Hove, R. Jonckheere, R. Pereira, and M. Van Rossum, “Submicron pseudomorphic HEMT’s using non-alloyed ohmic contacts with contrast enhancement,” MRS Spring Meeting, 1990. L. F. Lester, P. M. Smith, P. Ho, P. C. Chao, R. C. Tiberio, K. H. G. Duh, and E. D. Wolf, “0.15pm gate length double recess pseudomor- phic HEMT with f,,, of 350GHz,” IEDM Tech. Dig., pp. 172- 175, 1988. C. E. Weitzel and D. A. Doane, “A review of GaAs MESFET gate electrode fabrication technologies,” J . Electrochem. Soc., vol. 133, pp. 409C-416C, Oct. 1986. A. Chisholm, S. Sainson, M. Feuillade, and A. C!ei, “0.lSpm e-beam T-shaped gates for GaAs FET’s,” Microcircuit Engineering Abstracts, p. 36, Sept. 1989. S. Ramo, J. R. Whinnery, and T. van Duzer, Fields und Waves in Communication Electronics. M. K. Wu, J. R. Asburn, C. T. Torng, P. H. Hor, R. L. Meng, L. Gao,

pp. 261-266, 1968.

pp. 1064-1081, 1977.

New York: Wiley, 1984.

-

I

ALLEE el al LIMITS OF NANO-GATE FABRICATION

!

Z . L. Huang, Y . Q. Wang, and C. W. Chu, “Superconductivity at 93K in a new mixed-phase Y-Ba-Cu-0 compound system at ambient pressure,” Phys. Rev. Lett., vol. 58, pp. 908-910, 1987. J. I . Gittleman and B. Rosenblum, “Microwave properties of super- conductors,” Proc. IEEE, vol. 52, pp. 1138-1147, 1964. A. Kapitulnik and K. Char, “Measurements on thin film high-Tc su- perconductors,” IBM J. Res. Develop., vol. 33, no. 3, pp. 252-261, 1989. R. J. Cava, B. Batlogg, R. B. van Dover, D. W. Murphy, S. Sunshine, T. Siegrist, J.P. Remeika, E.A. Rietman, S. Zahurak, and G.P. Espinosa, “Bulk superconductivity at 91K in single-phase oxygen- deficient perovskite BazYCuaOg-d,” Phys. Rev. Lert., vol. 58, no. 16, pp. 1676-1679, 1987. 0. K. Kwon, “Chip-to-chip interconnections for very high speed system level integration,” Ph.D. dissertation, Stanford University, CA, 1986.

David R. Alee received the B.S. degree in electrical engineering from the University of Cincinnati, OH, in 1984 (valedictorian) on a Voorheis Honor Scholarship. He received the M.S. and Ph.D. degrees in electrical engineering from Stanford University, CA, in 1986 and 1990, respectively on an American Electronics Association Faculty Development Fellowship. His dissertation research involved the use of high resolution electron beam lithography to incorporate nanostructures in both conventional

and novel quantum based devices. While at Stanford he was a co- instructor in a new graduate level course on high resolution beams in microfabrication technology. He was also involved in the modeling of the reduced electron energy spread in laser irradiated cathodes of electron beam lithography. Since October 1989, he has been a post-doctoral research associate at Cambridge University where he has continued work on nanometer scale devices and nanostructure fabrication techniques.

Alec N. Braers was educated in Austrialia and England. He received the undergraduate de- grees in physics and in electronics in 1959 and 1960 respectively, from Melbourne Univer- sity. He received the undergraduate degree in mechanical sciences in 1962 from Cambridge University, U.K. He received the Ph.D. degree in electrical engineering in 1965 from Cambridge University.

Following completion of the Ph.D. degree, he worked for IBM in the US. until 1984. He was

elected an IBM Fellow and held a series of management positions in IBM including responsibility for the Photon and Electron Optics groups at the Yorktown Research Center from 1971 to 1981 (Semiconductor Lithography and Process Development in IBM’s East Fishkill Laboratory and Advanced Development at East Fishkill). In 1984 he was a member of the IBM Corporate Technical Committee. Presently, he is Master of Churchill College, Cambridge, and is Professor of electrical engineering and Head of the Electrical Engineering Division at the Cambridge Uni- versity Engineering Department. At Cambridge he continues his personal research on the application of small electron beams (diameters down to 0.3 nm) to microscopical and microfabrication problems. These include the fabrication of quantum devices and ultrasmall transistors. He has published numerous articles on high resolution lithography and related subjects.

Dr. Broers received the American Institute of Physics Prize for indus- trial applications of physics in 1981 and the IEEE Cledo Brunetti Award in 1985. He is a Fellow of the IEE, the Fellowship of Engineering, and the Royal Society.

R. Fabian W. Pease, for a photograph and biography please see page 1092 of this issue.

1105