GYANDEEP - Indian Railways Institute of Signal Engineering ...

-

Upload

khangminh22 -

Category

Documents

-

view

0 -

download

0

Transcript of GYANDEEP - Indian Railways Institute of Signal Engineering ...

ìððÐðÇóÑðìððÐðÇóÑðìððÐðÇóÑðìððÐðÇóÑðIRISET Newsletter Volume-3 Issue I

GYANDEEP

Indian Railways Institute of

Signal Engineering and TelecommunicationsTarnaka Road, Secunderabad

HIGHLIGHTS OF ACTIVITIES

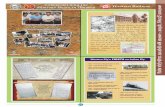

Glimpses of Annual Day

Shri Kul Bhushan, Member Electrical, Railway Board

inaugurated the New Signal and Telecom Laboratory and E-

Learning Centre building on 03rd April 2014 in the august

presence of Shri.P.K.Srivastava, General Manager, South Central

Railway, Shri. Satyender Kumar, Director/IRISET and

Shri.S.K.Sharma, CAO, South Central Railway. Member Electrical,

addressed the Officer trainees and Apprentice SSE trainees in the

Auditorium & emphasised on the important role of S&T Engineers

have to play in the growth of Indian Railways. He also inspected the

renovated badminton courts and the new Gymnasium at IRISET.

56th Annual Day celebrations were held on 24.11.2013.

Shri Pradeep Kumar Srivastava, GM/SCR presided over the

function. Shri M.Suresh, Additional Member (Sig)/Railway Board &

Shri P.K.Srivastava, Additional Member (Tele)/Railway Board were

Guests of Honour for the function. Director/IRISET presented the

Annual Report of IRISET. Academic awards were given away to the

trainees who stood first in their respective batches during the

year. The function concluded with cultural programme.

During the Annual

Day celebrations,

anniversary issue of

“ G y a n d e e p ” w a s

released by

Shri P.K.Srivastava,

General Manager/

S o u t h C e n t r a l

Railway

The Lecture notes on

Signalling on Subjects

– S9, S10, S14 & S22

which are translated

in Hindi inhouse were

released during the

A n n u a l D a y

celebrations.

Renovated Badminton Hall and Gymnasium were

inaugurated by Additional Member (Sig)/ Railway Board &

Additional Member (Tele)/Railway Board on 24.11.2013. The

depilated hall has been completely redone and provided with

synthetic mats of International Standard and a small Gymnasium

has been built within this hall for benefit of trainees

The Computer Based Training Module on maintenance and

trouble shooting on Automatic Signalling has been prepared in-

house. This was demonstrated to Additional Member (Sig)/

Railway Board & Additional Member (Tele)/ Railway Board in Train

Detection Systems Laboratory on 24.11.2013.

ìððÐðÇóÑð

Gyandeep

IRISET02

ìððÐðÇóÑð

Gyandeep

IRISET03

The Electronic Interlocking System of M/s. Medha make has

been installed along with Training Simulator software and CBT

module. The same was inaugurated by Additional Member

(Signal)/Railway Board on the Annual Day.

The GSM-R system connected with MSC at Agra has been

commissioned for the purpose of imparting hands on training on

Mobile Train Radio Communication to officers and supervisors.

CBT module has also been commissioned in this Lab. The system

was formally inaugurated by Additional Member (Tele)/Railway

Board.

Workshop on “Concept and Systems for Improving

Reliability & Safety of Signalling Equipments” was conducted on

25.11.2013 in which Additional Member (Signal)/Railway Board,

Sr.ED/RDSO, Advisor(Signal)/ Railway Board and PHOD/HOD from

Zonal Railways participated.

IRISET Advisory Committee Meeting was held on

25.11.2013 under the Chairmanship of Additional Member

(Sig)/Railway Board in which CSTEs of SCR, SR & SER,

Director/IRISET and Executive Director(T&MPP)/Railway Board

attended and discussed various aspects of training at IRISET.

Review of content in Signalling and Telecom modules was

discussed. Allocation of additional time slots for new technological

systems introduced in Railways was discussed.

A workshop on “Communication based Signalling &

Developments in Signalling” was conducted on 27.12.13 for IRSSE

SAG officers of 1986 exam batch who have completed 25 years of

Railway Service in which 19 officers participated.

Republic Day was celebrated on 26.01.2014 with much

fervor and enthusiasm which was attended by Faculty, Staff and

Trainees.

As a part of Republic Day celebrations, tree plantation

programme was conducted in which trees were planted by faculty

& IRSSE Probationers of 2012 exam batch.

ìððÐðÇóÑð

Gyandeep

IRISET04

Reliability Improvement of Axle Counters in WCRShri Sanjay Tiwari,

Dy.CSTE/JBP/WCR

There were significant failures of axle counters, especially Digital Axle Counters, in WCR in

the year 2011-12. These failures also affected punctuality of several Mail/ Express trains.

There are approximately 259 equipments of Analog axle counters and 1019 equipments of

Digital axle counters installed in WCR. The population of axle counters (nos of equipments),

make-wise, installed in WCR is: CEL Analog: 143, CGL Analog: 40, Byculla Analog: 76, Alcatel

Digital: 710, CEL Digital: 282, GG Tronics Digital: 18 and Siemens Digital: 9.

The types of failures witnessed in Axle Counters are: DP hang, Reset (other than testing),

cards defect, lightening related, TX/ RX coils related, mother board, DC-DC converter,

Engineering activities, other reasons etc. In order to reduce these failures, innovative and

cost effective reliability improvement measures were initiated on WCR.

These reliability improvement measures are mentioned as follows:

1) Provision of coil and 4700 microfarad capacitor [low pass

filter] across power supply on Eldyne SSDAC: To minimize

the cases of DP getting hanged due to surges. Diagram

shown. Activity completed in the year 2012-13.

2) Improvement in earthing in CEL Axle counters:

Being carried out to improve the EMI performance of

DACs (Diagram shown below) [80% done]

3) Improvement in earthing in Eldyne SSDACs:

Being carried out to improve the EMI performance of DACs (Diagram shown below)

[56.5% done]

Steps for improvement in Earthing (Eldyne and CEL):

• Weld the clamp with GI pipe.

• Replace Iron Nuts & Bolts by SS/brass nuts & bolts.

• Replace clamp with SS/ 304 clamp.

• Thread the bolt in the location body.

• Tighten with check-nuts.

• Replace GI wire with double SS wire rope connected with lugs at both ends.

4) Shifting of TX/ RX coils on non-cess rails:

To prevent the failures due to movement of rail dolly etc which are moved by the Engg

staff from cess side of the track. Activity completed in the year 2012-13.

5) Painting of SSDAC/ MSDAC location boxes/ DPs with cooling paint:

The location boxes/ DPs of DACs have been painted with cool and seal paint which gives a

temperature reduction of 3-4 degrees. Activity completed in the year 2012-13.

6) Provision of remote cut and resume of power supply for IBH DP hang cases (Eldyne):

When DAC DPs of IBH hang, it takes a long time to reach IBS location to cut and resume the

Surge

amplitude SPD alone

Surge

amplitude

SPD + LPF

Effect of Low Pass Filter [ coil and 4700 microfarad capacitor] on surges in Eldyne SSDAC

5

power supply, leading to detention to traffic. An arrangement has therefore been developed (pressing a switch at station and consequent picking up of relay at IBH hut) to remotely reset the IBH DP from station itself. Activity completed departmentally in the year 2012-13.

7) BPAC: Redundancy at worst locations: To enhance reliability and reduce failures of

BPAC. 17 out of 38 block sections provided. Activity in progress.

8) AMC of Eldyne SSDACs: Work sanctioned in KOTA div.9) Keeping 5/ 10 pairs cable at station for axle

counter for quick restoration when Quad cable is damaged / faulty: 81% completed.

10) Provision of isolation transformer of 470/ 600 ohms on communication pair of quad cable in BPAC/ IBH application [Eldyne BPAC/ IBH]:

To avoid impedance mismatching, problem of non-optimal power transfer and to improve the surge protection performance. [61% done]

11) Low cost maintenance free earthing for Digital Axle Counter field locations [DPs]:

The earthing of ordinary type being provided now to the DACs is not good enough for the sensitive electronics of the axle counters. On the other hand, the maintenance free earth as per RDSO specification is very costly and theft prone. Thus, a low cost and theft proof earth has been developed for provision on DPs of DACs, which will be completely maintenance free. This will go a long way in reducing the cases of unexplained failures. [Diagram shown below] {Initiated in 2013-14}

12) Provision of DC-DC converters in 1+1 configuration for each DP [DPs of BPAC & IBH]:

To prevent failure of both BPAC/ IBH at same time. Also, DC-DC converters to be fed directly

with 110 V battery to prevent failures due to non-functioning of IPS. Activity in progress. [Initiated in 2013-14]

13) Providing packing on top of the cards inside the mushroom DPs of Eldyne axle Counters to prevent vibrations due to movement of trains: Activity completed in the current year 2013-14.

14) Provision of Converters to Eldyne MSDAC DPs having more than 16 DB loss as per Minutes of the Meeting with M/s Thales in June 2013 [Eldyne DPs]: In progress. [Initiated in 2013-14]

15) Provision of SPDs to digital axle counters [DPs] after procurement from RDSO recommended sources: Activity in progress. [Initiated in 2013-14]. The effect of a surge, say of - 30 V magnitude, on 24 V supply of DAC is shown below in schematic on left side. The resultant voltage, during period of surge, is shown by dotted line.

A u g u r e d H o l e 1 0 0

m m t o 1 2 5 m m D i a

N a t u r a l s o i l/ b a c k f il l

c o m p o u n d

1 5 0 m m

M in im u m

P r e ca s t R C C

C h a m b e r w i t h

co v e r w it h p u l l in g h o o k . S iz e a p p r o x

3 0 0 x 3 0 0 x 3 0 0 m m ,

2 5 m m t h i ck

S S w i r e r o p e 1 X 1 9 , 1 2 m m

( n o m i n a l ) d ia . S S g r a d e - 3 1 63 X 3 0 X 2 0 0 0 m m

s t a i n l e s s s t e e l a n g le

( g r a d e 3 0 4 )

E a r t h e n h a n ci n g

c o m p o u n d

O n e w ir e r o p e

c o n n e c t e d o n e it h e r s id e o f t h e

e a r t h b a r

L o w c o s t m a i n t e n a n c e f r e e e a r t h i n g f o r D A C D P s

CEL SSDAC

6

Eldyne MSDAC

16) Provision of Ground Shield Lightening Protection for IBH Eldyne make Digital Axle Counter DPs [DPs]:

On 01/07/2013, there were extensive damages to most of the cards including mother boards of Eldyne make DACs installed at IBH between Ravtha Road and Alaniya in KOTA division due to lightening. Hence, this scheme has been initiated to be provided at the most vulnerable IBH Eldyne make Digital Axle Counter DPs [DPs] only. The schematic diagrams are as follows:

Because of adoption of these innovative and cost effective reliability improvement measures, 3276 nos. of failures of axle counters during the year 2011-12 reduced to 2284 nos. of failures of axle counters during the year 2012-13, i.e., reduction by 30.3 %. Also, because of some more innovative and cost effective reliability improvement measures initiated during the year 2013-14, 1040 nos. of failures of axle counters during the year 2012-13 [till 31/08/2012] reduced to 988 nos. of failures of axle counters during the year 2013-14 [till 31/08/2013], i.e., reduction by 5 %

Eldyne SSDAC

DP

The flow of lightning current from the lightning spot,

takes a path into the rings of ground shield and passes on

to the other side of ground without going to the DP,

because of much smaller resistance of the metallic

path as compared to that of earth.

Ground Shield Lightening Protection (GSLP) provides a bypass path to the EldyneDigital Axle Counter DP

7

Designing Microlok-II Application Software for a new StationShri. P. Sreenivasu

Lecturer signalling -2

The Electronic Interlocking (EI) requires two softwares to meet railway interlocking, namely Executive Software and Application Software.

• Executive Software: This software is c o m m o n t o a l l t h e s t a t i o n E I ’s manufactured by the same company. This is Factory installed software and User (Railway Signal Engineer) has no access to modify it.

• Application Software: This software is different for each station though the same company EI is employed. This is specific to each station and prepared as per Table Of Control. It can be installed by Signal Engineer at site. This can be modified when the yard alternations are done.

Broadly Microlok-II designing for a new station involves

1. Interface design2. Application software design

Microlok-II Interface Design:I. Involves estimating accurately the number

of Microlock-II card files i.e. vital input, vital output, non vital input & output cards and associated hardware needed for interface.

II. Making configuration diagram based on the end user (Railways) requirement and Planning of Serial communication based on configuration

Microlok-II Application software design:Step 1: Preparation of application logic for

loading it on to Microlok II CPU.Step 2: Based on application Logic designed,

VDU software design has to be done so that the Commands from VDU also executed similar to the conventional panel commands.Application Program Design:

Application Program written in the form of Boolean equations is a form of Interlocking Circuit based on IR relay interlocking design. All the relays used in conventional circuits are called as BIT when referred to Application Program.

The application program is written by using any Text Editor and it saved with file extension “PROGRAM.ML2” . Then this .ML2 file is compiled by using the Compiler supplied by Ansaldo, which results in three f i les P R O G R A M . M L L , P R O G R A M . M L P , PROGRAM.MLD when the written program is as per the Microlok – II syntax rules. MLD file is not needed since the same information is included in the MLL file. Therefore MLD is an option and not produced now.

“MLL” file is a listing file, which gives any errors, warnings, no. of BITs used, no. of time one bit used and Address selection for I/O cards etc. This also gives unique identification numbers called as “CHECKSUM” & “CRC” for particular station Application program. “MLP” file is a data file, which is loaded in memory of CPU of MLK II using MLK II Maintenance tool, supplied by Ansaldo.

Application Program consists of· Local I/O bit definition section· Serial bit definition section· Boolean bit definition section· Timer section· Log bit definition section· Constant Definition· System Configuration· Numeric section· Logic Section

Logic Section: It is one of the most important section in

which a designer should acquire sufficient knowledge and skill to become a good application program designer. This is the section which decides the interlocking and hence the safety of operations.

The symbols used for converting the interlocking circuit into the Boolean equations are:

8

SERIES ———— Star — *PARALLEL ———— Plus — +Back contact ——— Negation — ~Start Of Parallel Path —— (End OF Parallel Path —— )Bit Separation ——— ,End of Statement / Section —— ;

In addition to above symbols, the following are also used.

% followed by \ for multi lines commenting // for single line commenting /* followed by */ for multi lines commentingThe commented lines are not taken by

compiler during compilation process.

Now let us see some rules for writing the Boolean equations.

1. NV.ASSIGN statements are used for non vital logic Boolean equations.

2. ASSIGN statements are used for vital logic Boolean equations.

3. The compiler will generate a severe warning if an attempt is made to do an NV.ASSIGN to a vital bit.

4. An ordinary warning will be generated if an ASSIGN is used for a non-vital bit as a target.

5. A bit used in the output list of an assignment may be used for 50 front contacts and 50 back contacts. If need arises to use it for more than 50 assignments , then a repeater bit may be assigned first, then the repeater can be utilised again for 50 more assignments and so on.

6. The number of operators in a Boolean statement shall not be more 60 (like 45 contacts of Q series relays in a relay circuit).

7. In a relay interlocking circuit we will be able to show the conditions for execution of a function both on positive line as well as on negative line. But in Boolean equations all conditions are to be shown on side left to “TO” only.

ASSIGN CH1LR*CH2LR*S1A_DMTNNR*SH23NNR*(4OVSR+18NWKPR)*

(S3GNR*S3ASR*3_4TUNR+S3NRR) * (S3GNR+S3NRR) *(~S3GNR+~EGGNR)

* ~S3_SH21UYR1 TO S3NRR;

8 The double cutting cannot be shown as it becomes redundant in Boolean equations. The cross

protection is not required since physical wiring is not there between bits and the bits are virtual

relays.

ASSIGN S1UCR*~S1ASR*(~S1GNR+S1HR)*(13NWKPR*~S1UGR*

~S1UECPR+13RWKPR*S1UGR*S1UECPR) TO S1HR;

// S1HR STR = 5 MSEC

S1UCR ASPR1

S1S1UCRUECPR

S1UGRS1

GNRS1

HR

S1

R1 R2

N24

S1HR

UCRS113

NWKPR

13RWKPR

S1UGR

S1UECPR

S1ASR

GNRS33-4T

UNR UYR1S3-Sh21S3

GNRNRRS3

S3NRR

GNRS3

NRR

S3

R1 R2

EGGNR

S3ASR

S3GNR

Sh23NNR

S1A-DMTNNRCH2LRCH1LR

N24

S3NRR

4OVSR

18NWKPR

B24

8

9

9 In above equation S1HR is commented to remind the programmer to define S1HR as slow to release in Timer section as below.

S1HR: SET= 0: SEC CLEAR=5: MSEC;10 A Bit may be made slow to pickup or slow to release in Timer section. Like that 399 Timers can be

defined for a card file with time of 0, 500Msec,.....109 Min11 The commands from CCIP (conventional panel) as well as Operating PC (VDU) are to be executed

whichever is enabled by the operator at that moment.

NV.ASSIGN ((PANEL + ~SMKEY * ~PC_ON) * S1GN + PC * (CI_S1A + CI_S1B + S1RTRELR1 + S1SCR)) * ~S5GNR * ~S3GNR *~SH10GNR * WNCR TO S1GNR;

In above equation S1GN - Signal Button is pressed from conventional panel to pick up S1GNR in panel mode with SM key in or out.

In above equation CI_S1A or CI_S1B or S1RTRELR1 or S1SCR bits are sent to Microlok when VDU is

under use as defined in serial bit definition section.

CI_S1A bit is used to pick up S1GNR as per above Boolean equation in PC mode.

12 Sometimes, a bit sent from VDU may be used in more than two Boolean equations to fulfil the requirement. The Bit, CI_S1A used to pickup S1GNR is used once again to pick up respective UNR also as given below.

NV.ASSIGN (PANEL * DLUN + PC * (CI_S1A + CI_C1A + CI_SH21A)) * ~DMUNR * ~UMUNR * ~COMUNR * ~3UNR * ~27UNR * ~UDUNR * ~DDUNR * ~S3EGNR * ~S5EGNR * ~SH8EGNR * ~S4EGNR * ~S6EGNR * ~S30EGNR * ~S26EGNR * WNCR

TO DLUNR;13 For compilation of VDU, one file named .CSV is used. The file MLK_1STN_10.csv will be containing

the inputs and outputs of address 10 of serial bit definition section of application logic and they were arranged exactly in the same sequence as defined at address 10 of serial bit

P

S1

GNS5

GNR

SH 10

GNR

S3

GNR WNCRS1

GNR

SM KEY PC-ON

PC CI-S1A

CI-S1B

S1RTRELR1

S1SCR

PANEL

10

definition section . Then only the commands are correctly executed from VDU. The bit sent from VDU should be used as it is in the application logic like CI_S1A, S1RTRELR1, and S1SCR etc.

14 Sometimes a single Boolean equation may be written to assign to more than one target as shown below.

NV.ASSIGN (~PANEL * PC_ON + (PANEL * PC_RQ + ~PC_ON * ~PANEL) * FLASH) *CPS.STATUS TO PCKE, PCKE.OPSO, PCKE.MPSO;

15 When the system is initially switched on or during warm standby changing over, a time delay of 120 seconds is created to pickup all ASRs which are not in the approach of trains.

ASSIGN ~SH4HR.ISO * ~SH4_OFFECR.ISI * ~SH4UCR * (22ATPR.ISI * 20TPR.ISI *

(5TCPR + 20WNR.ISO) * (SH4UYR1 * SH4UYR2 * SH4UYR3 * SYSINITTMR + SH4JSLR * SH4JR) +

S H 4 A L S R )

TO SH4ALSR;

ASSIGN ~SH4HR.ISO * ~SH4_OFFECR.ISI * ~SH4UCR * 22ATPR.ISI * 20TPR.ISI (5TCPR + 20WNR.ISO) * ((SH4EGNR + CPSJR * 13ATPR.ISI) *SH4JBPR + SH4JSLR) * ~SH4ALSR TO SH4JSLR;ASSIGN C P S . S T A T U S J 2 * A L S R _ D N * ~ S Y S I N I T T M R

TO CPSJR;ASSIGN C P S . S T A T U S * ( C P S . S T A T U S . I S I + S Y S I N I T T M R )

TO SYSINITTMR; // STP 130 SEC

16 All vital output relays are read back and taken as non-vital inputs. Any mismatch occurs between vital output delivered and bit read back will pick up FCOR. There by the system goes for a RESET.

ASSIGN ~1DR.ISI * 1DR_F + ~1HR.ISI * 1HR_F + ~C1HR.ISI * C1HR_F + ~1BUR.ISI * 1BUR_F + ~2DR.ISI * 2DR_F + ~2HR.ISI * 2HR_F +

~C2HR.ISI * C2HR_F + ~2BUR.ISI * 2BUR_F + ~2CUR.ISI * 2CUR_F +~SH3HR.ISI * SH3HR_F + ~SH4HR.ISI * SH4HR_F + ~5DR.ISI * 5DR_F + ~5HR.ISI * 5HR_F + ~6DR.ISI * 6DR_F + ~6HR.ISI * 6HR_F

TO FCOR1;// STP 1 SEC

ASSIGN ( F C O R 1 + F C O R 2 + F C O R 3 + F C O R 4 ) * C P S . S TAT U STO FCOR;

// STP 500 MSECASSIGN ~ I V S L _ C O M O K J 2 * S Y S I N I T T M R + F C O R + L I N K FA I L

TO RESET; Initially CPSJR will be in pickup condition and make all JSLRs to pick up, thereby ASRs will pickup

provided other conditions are satisfied. After 130 seconds time delay, SYSINITTMR will pick up and stick thereby drops CPSJR.

17 The maximum Boolean statements (assign/nv.assign) per card file can be written is 4095. If the need arises more than this, one more card file may be employed.

Finally the complete wiring diagram based on the hardware (estimated) and configuration (decided) is prepared.

On successful completion of interface design, the application software design and VDU design, the application software is then compiled and .mlp file is uploaded into the CPU using maintenance tools supplied by Microlok-II, Ansaldo. VDU software is loaded onto operator PC. Then software simulation panel is made ready and FAT – Factory Acceptance Test is carried out to satisfy TOC supplied by Railways. On satisfactory completion of FAT, further SAT- site acceptance test is carried out and the station is commissioned for train operations.

11

BRT on Rail Corridors - ColomboShri V C D Jayasekara

Sri Lanka Railway

Background:Traffic congestion at Colombo and around is

mainly resulted by the private vehicles. Vehicles entering Colombo city each day has been 250000 at year 2012 (Ref. “Soon you’ll be speeding at 15 kmph on Colombo roads,” – by Mirudhula Thambiah, the Sunday Times on 12 Feb 2012) and now obviously might have gone way passing the figure. The figures in the article says 225000 vehicles are private owned of the total.

Traffic congestion could be solved in three main ways.

1. Improving Infrastructure – facilitate the vehicles entering to the Colombo by improving the number and the quality of the access means, then distribution of the vehicles in an organized manner inside the city.

2. Strategically reducing the number of vehicles entering into the city – This involves tasing the vehicles, uplift the public transport and encourage people to use them instead driving on their own, imposing regulations on number of passengers for public vehicles, etc.

3. Reducing the necessity/demand to travel to capital through decentralization policy.

Option three appears to be a long term solution and need policy decision at top government level, which may create a political background for the issue. Also this can result an impact of the economy of the country. Option one also need heavy capital in implementation. While Colombo desperately in the requirement of a rapid transit option, the fact remains that Sri Lanka being a developing country is not in a position to invest huge capital needed for e l e vate d ro a d s , p ro v i d i n g e l e c t r i ca l infrastructure to rapid transits, investing on specially designed passenger caries etc.

Therefore in this document it is expected to propose an alternative transit measure under option two which does not need much investment but still need some strategic decisions at the top management of transportation sector.

PossibilitiesUnder the above possibilities listed at option

two, the popular topic is to reduce the number of private vehicles entering the city byu means of making the public transits popular. Thus Rail and Road public transport mediums need to be re-analyzed to deliver the optimum service in a strategic way. Then it is required to explore the demand, possibility and cost for the alternatives.

If the peak traffic which requires most attention in this regard is considered, people reluctant to get in to the Public Road Transits, mainly due to two facts.

Firstly the main target, get into the work place in time. Normally by experience it has become a fact that even the medium distance travellers are paying more time at on the way stops than the actual travel time. Sometimes this become three times of the actual travel time which makes passengers get into the transits three times earlier than the required which solely would become the reason for the unpopularity of the public transport systems. But still this could not be solved by using private vehicles, because simply the same thing will repeat on the way.

Then comes the second factor, comfort and comfortable environment. Both does not normally experienced at Public Transport systems but easily fulfilled by the private vehicles. This becomes even complicated when the crew behaviours, air and noise pollution, space issue and neighbour passengers are considered.

Whereas Rail Transit which become obviously the fastest between destinations while all other

12

draw backs too appear at road transits are minimized in comfort concern. Rest also could be overcome with a minimum effort. Therefore in this document it is presumed that passengers specially the daily travellers prefer Rail transit if properly facilitated.

ProposalSri Lanka Railways at present is not in a

position to invest highly on developing infrastructure for catering more trains. But peak time train service is running at an excessive load factor despite of the fact that railway track utilizatin is at a very high level in specially Main Line, Negombo Line and Coast Line. Then if large scale investment is not permitted the obvious choice is to to utilize whatever posses at optimize level.

Therefore the land asset and “Right of Way” asset is proposed to be utilized in following manner.

1. Sri Lanka Railways has land reservations on all its main corridors mentioned earlier and easily can construct a road way parallel to the existing rail track in suburban areas.

2. A Bus Rapid Transit can be launched on that roadway at a minimum cost that is investing on luxury or semi luxury or even buses without seats/with less number of seats.

3. BRT shall run exclusively in the direction of the peak hour traffic flow in the morning and evening.

4. BRT shall have the “Right of Way” priority at the level crossings in a frequent basis.

ExplanationThe first requirement to be met by the

transport mediums would be the reaching destination on time and safely. In this concern Sri Lanka Railways enjoys its freedom of passage that no other obstructions or limitations experienced on its way which is a common hassle needed to be overcome by all other transport means. No traffic congestions unless created by their own trains and systems. On the other hand this option is extremely difficult when roadway is considered b e c a u s e i t d o e s n o t h a v e t h e

freedom for creating the land space required for running a BRT due to townships which causes much inconvenience to public and commercial activities along the road. When railway passage is concerned most of the requirement is already prevailing free of nobodies touch except for the Kelani Vally line and rest could be recovered from encroachments without much effort and inconvenience to public. Commercial activities will not be or hardly be come on way. What rail transport privileged at reaching the destination at shortest time is speed and passage. Therefore why not applying the same blessings to a BRT. BRT can enjoy an exclusive passage. BRT at the same time can also enjoy the speed which will be explained latter under Right of Way.

When considering the type of busses to be engaged, it’s very important to stick and focused in to the main requirement expected. That’s reach the destination early at a reasonable comfort level. And also this is proposed to overcome the infrastructure constrains of Railways to provide more trains. Constrains would be implied by lack of capital for putting up a new track and rolling stock plus other systems. Hence the busses in BRT would just be adequate to create the train atmosphere with an additional margin of comfort, may be seen as a train on tires or a train on road. BRT should be so planned to take the burden out of the train and simulate the same safe and comfort environment at busses. This would become more beneficial if made availed at the same train ticket or seasons. Passengers shall have the freedom to just make the selection between train and bus both would be made available at either side of the same platform perhaps or two levels at the same railway station. Therefore comfort at a certain level would be maintained rather than keeping the service unaffordable for general public in the sense of introducing luxury busses. Busses with fewer seats may adequately full fill the requirement.

Operation of the BRT if maintained of the demand direction of the peak hour traffic would result the rail operator to invest minimum for infrastructure and at the same time some revenue generation may also be possible. The

13

requirement if focused back was to cater the excessive traffic at peak hours. Therefore if BRT planned to be operated in peak hours;

1. Less number of busses will be required and up and down fleet will be effortlessly arranged in a self manner at required terminal.

2. Railway can use the roadway as a maintenance access way for the rail track which can increase the effectiveness of maintenance as at the moment this is issue is also a burden for railway operators all over the world because unavailability of access roads force operators to carry on the maintenance using specific rail vehicles, some time creating operating restrictions.

3. Railway can optionally open the roadway for general traffic in off peak hours with an imposed charges thereby a revenue generation would also be possible.

4. Infrastructure such as electricity masts for an electrically operated BRT could also be achieved with a minimum capital.

Right of WaySri Lanka Railways has right of Way for its

passage which would become the greatest advantage in the BRT operation under the proposal. BRT can also enjoy the Right of Way being a sub or assisting service of the Railway itself and could deliver a faster service that it would perform on a road way in concern of railway crossings. At the same time Right of Way will cut off additional costs for flyover like crossing arrangements, which would likely to incur if the BRT happened to be planned on a roadway.

When operations constrains to BRT is considered the speed could come down at mainly two reasons; due to stopping schedule, of which operator have the discretion on planning and crossing of main roads and the possible delay at level crossings. Since the BRT will operate on a parallel line with the existing railway line, BRT has the benefit of utilizing the closing time of level crossings, for trains operating on railway line disregard of the direction. BRT operates in a single direction, therefore could acquire the closing time of level crossings trains in both

directions with a signalling system designed with special customized features.Enhancements

Despite of the all plus points of BRT operating in the railway corridor, the facts remain that suggested Railway reservation is never meant for a bus operation and more to that a BRT can ever replace a train. If capital investment constrains not prevailed an additional railway line would have been the appropriate optimization of the reservation. Therefore the timely conversion of the BRT roadway to a railway track also need to be considered.

In this case unlike in most other cases not only this solution has provisions for conversions, it makes the later construction of a rail track more feasible. Lands already acquired and prepared, halfway arranged Electricity and other infrastructure, halfway arranged stations terminals makes any future conversion halfway done.Conclusion

Therefore considering all above facts the best option will be designing a BRT run on the railway corridor parallel to trains as supporting service, with a preplanned future track for railway operation. This can make the transform easier and BRT will also be gained by a better organized, more than adequate infrastructure.

At the same time to make the proposal more meaningful following suggestions are also recommended.

1. Find out possible ways and means to attract the road users specially the daily travellers using private vehicles.

2. Encouragements given to passengers by arranging parking facilities at the rail terminals so that they can drive the private vehicle to the railway station and from there to BRT or train depending on the situation and again pick up at the destination by a suitable office transport arrangement.

Finally the BRT shall be operated more like a part of a train running on roadway but not as conventional BRT.

14

Medha EI- Application Data generation ProcessK.Venkatramana Reddy

GM (S&T). Bangalore Metro

Introduction: As we are all aware , Electronic Interlocking is

being introduced in big way in Indian Railways and EI equipments are manufactured by different vendors. Each vendor is having his own hardware design within the framework of RDSO specification. Application design process also varies from vendor to vendor. In this paper an attempt is made to explain the application data generation process of Medha EI system based on their training imparted at IRISET/SC.

Medha Application data design process consists of three stages.

· Application data generation· VDU design· Field Simulation Panel design and testing

using interlocking simulator

Application data generation process is explained in this article.

For application data generation Medha has developed a software tool called “YDC App Data Generation”.

The inputs required for generating the Application Data are

1) Interlocking logic written in text file format ( “BETEquations.txt”)

2) System Hardware Configuration details.

Interloking Logic Design:The Interlocking logic shall be designed based

on the following base input documentsStation SIP(Signalling Plan), Table Of Control & Panel Diagram.

Boolean logic is used for writing interlocking logic and it will be written in text file format using note pad. The following rules shall be followed while writing the Interlocking logic.

The following example illustrates about writing boolean equation

The Interlocking Logic Equation for the above circuit shall be written as shown below:

S160TSR = 520TPR & ((S160ASR & !S160T540NRR) # S160TSR);

Following sequence is to be followed while writing application logic.

Button

NNR/NLR

Point Circuit

UCR

ASR

JLSR,UYR

OVSR,OVJLSR

UGR,HR,DR

LC gate, C/H

Block Indication Equations Should Start with

SMKEYINKE Equation.i .e. SMKEYINKE equation separates

interlocking equations and indication equations.

Operator Description = Assign & Logical AND

# Logical OR

! Used for representing Relay back

contact

; Every logic equation shall end with

Semicolon

( For starting the parallel path

) For ending the parallel path

15

Standard relay nomenclature to be used is as follows.

As per the above guidelines application logic shall be written using notepad and shall be named as “BETEquations.txt”

System Hardware configuartion details:Based on SIP and Panel diagram, assess the

requirement of Vital and non Vital Inputs and outputs keeping provision for spares. This information is required for assessing Object Controllers(Ocs) and PP(Panel Processor) cardsWhile assessing the OCs and PP cards following is to be kept in mind

Each OC can have maximum 5 input WFMs and 3 Output WFMs.Each input WFM can cater for 8 Vital inputs and each output WFM can cater for 8 Vital Outputs. Each PP module can have maximum 11 input cards and 38 output cards. Each PP input card can cater for 64 non vital inputs and each PP output card can cater for 64 non vital outputs.

After assessing the requirement of OC and PP cards, allocate Vital Inputs and outputs WFM wise (OC1 WFM 0 to 7, OC2 WFM 8 to 15 and so on) in an excel sheet which will be useful in application data generation process.

Fig. Sample WFM allocation chart

Like wise allocate Non vital Inputs and outputs also PP card wise.

PP Inputs. (each card in 8 rows and 8 columns = 64).

First row should contain only keys. First the available KEYs shall be allocated from the list balance will be dummy keys which can be used at a later date if required. Balance can be allocated to various panel inputs as indicated below which will be useful in application data generation process.

Fig. Sample panel input allocation chartPP Outputs. (each card in 8 rows and 8

columns = 64).First two row are reserved for counters and

buzzers. Allocation of Counters will start from 1, 2 ... and buzzers will starts from 16,15..... Balace will be shown as spare. Balance can be allocated to various panel outputs as indicated below which will be useful in application data generation process.

Fig. Sample panel output allocation chartThese Excel sheets will be useful in application

data generation process. After completion of the above, install “YDC App Data Generation Setup.exe” a software tool developed by Medha shall be installed in the C drive of the PC.

It is having four parts.Fitter Module : This module generates the

Application data based on BETEquations and Inputs provided such as H/W Configuration & I/O correspondence details.it will give the Output files of Specific Station “Appliation data i.e Fitter .Bin File” & Database for VDU, MT i.e Fitter.Mdb”.

xRECR Signal Red Aspect.

xHR Signal Yellow Aspect Control.

xHECR Signal Yellow Aspect.

xDR Signal Green Aspect Control.

xDECR Signal Green Aspect.

xHHR Signal Double Yellow Aspect Control.

xHHECR Signal Double Yellow Aspect

xNWR Point Normal Output Control.

xNWK1R Point Normal Detection. xRWR Point Reverse Output Control.

xRWK1R Point Reverse Detection.

xJLSR Timer Initiating relay .

xJR Timer relay .

16

CRC Verification : After Generation of Application data, the tables check sum will be verified by using CRC Verification.Tables check sum and application data checksum shall be the same.

Reverse Compilation: Through Reverse Compilation with the final Application data, files will be generated which will compared with the initial files using compare

Compare : Finally for Data verification both the Final Application Data files & Reverse Compilation files will be compared and the result should be identical.

Copy the application logic program file (BETEquations.txt file) into the “YDC App Data Generation” folder in the C Drive. Run the Application Data Generation Tool by double clicking the icon. A window will appear on the screen as shown below .

Select the fitter and click Run button. A message box related to grouping of the relays will appear as shown below.

If the program is being run for the first time then relay grouping is must. For subsequent modifications based on requirement either yes or No is to be selected. The following procedure explains about relay grouping.

Relay Grouping :

Fig. Various columns available in Relay Grouping menu

In EI the inputs, outputs and the internal variables used for computation of Interlocking Logic are referred to as logical relay variables.These relays will not exist physically except field inputs and field outputs. But they are referred as relays due to their equivalent or similar functionality to the relays in the Relay based Interlocking.The relay variables used by the System for Interlocking and Indication computation have been categorized as follows:

PP Input Relays: The System receives the status of the keys and buttons/knobs in the CCIP as input. These inputs are stored as Panel Input relays. These relays are not physically present, but are logically represented as a variable whose value reflects the relay contact state.

PP Output Relays: The Variables, which store the Panel outputs like indication lamp status (Lamp On = Relay picked up, off = Relay Dropped), Buzzer and Counter output values, are referred to as PP output/Indication Relays.

Timer Relays: The timer initiating relays(JLSR) are picked-up to start a timer for the corresponding time interval. The timer relays(JR) are picked up when the set time interval is elapsed.

External Relays: The Relays that are driven by the system (Output Relays), and the relays, whose contacts are read into the system (Input Relays) are being referred as External Relays.

The Output relays transmit the commands to drive the various functions. The Input Relays reflect the status of the field functions. These relays are also referred as field input or field output relays.

17

Additional Relays: Variables used to store the intermediate relay states while computing the Boolean equations are called additional relays. These relays are not present in the interlocking relay circuits/equations. But while executing the relay circuits as Boolean Equations, some intermediate states need to be stored. These states are stored in additional relay variables. These are System generated relays during compilation and normally starts with b_.

Internal Relays: The other relays, which are used in the relay circuits while designing the interlocking logic, but are not physically present, are being referred as internal relays.

While making Relay grouping, nomenclature used in “Interlocking Equations” only to be used. If any other information is given to the tool it will not understand the values .

Fig. Sample Relay groupingThere are two ways of doing relay grouping

By entering manually in each group ending with generic(group) names like TPR, DECR, HECR, NW1KR , _P, _KE, _W, _R etc.

Eg. If DECR is entered as external input relay all relays/variables ending with DECR will be grouped under external input relays(S2DECR, S3DECR,S12DECR etc.)

By using drop down menu where all the variables used in BETEquation will appear in drop down menu and to be selected manually. But this will be cumbersome and normally first method is used.

After completion of the relay grouping save the changes for proceeding to the next step.

Hardware(System) configuration :

The System Configuration Setting Window facilitates to enter the system configuration details for the current yard.

a) First tab facilitates to enter WFM Configuration.

b) Second tab facilitates to enter PP Input (Button/Key Inputs) Information.

c) Third tab facilitates to enter PP Output ( I n d i c a t i o n s / C o u n t e r s / B u z z e r s ) Information.

d) Fourth tab facilitates to enter Timer details.e) Fifth tab facilitates to enter the Information

regarding Relays to be picked up at power ON.

f) Sixth tab facilitates to enter Other Information.

g) Seventh tab facilitates to enter function details.

WFM configuration :All External Input and External Output Relays

allocation will come under WFM Configuration. While updating WFM configuration first indicate the no. Of WFMs that are required.

Each OC can cater for 5 Input Cards and 3 Output cards. (Total 8 cards)

OC0-WFM0 to WFM7OC1-WFM8 to WFM15OC2-WFM16 to WFM23 and so on.For example if a particular station requires 12

I/P WFMs and 7 O/P WFMs , 3 OCs are required. Let us assume that we want to distribute the

WFMs OC wise as follows:OC0- 4 I/P WFMs and 3 O/P WFMs(1 Spare)OC1- 4 I/P WFMs and 2 O/P WFMs(2 Spare)OC2- 4 I/P WFMs and 2 O/P WFMs(2 Spare)Total: 12 I/P WFMs and 7 O/P WFMsNo. of WFMs=(No.of OCs X 8 – No. of Spare

WFMs of last OC).In the present case no. of WFMs that need to

be entered is 3 X 8 – 2 i.e 24-2 =22 22 rows will appear with 0 to 21 in WFM no

column

18

WFM connected (Input/Output) or not connected state shall be decided in the second column.

By default all the WFM’s connected state is displayed as “Not Connected” only, so there will not be any access given to Relay0 to Relay7 cells of these “Not Connected” WFMs.To change the connected state of a WFM, click on the corresponding cell in second column so that a drop down arrow will appear at the right side of the cell. Further click on the drop down arrow so that a drop down list will appear below the selected cell. In that three states “Input”, “Output” and “Not Connected” are displayed. Select one of these three options provided as shown below.

Fig. WFM ConfigurationUsing dropdown menu assign WFMs as

Input/Output/Not connected as indicated below.

WFM 0 to 3 as Input

WFM 4 to 6 as Output

WFM 7 as Not connected

WFM 8 to 11 as Input

WFM 12,13 as Output

WFM 14,15 as Not connected

WFM 16 to 19 as Input

WFM 20,21 as Output

WFM 22,23 as Not connectedAfter assigning WFMs, assign each input/output of WFMs through drop down menu which will appear based on the relay grouping. All external input relays will appear in drop down menu while assigning input WFM.As and when a particular input is assigned that will disappear in drop down list .

All external output relays will appear in drop down menu while assigning output WFM. As and when a particular output is assigned that will disappear in drop down list .There is a provision given to the user to interchange two allocated

relays by using a blank relay (——) in the relay drop-down list.

Complete all external I/O assignment as per the vital I/O Calculation in the WFM modules of the OC based on excel sheet prepared initially.

Panel Processor I/P Configuration:

VDU Connectivity status options: Case-1: If Yes “Connect” to be selected. Case-2 : If No - “Not connect” to be defined.

Selection of Interlocking Type: 1.If Panel Interlocking i.e Knobs — “ PI” to be

selected 2.If Route Relay Interlocking i.e Buttons — RRI

to be selected

Each PP input card can read 64 inputs (i.e. 8 Rows)

First column shows the serial number starting from zero. Columns of Relay1 to Relay8 will display unallocated Button Inputs list when they are selected.First row should contain only keys. First the available

KEYs shall be allocated from the list balance will be dummy keys which can be used at a later date if required

After allocating KEYs in the first row, then from the next row onwards, unallocated Button Inputs will be displayed in the drop down list. Now allocate all the Panel Inputs in the appropriate positions as per Excel sheets prepared for Panel Inputs. To update the Button Input Allocation, press the Update Button, so that this allocation will be stored in the background and will retrieved whenever the PP Input tab window is selected. To change the position of the allocated relay then use the blank relay (——). First select the relay cell, which is to be exchanged, then from the list select the blank relay, so that earlier relay comes in to the list and blank relay will appear in

19

that relay cell. Now re allocate this relay wherever it should be positioned.

User can clear all the relays that are allocated by pressing the button Clear Window. This will be used when all the relays needs to be interchanged. After allocating all Button Inputs, the window appears as shown below.

Fig. PP I/P configurationAll Operator Panel Outputs such as Buzzers,

Counters and indications will come under this tab window.

Each card consists of 64 O/P st nd1 and 2 row (i.e 16 O/P ) to be dedicated for

Counters & Buzzer functions, then O/P bits can be allocated.Number of rows will be selected depending on the number of Panel Output Relays used in the Yard, and also there will be a provision given to the user for modifying the number of rows

Allocation against each output will be done by selecting the output from dropdown list which will appear when a cell is selected. User needs to do the allocation of the indications as per Excel sheets prepared for Panel Outputs.

Once any relay is selected from the list then the same relay will disappear from the relay list and comes into that cell. Press update button after allocation of all panel O/P.After allocating all Indications, the PP Output window appears as shown below

Fig.PP O/P ConfigurationTimer Configuration :Timer tab window is categorized into two

groups,

Timer Initiating Relay Configuration and Timeout for IO Correspondence.

Though there are various categories of timer initiation relays indicated in the tool at present, allocation of timer values is done by selecting normal signal cancellation time.

When the edit button against normal signal cancellation time is pressed all the timers will appear in dropdown window and timer value can be assigned against each timer . Do not press update button as timer values are different.

Time out for IO Correspondence:In Timeout for IO Correspondence, Single

Aspect IO Correspondence Time, Two Aspect IO Correspondence Time, Three Aspect IO Correspondence Time, Four Aspect IO C o r r e s p o n d e n c e T i m e a n d P o i n t I O Correspondence Time shall be entered.These timings can be in ticks or seconds, user can select either ticks or seconds. One tick = One cycle time ; one second = 3 ticks. This will be used for error reporting.Pickup Relay at Power On:

As per the Zonal Railway Standard Practice at Power on Pick relays can be initiated. At present it is set to Zero

Fig. Timer ConfigurationOther functions :

EIC Connect Status, CTC Connect Status, EIS Installation Address and Application Data Version shall be entered under this tab window. This information will be stored in application data, which will be used by the system.

20

EIC & CTC are the future use. Set them as “Not connected” as a default.

EIS Installation address shall be in the range of 0 to 65535 (0 to FFFF in hex) and Application data version shall be in the range of 0 to 255 (0 to FF in hex). Enter only the Hex value.

EIS Installation ID will be mentioned for corresponding Station

Application Data version should not be changed and by default it should be “0010” i.e 1.0 Version

After entering the values click on update button to save the data.

At any point by pressing the clear window will clear the data that is enteredFT Details :

Function Name, Function Type & Aspects needs to be entered under this tab.

User shall enter all the function details manually based on the Signalling Interlocking Plan

Function details, which will be entered in this tab, will be used for generating the IO correspondence.

After updating all the Hardware configuration details select the “Update” Button for updating the status of records.Creating Lookup Tables :

After updating all the details select “Create lookup tables” button for creating the tables and wait till the tables are created .

A message will appear “Do You want to close the application?” Press “ Yes” to exit the application. After all the process completion YDF fitter yard specific files will be stored in the folder named “ YDC_Fitter_files.

Application Data will be generated by the name “Fitter_BinaryFile.bin” in the path “C:\YDC App Data Generation\YDC_Fitter_Files\”.

This Fitter_BinaryFile.bin file is the Application Data for the specific station, which will be programmed into the MEI633 to perform the interlocking of the station. Along with the Application Data, Lookup Tables are also generated in the same path by the name “LookupTables.txt”. Lookup tables consist of all the system configuration details for user understanding.

Data Verification Process :After generation of application data select the

CRC vereification and press RUN.After Generating the Checksum a message box

window displays and shows that “Do you want to verify the data?” Now click on “YES” for viewing the generated data.

All tables Check Sum will be displayed in “table check sum .txt file” Total Check Sum in the tabel and that of fitter binary file should be same. If there is any difference , once again data need to be verified. Reverse Compilation:

Once Application data generated Select the Reverse Compilation option and click on Run button for the Reverse Compilation execution. After Completion of Reverse compilation process a message box window displays and shows that “Reverse Compilation is completed Compare the file” then Select “OK” Finally now select the option to “ Compare Files “ then click on “Run” for comparision of Reverse compiler generated files.

The following files one by one from each folder

Both the files should match with each other and the message “Identical” shall display in normal course. If files are not Identical the comparison window will open and shows the difference between them for comparision and verification. After rectifying the defects again program is to be run till the above files match with each other. After compilation is over binay file is to be uploaded to the system.

Conclusion: The above procedure explains briefly about the steps involved in application data generation which is dependent on the application data generation tool developed by Medha. Readers should note that any subsequent changes to this tool by Medha will have effect in the data generation process. Some of the tables generated in this process are used in VDU design and Field simulation design.

Folde

r/File

Application data version

files

YDC_Fitter_

Files

1

Fitter_BinaryFile_Indicati

onEquations.txt FinalIndicati

onsEqs.txt

2 Fitter_BinaryFile_Interloc

kingEquations.txt

FinalInterloc

kingEqs.txt

3 Fitter_BinaryFile_System

configurationTables.txt

LookupTabl

esData.txt

ìððÐðÇóÑð

Gyandeep

IRISET21

òÎÃðóÚð £Ã¨öîæ¾ ̈ îðÚðáòÐðæÑððÇÐð ̈ ÷î òâð¦ ýòÜçð÷¾ ̈ îð÷ äðóâÀ çð÷ çðÙÙððòÐðÃð

òÇ. 23.10.2013 ¨îð÷ ¨÷üîÍóÚð ÚðõÐððÐðó òµðò¨îÃçðð ¡ÐðôçðüÏððÐð çðüçÆððÐð Ùð÷ü Ðð±ðÜ Üð¸ðØððæðð ¨îðÚððáÐãðÚðÐð çðòÙðòÃð ¨îó ×ðø¿¨î ¡ðÚðð÷ò¸ðÃð ¨îó ±ðýá Æðó. ýçð ×ðø¿¨î Ùð÷ü ýòÜçð÷¾ ¨÷î òÐðÇ÷äð¨î, £Ñð ÙðôÜðòÏð ãð ¡ðµððÚðá òçð±ðÐðâð, Üð¸ðØððæðð ¡òÏð¨îðÜó, Üð¸ðØððæðð ¡ò³ðêð¨î ¦ãðü Üð¸ðØððæðð çðèðÚð¨î ±ß÷À | Ðð÷ Øðð±ð òâðÚðð. ýçð ×ðø¿¨î Ùð÷ü èøÇÜð×ððÇ/òçð¨üîÇÜð×ððÇ Ðð±ðÜÎÚð Ùð÷ü òçÆðÃð ¨÷üîÍóÚð çðܨîðÜó ¨îðÚððáâðÚðð÷ü Ùð÷ çð÷ òèüÇó Ùð÷ü òÎÃðóÚð £Ã¨öîæ¾ ¨îðÚðáòÐðæÑððÇÐð ̈ ÷î òâð¦ ýòÜçð÷¾ ̈ îð÷ äðóâþÀ ÑßÇðÐð ̈ îó ±ðýá. ¡ÏÚðêð ¦ãðü òÐðÇ÷äð¨î, ̈ ÷üîÍóÚð ×ððÜðÐðó ̈ öîòæð ¡ÐðôçðüÏððÐð çðüçÆððÐð, èøÇÜð×ððÇ ̈ ÷î ̈ îܨîÙðâðð÷ü ÎðÜð ÑßÇÄð Úðè äðóâþÀ òÐðÇ÷äð¨î/ýòÜçð÷¾ Ðð÷ ÑßðÑÃð ̈ îó.

òèüÇó ̈ îðÚðáäððâðð ̈ îð ¡ðÚðð÷¸ðÐð

çðÙðÚð-çðÙðÚð ÑðÜ ýòÜçð÷¾ ̈ ÷î ̈ îòÙðáÚðð÷ü ̈ îð÷ Üð¸ðØððæðð òÐðÚðÙðð÷ü ̈ îó ̧ ððÐð¨îðÜó Ç÷Ðð÷ ÃðÆðð ̈ ÷üîÍ çðܨîðÜó ̈ îÙðáµððòÜÚðð÷ü ¨îó çðüãðøÏððòÐð¨î ×ððÏÚðÃðð ¨îð÷ ¡ãð±ðÃð ¨îÜðÐð÷ ¨îó Çöòæ¾ çð÷ òÇ. 20.12.2013 ¨îð÷ ýçð çðüçÆððÐð ¨÷î çðØðó òâðòÑð¨î ãð±ðóáÚð ¨îÙðáµððòÜÚðð÷ü ¨÷î òâð¦ Üð¸ðØððæðð ¡òÏð¨îðÜó/ýòÜçð÷¾/òçð¨üîÇÜð×ððÇ ÎðÜð ØððÜÃð çðܨîðÜ ¨îó Üð¸ðØððæðð ÐðóòÃð ¦ãðü òÐðÚðÙð ÃðÆðð çðüãðøÏððòÐð¨î ÑßðãðÏððÐð òãðæðÚð ÑðÜ òèüÇó ̈ îðÚðáäððâðð ̈ îð ¡ðÚðð÷¸ðÐð ò¨îÚðð ±ðÚðð.

Ü÷âð Ùðüëðó Üð¸ðØððæðð ܸðÃð ÑðǨî ÑßðÑÃð

çðüçÆððÐð Ùð÷ü Üð¸ðØððæðð òèüÇó ̈ ÷î Ñß±ßðÙðó ÑßÚðð÷±ð ̈ ÷î òâð¦ òÐðÜüÃðÜ Ùðð±ðáÇäðáÐð ¡ðøÜ Ñß÷ÜÂðð Ç÷Ãð÷ èô¦ Üð¸ðØððæðð ̈ ÷î çðôµððÞ ̈ îðÚððáÐãðÚðÐð çðôòÐðòêµðÃð ̈ îÜÐð÷ ÃðÆðð çãðÚðü Üð¸ðØððæðð Ùð÷ü £Ã¨öîæ¾ ̈ îðÚðá ̈ îÜÃð÷ èô¦ çðØðó ¡ÏðóÐðçÆð ¡òÏð¨îðòÜÚðð÷ü / ̈ îÙðáµððòÜÚðð÷ü ̈ îð÷ Ñßð÷ÃçððòèÃð ̈ îÜÐð÷ ̈ ÷î £ÑðâðêÚð Ùð÷ü ýòÜçð÷¾ ̈ ÷î òÐðÇ÷äð¨î åó çðÃÚð÷ÐÍ ̈ ôîÙððÜ ̈ îð÷ Ü÷âðãð÷ ×ðð÷Àá Ðð÷ Ü÷âð Ùðüëðó Üð¸ðØððæðð ÑðǨî çð÷ çðÙÙððòÐðÃð ò¨îÚðð. òÇ. 12.11.2013 ̈ îð÷ òÐðÇ÷äð¨î Ùðèð÷ÇÚð Ðð÷ Ü÷âðãð÷ ×ðð÷Àá ̈ îðÚðáðâðÚð Ùð÷ü Úðè ÑðǨî ÑßðÑÃð ò¨îÚðð.

ýòÜçð÷¾ Üð¸ðØððæðð ̈ îðÚððáÐãðÚðÐð çðòÙðòÃð ̈ îó 129 ãðóü ×ðø¿¨î òÇÐðüð¨î 26.12.2013 ̈ îð÷ çðüÑðÐÐð

òÇÐðð¨î 26.12.2013 ̈ îð÷ òÐðÇ÷äð¨î/ýòÜçð÷¾/òçð¨üîÇÜð×ððÇ ̈ îó ¡ÏÚðêðÃðð Ùð÷ü Üð¸ðØððæðð ̈ îðÚððáÐãðÚðÐð çðòÙðòÃð ̈ îó 129ãðóü ×ðø¿¨î ¡ðÚðð÷ò¸ðÃð ¨îó ±ðýá, ò¸ðçðÙð÷ü Üð¸ðØððæðð ¨îðÚððáÐãðÚðÐð çð÷ çðü×ðüòÏðÃð òãðòØðÐÐð ÙðÇð÷ü ÑðÜ µðµððá ¨îó ±ðýá. ¡ÏÚðêð ¦ãðü òÐðÇ÷äð¨î Ùðèð÷ÇÚð Ðð÷ òçðÃðü×ðÜ 2013 ¡ðøÜ Ððãðü×ðÜ 2013 Ùð÷ü ¡ðÚðð÷ò¸ðÃð ªîÙðäð: Üð¸ðØððæðð çðÑÃððè ¡ðøÜ ãððòæðá¨î òÇãðçð, çðÃð¨áîÃðð òÇãðçð ¡ðòÇ ¨÷î çðÒîâð ¡ðÚðð÷¸ðÐð ¨÷î òâð¦ çðüÃðð÷æð ãÚð©Ãð ¨îÜÃð÷ èô¦ ¨îèð ò¨î çðØðó ¡òÏð¨îðÜó ¡ðøÜ ̈ îÙðáµððÜó Üð¸ðØððæðð çðÑÃððè ̈ ÷î ÇðøÜðÐð òãðÙðð÷òµðÃð òèüÇó ¾÷ÙÑâð÷¾ ÑðôòçÃð¨îð ̈ îð £ÑðÚðð÷±ð ̈ îÜÃð÷ èô¦ èÜ òÇÐð òèüÇó Ùð÷ü ̈ ôî¶ Ðð ̈ ôî¶ ̈ îðÙð ¡ãðäÚð ̈ îÜ÷ü.

çðØðó ØððÜÃðóÚð Ü÷âðð÷ü ̈ ÷î ¡òÏð¨îðòÜÚðð÷ü ¡ðøÜ ̈ îÙðáµððòÜÚðð÷ü ̈ ÷î òâ𦠡âð±ð-¡âð±ð “¨üîÑÚðõ¾Ü ÑðÜ ÚðõòÐð¨îð÷À

¡ðÏððòÜÃð òèüÇó ̈ ôüî¸ðóÚðÐð ÑßòäðêðÂð” Ñðð¿þÚðªîÙð ̈ îð ¡ðÚðð÷¸ðÐð

òÇÐðüð¨î 24.02.2014 çð÷ 28.02.2014 Ãð¨î ¡òÏð¨îðòÜÚðð÷ü ¨÷î òâ𦠨üîÑÚðõ¾Ü ÑðÜ ÚðõòÐð¨îð÷À ¡ðÏððòÜÃð òèüÇó ¨ôüî¸ðóÚðÐð ÑßòäðêðÂð Ñðð¿þÚðªîÙð ̈ îð ¡ðÚðð÷¸ðÐð ò¨îÚðð ±ðÚðð Æðð, ò¸ðçðÙð÷ü òãðòØðÐÐð êð÷ëðóÚð Ü÷âðð÷ü ̈ ÷î 9 ¡òÏð¨îðòÜÚðð÷ü Ðð÷ Øðð±ð òâðÚðð.

òÇÐðüð¨î 24.03.2014 çð÷ 28.03.2014 Ãð¨î çðØðó ØððÜÃðóÚð Ü÷âðð÷ü ̈ ÷î ̈ îÙðáµððòÜÚðð÷ü ̈ ÷î òâð¦ ̈ üîÑÚðõ¾Ü ÑðÜ ÚðõòÐð¨îð÷À ¡ðÏððòÜÃð òèüÇó ¨ôüî¸ðóÚðÐð ÑßòäðêðÂð Ñðð¿þÚðªîÙð ¨îð ¡ðÚðð÷¸ðÐð ò¨îÚðð ±ðÚðð Æðð, ò¸ðçðÙð÷ü òãðòØðÐÐð Ü÷âðð÷ü ¨÷î 38 ¨îÙðáµððòÜÚðð÷ü Ðð÷÷ Øðð±ð òâðÚðð.£©Ãð Ñðð¿þÚðªîÙðð÷ü Ùð÷ü £Ðè÷ü ¦Ùð¦çð ¡ðûòÒîçð ¨÷î çðØðó Ñðèâðô¡ð÷ü ¨îó ¸ððÐð¨îðÜó Çó ±ðýá. ¨üîÑÚðõ¾Ü ÑðÜ òèüÇó ýÐðòçªîѾ ̈ îó-×ðð÷Àá ̈ îó ̧ ððÐð¨îðÜó Ç÷Ãð÷ èô¦ ̈ îó-×ðð÷Àá ÑðÜ ÑßòäðêððòÆðáÚðð÷ü ̈ îð ¡ØÚððçð ̈ îÜðÚðð ±ðÚðð, Ãððò¨î ãð÷ òèüÇó ¨ôüî¸ðóÚðÐð Ùð÷ü çðêðÙð ×ðÐð çð¨÷üî.

ýòÜçð÷¾ Üð¸ðØððæðð ̈ îðÚððáÐãðÚðÐð çðòÙðòÃð ̈ îó 130ãðóü ×ðø¿¨î òÇÐððü¨î 21.03.2014 ̈ îð÷ çðüÑðÐÐð

òÇÐðüð¨î 21.03.2014 ̈ îð÷ òÐðÇ÷äð¨î/ýòÜçð÷¾/òçð¨üîÇÜð×ððÇ ̈ îó ¡³ÚðêðÃðð Ùð÷ü Üð¸ðØððæðð ̈ îðÚððáÐãðÚðÐð çðòÙðòÃð ̈ îó 130ãðóü ×ðø¿¨î ¡ðÚðð÷ò¸ðÃð ̈ îó ±ðýá. ÑßòäðêðÂð çðüçÆððÐðð÷ü ̈ ÷î òâð¦ Ü÷âðãð÷ ×ðð÷Àá çð÷ ̧ ððÜó ̈ îó ±ðýá Üð¸ðØððæðð ̈ îó ÙððÐð¨î ¨îðÚðáçðõµðó ̈ îó ÙðÇð÷ü ÑðÜ ýçð ×ðø¿¨î Ùð÷ü µðµððá ̈ îó ±ðýá.×ðø¿¨î ̈ ÷î ¡ÏÚðêð ¦ãðü òÐðÇ÷äð¨î Ùðèð÷ÇÚð Ðð÷ Üð¸ðØððæðð ¡òÏð¨îðÜó ¡ðøÜ £Ðð¨îó ¾óÙð ̈ îó Ñßäðüçðð ̈ îÜÃð÷ èô¦ ̈ îèð ò¨î £Ðð¨÷î ÃðÆðð ¡ÐÚð ¨îòÃðÑðÚð ¡òÏð¨îðòÜÚðð÷ü ¨÷î ¨îò¿Ðð ÑðòÜåÙð ¡ðøÜ Üð¸ðØððæðð ¨îðÚðð÷áïü Ùð÷ü âð±ðÐð ¨÷î ¨îðÜÂð ýçð çðüçÆððÐð ¨îð÷ Üð¸ðØððæðð çðüçÆððÐð, Ððýá òÇââðó ¨îó äðóâÀ ¡ðøÜ Ðð±ðÜ Üð¸ðØððæðð ¨îðÚððáÐãðÚðÐð çðòÙðòÃð ¨îó äðóâÀ òÙðâðó. £Ðèð÷üÐð÷ ̈ îèð ò¨î èÙð÷ü ýÐð £Ñðâðò×ÏðÚðð÷ü ̈ îó ̈ î´ó ̈ îð÷ ×ðÐðð¦ Ü®ðÐð÷ ̈ ÷î òâð¦, ¡×ð çð÷ ×ðÁ¨ÿîÜ âðêÚð òÐðÏððáòÜÃð ¨îÜÐðð èð÷±ðð ÃðÆðð ¡ðøÜ ¡òÏð¨î Ùð÷èÐðÃð ̈ îÜÐðó èð÷±ðó.

ìððÐðÇóÑð

Gyandeep

IRISET22

IRISET Family Extends a Warm Welcome

Senior Professor Telecom

Smt. S.Manga.V, IRSSE 1985, assumed charge as Senior Professor-

Telecom/IRISET on 21.03.2014. She did her graduation in Electronics

and Communication Engineering from Andhra University, College of

Engineering, Waltair (1981-1985) followed by ME from Delhi College

of Engineering (1985-1987). She started her career from IRISET / SC

(first batch of Centralised Training) on 09.03.1987. She worked over

SCR, NR, CR and WR. While working as CSTE/C on Central Railway, was

involved in commissioning of Kula-Thane 5th and 6th line,

commissioning of Train Management System, gauge conversion –

Khurudwadi, Osmanabad, RRIs Amla, Badnera, Miraj etc., commissioning

of UTS over western Railway, Quad cable work at Gir forest etc.

Shri. M.Raj Kumar, joined IRISET in April 2014 Earlier he worked as

ASTE/Projects, South Central Railway & has experience in Signal

maintenance & Contruction like planning & execution of additional loop

line with panel interlocking, route setting type interlocking, BPAC works

etc.

Lecturer Signalling

Instructor Signalling

Shri. V.Madhusudhan, joined IRISET on 27.01.14 and posted as

Instructor Signal in Train Detection Lab. He has worked as

SSE/Signal/Dornakal, South Central Railway prior to joining IRISET. He

has put upa a total service of 29 years in the Secunderabad divison. He

has experience in various fields of signalling in his entire service viz.

Electro-mechanical signalling, D.C.Track Circuits (RE & Non-RE), UAC,

Panel Interlocking, IPS & SSDAC.

Shri. P.Visweswar Rao, joined IRISET on 25.02.14 and posted as

Instructor Signal in Electrical Signalling Lab. Prior to his joining IRISET,

he worked as SSE/Signal/Sanathnagar. He has put in 33 years of Service.

He has worked with SSDAC, Universal Axle Counter and all types of

Signalling Interlocking.

Shri. Ch. Janaki Ram, joined IRISET on 11.04.2014 and posted as

Instructor Outdoor Signalling. Prior to his joining IRISET he has put in

31 years of service in Secunderabad Division of SCR. He has experience in

the field of RRI, Panel Interlocking and SSI AZD Praha.

ìððÐðÇóÑð

Gyandeep

IRISET23

Pictorial Glimpse

Inauguration of New S&T Laboratory Building by Shri Kul Bhushan, Member Electrical

Shri Satyender Kumar, Director

administering Pledge during the

Vigilance Week Celebrations

Cultural Programmes during Annul Day Celebrations

Parade by Trainees on Republic Day Sports events Winner

Cultural Program as a part of

the Vigilance Awareness Week

S. No A)

A1)

6)

Course NameGAZETTED COURSES

INITIAL COURSES

A2) INTEGRATION COURSES

A3) EQUIPMENT COURSES(SIGNAL)

A4) EQUIPMENT COURSES(TELECOM)

A5) GENERAL COURSES

A6) SPECIAL COURSE FOR SAG OFFICERS

B) NON GAZETTEDBSIG)BSIG1)

BSIG2)

BSIG3)

NON GAZETTED SIGNAL

INITIAL COURSES

REFESHER COURSES

EQUIPMENT COURSES

Digital Axle Counters (SECOND COURSE)Electronic Interlocking (SECOND COURSE)

SDH Equipment (SECOND COURSE)

Computer Networking & Security Management (SECOND COURSE)

Duties and Responsibilities of JAG Officer (SECOND COURSE)

Construction Practices

53rd Course

54th Course55th Course

7)8)

9)

10)

11)

12)

13)

14)15)

Initial Course for Apprentice JE Phase - I (FIRST COURSE)Initial Course for Apprentice JE Phase - I (SECOND COURSE)Initial Course for Apprentice SSE Phase - I (FIRST COURSE)Initial Course for Apprentice SSE Phase - I (FIRST COURSE)Initial Course for JE/SSE (Design) Phase - I

Refresher Course Refresher Course Refresher Course Refresher Course Refresher Course

Earthing & Surge ProtectionElectronic Interlocking Axle Counters and applicationTPWS

16)

17)

18)

19)

20)

21)22)23)24)25)

26)27)28)29)

TLBI DAIDO30)RRI British31)

TPWS

Initiation Course for IRSSE (P) (2013 batch) (TENTATIVE)Initial Course for IRSSE (P) (2012 batch) Phase - II

8-12-14

21-07-14

12-12-14

17-10-14

Integration Course for Group B Officers (Tele to Sig) Phase - II

4)

5)

1)

2)

Start Date End Date

27-10-14

29-12-14

3) Initial Course for IRSSE (P) (2013 batch) Phase - I

15-12-14 13-03-15

05-12-14

06-02-15

21-07-14

27-10-1403-11-14

03-11-14

13-10-14

27-10-14

08-12-14

04-08-14

22-09-1410-11-14

29-09-14

29-09-14

03-11-14

18-08-14

01-12-14

14-07-1411-08-1408-09-14

06-10-1403-11-14

14-07-1421-07-1421-07-1404-08-1411-08-1411-08-14

25-07-14

31-10-14

21-11-14

07-11-14

17-10-14

31-10-14

12-12-14

12-09-1431-10-1419-12-14

02-01-15

02-01-15

30-01-15

17-10-14

30-01-15

08-08-1405-09-1401-10-14

31-10-1428-11-14

18-07-1408-08-1425-07-1408-08-1414-08-1422-08-14

S. No Course Name

32) TLBI PUSHBUTTON 01-09-14 05-09-14

33)

34)

35)

36)

BSIG3)

BSIG4)

BSIG5)

BTEL)

BTEL1)

BTEL2)

37)

38)

39)

40)

41)

42)

43)

44)

45)

46)

47)

48)

49)

50)

51)

52)

53)

54)

55)

56)

57)

58)

59)

60)61)

62)

63)

64)

65)

66)

67)

68)

AFTC

RRI Siemens

Quality in S&T Works (SECOND COURSE)

Data Loggers (SECOND COURSE)

CRASH COURSE ON SAFETY IN SIGNALLING

SPECIAL COURSES ON LOCKING TABLE, SELECTION TABLE AND CIRCUIT DESIGN FOR PI/RRI

SPECIAL COURSES ON ELECTRONIC INTERLOCKING

NON GAZETTED TELECOM

INITIAL COURSES

REFRESHER COURSES

BTEL3) EQUIPMENT COURSES

BTEL4) GENERAL COURSE FOR SIGNAL & TELECOM SUPERVISORS

32nd Course

33rd Course

34th Course

35th Course

36th Course

Metal to Metal Relays - Siemens Practice

Metal to Carbon Relays - British Practice

Metal to Metal Relays - Siemens Practice

MEDHA

ANSALDO

Initial Course for Apprentice JE Phase - I

Initial Course for Apprentice SSE Phase - I

Initial Course for Apprentice SSE Phase - II

Initial Course for Promoted JE (Intermediate)

Refresher Course

Refresher Course

Refresher Course

Mobile Communication

IP Telephony & NGN (FIRST COURSE)

Control Communication & Transmission Media

SDH Equipment (SECOND COURSE)

Computer Networking & Security Management (SECOND COURSE)

Passenger Information System

SDH Equipment (THIRD COURSE)

Computer Networking & Security Management (THIRD COURSE)

IP Telephony & NGN (SECOND COURSE)

Establishment

Pre-selection course (FIRST COURSE)

Promotional Course for JE to SSE

Hindi Keying Training on Computers (SECOND COURSE)

Pre-selection course (SECOND COURSE)

Works & Tenders (SECOND COURSE)

22-09-14

03-11-14

15-12-14

15-12-14

07-07-14

04-08-14

15-09-14

27-10-14

22-12-14

04-08-14

01-09-14

01-12-14

14-07-14

04-08-14

27-10-14

22-09-14

29-12-14

30-06-14

28-07-14

25-08-14

22-09-14

22-09-14

14-07-14

28-07-14

04-08-14

11-08-14

08-09-14

08-09-14

13-10-14

27-10-14

07-07-14

07-07-14

18-08-14

25-08-14

01-09-14

15-09-14

26-09-14

21-11-14

19-12-14

19-12-14

11-07-14

08-08-14

19-09-14

31-10-14

26-12-14

28-08-14

26-09-14

26-12-14

01-08-14

22-08-14

30-01-15

12-12-14

27-03-15

19-09-14

22-08-14

19-04-14

17-10-14

17-10-14

18-07-14

01-08-14

08-08-14

14-08-14

12-09-14

12-09-14

17-10-14

31-10-14

11-07-14

01-08-14

28-08-14

28-08-14

26-09-14

26-09-14

Start Date End Date

Editorial Team:Shri.Satyender Kumar/Director, Shri.S.P.S.Chauhan,DeanShri.Ram Kripal/SPS,Editor Smt S Manga V/SPT Shri.C.K.Prasad/Professor (Telecom) Shri.T.T.Anand/EA, Design & Compiler

Calender of Courses ( July to December 2014)

Integration Course for Group B Officers (Tele to Sig) Phase - I