รายงานการวิจัยฉบับสมบูรณ์ - doi@nrct

-

Upload

khangminh22 -

Category

Documents

-

view

0 -

download

0

Transcript of รายงานการวิจัยฉบับสมบูรณ์ - doi@nrct

รายงานการวจยฉบบสมบรณ

การออกแบบชดทดลองกระบวนการระดบน าแบบ 4 ถง Design and Development Quadruple-tanks Process Apparatus

รองศาสตราจารยอาจนต นวมสาราญ งานวจยน ไดรบทนสนบสนนงานวจยจากงบประมาณเงนรายได ประจาปงบประมาณ 2555

คณะวศวกรรมศาสตร สถาบนเทคโนโลยพระจอมเกลาเจาคณทหารลาดกระบง

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

รายงานการวจยฉบบสมบรณ

การออกแบบชดทดลองกระบวนการระดบน าแบบ 4 ถง Design and Development Quadruple-tanks Process Apparatus

รองศาสตราจารยอาจนต นวมสาราญ งานวจยน ไดรบทนสนบสนนงานวจยจากงบประมาณเงนรายได ประจาปงบประมาณ 2555

คณะวศวกรรมศาสตร สถาบนเทคโนโลยพระจอมเกลาเจาคณทหารลาดกระบง

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

I

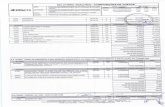

ชอโครงการ (ภาษาไทย) การออกแบบชดทดลองกระบวนการระดบน าแบบ 4 ถง แหลงเงนทน งบประมาณเงนรายได คณะวศวกรรมศาสตร ประจาปงบประมาณ 2555 จานวนเงนทไดรบการสนบสนน 81,000 บาท ระยะเวลาทาการวจย 1 ป ต งแต ตลาคม 2554 ถง กนยายน 2555 ชอ-สกล หวหนาโครงการ และผรวมโครงการวจย พรอมระบ หนวยงานตนสงกด รองศาสตราจารยอาจนต นวมสาราญ สาขาวชาวศวกรรมการวดและควบคม คณะวศวกรรมศาสตร

บทคดยอ ชดทดลองกระบวนการระดบน า 4 ถง เปนอปกรณทมความเหมาะสมสาหรบการประยกตใชเปนกระบวนการตวอยางในการออกแบบระบบควบคม สาหรบกระบวนการแบบสองอนพตสองเอาตพตทสามารถพบเหนไดในหลายๆอตสาหกรรม ซงโดยทวไปแลวกระบวนการแบบสองอนพตสองเอาตพตมกพบปญหาในการควบคมระบบเนองจากมการรบกวนกนระหวางคาตวแปรอนพตและเอาตพตท งสอง การออกแบบระบบควบคมแบบสองอนพตสองเอาตพตทมการรบกวนกนเพอใหไดผลตอบสนองของระบบควบคมตามตองการ จงตองอาศยความรความเขาใจดานคณลกษณะของกระบวนการ ทฤษฎการออกแบบระบบควบคมดวยเทคนคตางๆ รวมถงทกษะความรทางดานการใชงานอปกรณตรวจวด ตวแปลงสญญาณและตวควบคม ดงน นชดทดลองกระบวนการระดบน า 4 ถงจงเปนโจทยปญหามาตรฐานสาหรบการวเคราะหและออกแบบระบบควบคม และสามารถใชสาหรบการเรยนการสอนเพอเสรมสรางทกษะความรความเขาใจถงขดจากดสมรรถนะของระบบควบคมแบบสองอนพตสองเอาตพต อนเนองมาจากการรบกวนกนของตวแปรในกระบวนการ ความไมแนนอนของโมเดลกระบวนการ พฤตกรรมของระบบแบบเฟสไมตาสด การออกแบบตวควบคมแบบกระจายสวน การประยกตใชตวควบคมแบบดคปปล งเพอลดผลกระทบจากการรบกวนกนของตวแปรในกระบวนการ คาสาคญ : กระบวนการระดบน า 4 ถง, สองอนพตสองเอาตพต, การวเคราะหและออกแบบระบบควบคม

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

II

Research Title: Design and Development Quadruple-tank Process Apparatus Researcher Assoc. Prof. Arjin Numsomran Faculty: Engineering Department Instrumentation and Control Engineering

ABSTRACT

A quadruple-tanks process apparatus is an appropriate device for the control system design application of two inputs - two outputs (TITO) process which can be found in several industries. Generally, the TITO control system often has a problem because of the interference between the input and output variables. Therefore achieving the response of control system as desired specifications, it requires a deep understanding of process characteristics, control system theory including knowledge and skills for apparatuses using. Thus, the quadruple-tanks process can be a standard problem for control system analysis and design practices and it can be used to teach students about the skills of instrument devices using, understanding control limitation due to interactions, model uncertainties, non-minimum phase behavior, Design decentralized controllers, implementing decoupling controller to reduce the effect of interactions. Keyword : quadruple-tanks process, TITO, control system analysis and design

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

III

กตตกรรมประกาศ

การวจยคร งน ไดรบทนสนบสนนการวจยจากสถาบนเทคโนโลยพระจอมเกลาเจาคณทหารลาดกระบง จากแหลงทนงบประมาณเงนรายได ประจาปงบประมาณ พ.ศ. 2555 ขอกราบขอบพระคณทานอธการบด สถาบนเทคโนโลยพระจอมเกลาเจาคณทหารลาดกระบง ทสนบสนนการดาเนนการวจยและอานวยการ ขอขอบคณ สาขาวชาวศวกรรมการวดและควบคม คณะวศวกรรมศาสตร สถาบนเทคโนโลยพระจอมเกลาเจาคณทหารลาดกระบงทสนบสนนการดาเนนการวจยจนสาเรจลลวง ขอขอบคณนกศกษา STW Lab สาขาวชาวศวกรรมการวดและควบคม คณะวศวกรรมศาสตร สถาบนเทคโนโลยพระจอมเกลาเจาคณทหารลาดกระบง ทใหความรวมมอในการดาเนนการวจย

รองศาสตราจารยอาจนต นวมสาราญ

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

IV

สารบญ

หนา

บทคดยอภาษาไทย I บทคดยอภาษาองกฤษ II กตตกรรมประกาศ III สารบญ IV สารบญตาราง VII สารบญภาพ VIII บทท 1 บทน า 1

1.1 ความเปนมาและความสาคญ 1 1.2 วตถประสงคงานวจย 1 1.3 ขอบเขตของงานวจย 1 1.4 วธดาเนนงานวจย 2 1.5 ประโยชนทคาดวาจะไดรบ 2

บทท 2 แนวคด ทฤษฎและงานวจยทเกยวของ 3 2.1 การทบทวนวรรณกรรม (Literature review) 3 2.2 วรรณกรรมทถกอางอง 3

บทท 3 องคปรกอบของกระบวนการระดบน า 4 ถง 5 3.1 กระบวนการระดบน า 4 ถง 6 3.2 อปกรณวดระดบน า 7 3.3 อปกรณปรบแตงสญญาณ 4-20mA เปน 1-5V 8 3.4 ชดขบปมน า 9 3.5 ปมน า 10 3.6 แหลงจายไฟสาหรบอปกรณ 10 3.7 ชดบอรดควบคมกระบวนการ 12

บทท 4 แบบจ าลองทางคณตศาสตรและการวเคราะหคณลกษณะของกระบวนการน า 4 ถง 19 4.1 แบบจาลองทางคณตศาสตรของกระบวนการน า 4 ถง 19 4.2 การวเคราะหคณลกษณะของกระบวนการระดบน า 4 ถง 21

4.2.1 ซโรของกระบวนการ MIMO 21 4.2.2 การทางานของซโร 22 4.2.3 ผลกระทบจากตาแหนงซโรตอระบบควบคม 23

บทท 5 ความรพ นฐานการประยกตใชงานดานซอฟตแวร 24 5.1 การใชงานโปรแกรม Matlab 24

5.1.1 โปรแกรม Simulink 24 5.1.1.1 การจาลองระบบพลศาสตร (Dynamic System Simulation) 24

ดวย Simulink

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

V

สารบญ (ตอ)

หนา

5.1.1.2 หลกการของสญญาณและการไหลของตรรก 24 (Signal and Logic Flow)

5.1.1.3 การเชอมตอบลอก 25 5.1.1.4 กลมของบลอกทใชงานบอยในปจจบน 26 5.1.1.5 การสรางแบบจาลองระบบควบคม 29

5.1.2 การตดต งโปรแกรมเพอใชงาน Real Time Windows Target 34 5.1.2.1 Simulink external model interface 34 5.1.2.2 การตดต ง Real Time Windows Target Kernal 34 5.1.2.3 การคาพารามเตอรใน Simulink สาหรบ Real Time Workshop 35

5.2 การเขยนโปรแกรมภาษาซสาหรบหนวยประมวลผล ARM7 36 5.2.1 สถาปตยกรรมไมโครคอนโทรลเลอร ARM7 (ADuC7024) 36 5.2.2 โปรแกรม Keil uVision 3.11 36

5.2.2.1 การเรมตนใชงานโปรแกรม Keil uVision3 41 5.2.2.2 การ debug โปรแกรมภาษา C สาหรบ ARM7 45 5.2.2.3 การตดต งซอฟตแวร ARMWSD 47

5.3 พ นฐานการเขยนภาษาซ (Basic C For ARM7) 48 5.3.1 ความหมายภาษา C สาหรบ ARM7 48 5.3.2 โครงสรางโปรแกรมภาษา C สาหรบ ARM7 49 5.3.3 ตวแปรชนดตาง ๆ และคาคงท 50 5.3.4 ชนดของตวแปรในภาษาซ 50 5.3.5 การประกาศตวแปร 51 5.3.6 ตวแปรแบบอารเรย 52 5.3.7 เครองหมายตวดาเนนการ 52 5.3.8 รปแบบการเขยนคาสง 54

5.3.8.1 คาสงเงอนไขและการทาซ า 56 5.3.8.2 Standard Function และ User define Function 59

บทท 6 การออกแบบระบบควบคมพไอดส าหรบกระบวนการระดบน า 4 ถง 60 6.1 การควบคมแบบพไอด 60

6.1.1 ผลกระทบการควบคมแบบ I และ D 62 6.2 การออกแบบตวควบคมพไอดดวยเทคนคทางเดนราก 64

6.2.1 สถาปตยกรรมไมโครคอนโทรลเลอร ARM7 (ADuC7024) 64 6.2.2 การสราง ROOT LOCI ทสมบรณ 68

6.3 การออกแบบตวควบคมดคบปล งดวย สาหรบกระบวนการหลาย 74 แบบหลายอนพตหลายเอาตพตพไอดดวยเทคนคทางเดนราก

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

VI

สารบญ (ตอ)

หนา เอกสารอางอง 77 ภาคผนวก (ใบงานการทดลอง) 78 ประวตผวจย 98

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

VII

สารบญตาราง ตารางท หนา 3.1 รายละเอยดทางเทคนคของอปกรณวดระดบน า (Differential Pressure Transmitter) 7 3.2 รายละเอยดทางเทคนคของอปกรณปรบแตงสญญาณ SC-95 9 3.3 รายละเอยดทางเทคนคของชดขบปมน า 9 3.4 รายละเอยดทางเทคนคของปมน า 10 3.5 ตารางแสดงคณสมบตของ Switching Power Supply 11 5.1 ชนดของตวแปรในภาษาซ 50 5.2 เครองหมายตวดาเนนการทางคณตศาสตร 53 5.3 เครองหมายตวดาเนนการทางดานการเปรยบเทยบ 53 5.4 เครองหมายตวดาเนนการระดบบต 53 5.5 เครองหมายตวดาเนนการเพมคาและลดคา 53 5.6 เครองหมายตวดาเนนการเลอนบต (ซาย, ขวา) 54 5.7 ตวกาหนดชนดขอมลของภาษาซ 54

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

VIII

สารบญภาพ ภาพท หนา 3.1 ชดทดลองกระบวนการระดบน า 4 ถง 5 3.2 โครงสรางกระบวนการระดบน า 4 ถง 6 3.3 วาลวทใชในการปรบพ นทหนาตดรน าดานออก 6 3.4 อปกรณวดระดบน า (Pressure Sensor 3.92kPa Gauge 1-Port) 7 3.5 อปกรณปรบแตงสญญาณ 4-20mA เปน 1-5V 8 3.6 ชดขบปมน า SE-HB40-1 9 3.7 ปมน า API Instrument 10 3.8 บลอกไดอะแกรมของแหลงจายไฟขนาด 24 V, 6.5 A 11 3.9 อปกรณแหลงไฟขนาด 24 V, 6.5 A 11 3.10 ไมโครคอนโทรลเลอร ARM7 12 3.11 สถาปตยกรรมภายในของไมโครคอนโทรลเลอร ARM7 เบอร ADuC7024 13 3.12 บอรด ET-BASE ARM7024 (ADUc7024) 14 3.13 พอรต P1 มขนาด 6 บต 16 3.14 พอรต P3 มขนาด 8 บต 16 3.15 พอรต P4 มขนาด 8 บต 16 3.16 พอรต ARM-JTAG และวงจรสวนทใชในการเชอมตอกบ ARM-JTAG 17 3.17 การจดเรยงขาสญญาณของ Character LCD มาตรฐาน 17 3.18 วงจรสวนทเชอมตอกบ RS232 18 3.19 ข วตอ ADC0 – ADC9 18 3.20 ข วตอ DAC0 และ DAC1 18 4.1 ชดทดลองกระบวนการระดบน า 4 ถง 19 5.1 ลกษณะของโปรแกรม Simulink 25 5.2 แสดงบลอกตางๆ ของแหลงกาเนดสญญาณ (Sources) และแหลงสญญาณ (Sinks) 26 5.3 แสดงบลอกตางๆ ภายในกลมบลอกของระบบตอเนอง (Continuous System) 27 และระบบไมตอเนอง (Discrete System) 5.4 แสดงบลอกตางๆ ภายในกลมบลอกการดาเนนการทางคณตศาสตร (Math Operations) 27 5.5 แสดงกลมบลอก Discontinuities และกลม Signal Routing 29 5.6 แสดงหนาตางทใชในการกาหนดคาคงทในการจาลองปญหา (Configuration Parameters) 29 5.7 หนาตางสาหรบสรางแบบจาลอง 30 5.8 การเลอกบลอกทตองการจาก Simulink Library Browser 31 5.9 บลอกของระบบตวอยาง 31 5.10 การเชอมตอสญญาณระหวางบลอก 32 5.11 การเปลยนแปลงคาพารามเตอรของบลอก 32 5.12 ไดอะลอกใสคาพารามเตอรของบลอก Transfer Function 33 5.13 แบบจาลองระบบทางกลในรปแบบของ Transfer Function 33

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

IX

สารบญภาพ (ตอ)

ภาพท หนา 5.14 Hardware Implementation 35 5.15 RTW System Target File 36 5.16 แสดงกระบวนการทางานของไปปไลนใน ARM7โปรเซสเซอร 37 5.17 ลกษณะการใชงาน ARM ท ง 7 โหมด 38 5.18 หนาตาง Setup Real View Microcontroller Development Kit Version 3.11 40 5.19 หนาตาง customer Information 40 5.20 หนาตางแสดงการส นสดการตดต งโปรแกรม 41 5.21 หนาตางหลกของโปรแกรม Keil uVision 41 5.22 หนาตาง Components, Environment and Books 42 5.23 หนาตาง Create New Project 42 5.24 หนาตาง Select Device for Target 43 5.25 หนาตาง Add File to Group 43 5.26 หนาตางกาหนด Options for Target 44 5.27 หนาตางกาหนด Output Information 44 5.28 การ compile และการ Build โพรเจกต 45 5.29 ปม Build Target 46 5.30 การเขาสโหมด Simulation หรอ Debug 46 5.31 แสดงสถานะเตรยมพรอม Simulator 46 5.32 ปมการ Debug แบบตางๆ 47 5.33 หนาตางการใชงานของโปรแกรม ARMWSD 47 5.34 การ Configuration โปรแกรม ARMWSD กอนใชงาน 48 5.35 Flow Chart การประมวลผลภาษาซสาหรบ ARM7 49 5.36 โครงสรางโปรแกรมภาษาซ 50 5.37 ตวอยางการประกาศตวแบบ char และ int 51 5.38 อารเรย 1 มต 52 5.39 อารเรย 2 มต 52 6.1 (a) แสดง block diagram ของการควบคมแบบ P, I, D 61 (b) แสดงวา เปนฟงกชน unit ramp (c) แสดงการควบคมเอาตพต 6.2 (a) block diagram ของระบบควบคมแบบอตโนมตแบบ first order sensor 61 (b) block diagram ของระบบควบคมแบบอตโนมตแบบ over damped second order sensor (c) block diagram ของระบบควบคมแบบอตโนมตแบบ underdamped second order sensor 6.3 การควบคมแบบ integral 62

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

X

สารบญภาพ (ตอ)

ภาพท หนา 6.4 (a) แสดงระบบการควบคมระดบของเหลว 63 (b) แสดง block diagram ของระบบ

6.5 pole, zero ของ

1

2 3

( )( )

( )( )

K s zG s

s s p s p

67

6.6 ตวอยางจด breakaway บนแกน real ในระนาบ s 74 6.7 โครงสรางของกระบวนการแบบ TITO 74 6.8 โครงสรางระบบควบคมสาหรบกระบวนการระดบน าแบบ 4 ถงทประกอบดวยชดดคบปล ง 75

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

บทท 1 บทน ำ

1.1 หลกกำรและเหตผลของโครงกำรวจย

การศกษาดานวศวกรรมศาสตรนน การปฏบตการทดลองถอเปนองคประกอบหนงของกระบวนการศกษาทมความส าคญและมความจ าเปนอยางมากเพราะการปฏบตการทดลองชวยใหนกศกษาสามารถเขาใจหลกการทางทฤษฎไดมากขน อกทงยงเปนอกชองทางหนงในการเพมทกษะในการปฏบตงาน การใชอปกรณและเครองมอตางๆใหกบนกศกษา ส าหรบหลกสตรวศวกรรมการวดคมไดมงเนนใหนกศกษาเขาใจหลกการวดและการออกแบบระบบควบคมซงชดทดลองทจ าหนายโดยทวไปมกมราคาสงและยงขาดความยดหยนในการประยกตใชตามวตถประสงคทตองการ ดงนนคณะผวจยจงมแนวคดในการออกแบบชดทดลองกระบวนการระดบน า 4 ถงทมราคาต าแตมความยดหยนส าหรบการประยกตใชสง สามารถสรางความรความเขาใจพฤตกรรมของกระบวนการและฝกฝนทกษะในการออกแบบระบบควบคมใหแกนกศกษาวศวกรรมการวดคมไดเปนอยางด ชดทดลองกระบวนการระดบน า 4 ถง เปนอปกรณทมความเหมาะสมส าหรบการประยกตใชเปนกระบวนการตวอยางในการออกแบบระบบควบคมส าหรบกระบวนการแบบสองอนพตสองเอาตพตทสามารถพบเหนไดในหลายๆอตสาหกรรม ซงโดยทวไปแลวกระบวนการแบบสองอนพตสองเอาตพตมกมปญหาในการควบคมระบบเพราะมการรบกวนกนระหวางคาตวแปรอนพตและอาทพตทงสอง การออกแบบระบบควบคมแบบสองอนพตสองเอาตพตทมการรบกวนกนเพอใหไดผลตอบสนองของระบบควบคมตามตองการ จงตองอาศยความรความเขาใจดานคณลกษณะของกระบวนการ ทฤษฎการออกแบบระบบควบคมดวยเทคนคตางๆ รวมถงทกษะความรทางดานการใชงานอปกรณตรวจวด ตวแปลงสญญาณและตวควบคม ดงนนชดทดลองกระบวนการระดบน า 4 ถงจงเปนโจทยปญหามาตรฐานส าหรบการออกแบบระบบควบคม ซงถกออกแบบมาเพออธบายถงขดจ ากดสมรรถนะของระบบควบคมแบบสองอน พตสองเอาตพต อนเนองมาจากต าแหนงซโรของกระบวนการ สามารถใชส าหรบการปฏบตการทดลองเพอฝกฝนทกษะทางดานการวดและออกแบบระบบควบคม เปนชดทดลองทสามารถสรางองคความรพนฐานใหแกนกศกษาในหลกสตรวศวกรรมการวดคมไดอยางมประสทธภาพ

1.2 วตถประสงคของกำรวจย 1) เพอออกแบบและพฒนาตนแบบชดทดลองกระบวนการระดบน าแบบ 4 ถง ส าหรบการ

ปฏบต การทดลองดานการวดและการออกแบบระบบควบคมส าหรบกระบวนการแบบสองอนพตสองเอาตพต

2) เพอจดท าใบงานประกอบการทดลองเพอสรางความรพนฐานทางดานการวดและการออกแบบระบบควบคม

1.3 ขอบเขตของกำรวจย

ออกแบบและพฒนาตนแบบชดทดลองกระบวนการระดบน าแบบ 4 ถง พรอมจดท าใบงานการทดลอง

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

2

1.4 วธด ำเนนกำรวจย

1) ศกษาคนควาหาขอมลชดทดลองกระบวนการระดบน า 4 ถง 2) ออกแบบชดทดลองกระบวนการระดบน า 4 ถง 3) จดหาอปกรณส าหรบประกอบชดทดลองกระบวนการระดบน า 4 ถง 4) ประกอบและทดสอบการใชงานกระบวนการระดบน า 4 ถง 5) จดท าใบงานการทดลองและคมอใชงาน 6) เขยนรายงานสรปการด าเนนโครงการ

1.5 ประโยชนทคำดวำจะไดรบ

1) ตนแบบชดทดลองกระบวนการระดบน า 4 ถง ส าหรบอธบายผลของพฤตกรรมของระบบแบบสองอนพตสองเอาตพตทมตอประสทธภาพของระบบควบคม

2) ใบงานการทดลองการออกแบบระบบควบคมส าหรบกระบวนการระดบน า 4 ถง

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

บทท 2 แนวคด ทฤษฏและงานวจยทเกยวของ

2.1 การทบทวนวรรณกรรม (Literature review)

กระบวนการระดบน าแบบ 4 ถง ถกออกแบบและพฒนาข นในป ค.ศ. 1996 [1] ทสถาบน Lund Institute of Technology ประเทศสวเดน เพอใชเปนกระบวนการทดลองสาหรบอธบายเทคนคการควบคมระบบแบบหลายตวแปร ถกใชเพออธบายใหนกศกษาเขาใจถงผลของตาแหนงซโรของระบบแบบหลายตวแปรทมตอประสทธภาพของระบบควบคม โดยเปนชดทดลองในหลกสตรวศวกรรมควบคมสาหรบอธบายตวอยางการหาโมเดลของระบบจากผลทดลอง การควบคมแบบเวลาจรง การออกแบบระบบควบคมดวยเทคนคตางๆ เชน PID, Decentralized PID [3], Auto-Tuning PID [4], H Control [5], Adaptive Control เปนตน ดวยคณสมบตของกระบวนการระดบน าแบบ 4 ถง ทสามารถสรางความรความเขาใจพฤตกรรมของกระบวนการและฝกฝนทกษะในการออกแบบระบบควบคมใหแกนกศกษาวศวกรรมการวดคมไดเปนอยางด คณะผวจยจงไดมแนวคดออกแบบและพฒนากระบวนการระดบน าแบบ 4 ถง เพอใชสาหรบการวจยในหวขอตางๆ เชน “I-P Controller Design for Quadruple-Tank System” [6], ,”T-DOF PID Controller Design using Characteristic Ratio Assignment Method for Quadruple Tank Process” [7], ,”Design of Decoupled Controller for TITO System using Characteristic Ratio Assignment” [8], “Modeling of the Modified Quadruple-Tank Process” [9], “Design PID Controller for the Modified Quadruple-Tank Process using Root Locus” [10], “Design of PI Controller Using Decoupling and CRA Techniques for Quadruple-Tanks Process”, [11], “Design of PID Controller for the Modified Quadruple-Tank Process using Inverted Decoupling Technique” [12]

2.2 วรรณกรรมทถกอางอง [1] K. H. Johansson, “The Quadruple-Tank Process: A Multivariable Laboratory

Process with an Adjustable zero”, IEEE Trans. on Control Systems Technology, 8, 456-465, 2000.

[2] Johansson, K.H; Horch,A; Wijk,O; Hansson,A. “Teaching multivariable control using the quadruple-tank process.” Conference on Proceeding of th 38th IEEE, 1999.

[3] J. L. R. Nunes. “Modeling and control of the Quadruple-Tank Process. Master thesis, Department of Automatic Control”, Lund Institute of Technology, Sweden, 1997.

[4] V. Recica. “Automatic tuning of multivariable controllers”. Master thesis, Department of Automatic Control, Lund Institute of Technology, Sweden, 1998.

[5] M. Grebeck. “A comparison of controllers for the quadruple tank system. Technical report, Department of Automatic Control”, Lund Institute of Technology, Sweden, 1998.

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

4

[6] Arjin Numsomran,Tianchai Suksri, Viriya Kongratana, Thanit Trisuwannawat

and Kitti Tirasesth, “I-P Controller Design for Quadruple-Tank System”, TENCON 2004. [7] Tianchai Suksri, U-thai Sritheeravirojana, Arjin Numsomran, Viriya

Kongrattana, and Thongchai Werataweemart,”T-DOF PID Controller Design using Characteristic Ratio Assignment Method for Quadruple Tank Process”,Transactions on Engineering, Computing and Technology, 2006.

[8] Arjin Numsomran, Tianchai Suksri, Maitree Thumma ,”Design of Decoupled Controller for TITO System using Characteristic Ratio Assignment”, ICCAS 2007

[9] Arjin Numsomran, Vittaya Tipsuwanporn, Kitti Tirasesth, “Modeling of the Modified Quadruple-Tank Process”, SICE2008

[10] Arjin Numsomran, Vittaya Tipsuwanporn,Thanit Trisuwannawat and Kitti Tirasesth, “Design PID Controller for the Modified Quadruple-Tank Process using Root Locus”, ICCAS2008

[11] Tianchai.Suksri, Arjin Numsomran, Vittaya Tipsuwanporn, Thanit Trisuwannawat and Kitti Tirasesth, “Design of PI Controller Using Decoupling and CRA Techniques for Quadruple-Tanks Process”, ICCAS2011

[12] Arjin Numsomran, Vittaya Tipsuwanporn, Thanit Trisuwannawat and Kitti Tirasesth, “Design of PID Controller for the Modified Quadruple-Tank Process using Inverted Decoupling Technique”, ICCAS2011

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

บทท 3 องคประกอบของกระบวนการระดบน า 4 ถง

ชดทดลองกระบวนการระดบน า 4 ถง ประกอบดวยอปกรณตางๆทสาคญ 7 สวนดวยกน คอกระบวนการระดบน า 4 ถง อปกรณตรวจวดความดน วงจรปรบแตงสญญาณแรงดนทไดรบจากเซนเซอรวงจรขบกระแส ปมน า แหลงจายไฟ และ ชดบอรดควบคม สวนเอาตพตของระบบคอ ระดบน าของถงดานลางท ง 2 ใบ อนพตของระบบคอสญญาณควบคมทปอนใหแก ชดขบปมน า ทศทางการไหลของน าและคณลกษณะของกระบวนการสามารถปรบเปลยนตามตาแหนงการเปด -ปดของวาลวทางเขาของน า ซงตาแหนงซโรของกระบวนการสามารถปรบตาแหนงใหอยไดท งดานซายและดานขวาของระนาบ s โดยการปรบเปลยนตาแหนงวาลวทางเขาของน า รายละเอยดของอปกรณตางๆทใชในการทดลองน นสามารถอธบายไดดงตอไปน

ภาพท 3.1 ชดทดลองกระบวนการระดบน า 4 ถง

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

6

3.1 กระบวนการระดบน า 4 ถง กระบวนการระดบน า 4 ถง ประกอบดวยถงน าอะครลคมขนาดเพ นทหนาตด 169.56 cm2 และสง 20.0 เซนตเมตร 4 ใบ โดยถงน าแตละใบจะมวาลว ทใชในการปรบพ นทหนาตดรน าดานออกจากถง แสดงไดดงภาพท 3.2 น าทไหลเขาสถงน าแตละใบน นจะถกปมข นมาจากบอเกบน าดานลาง โดยปมน ากระแสตรง 24 โวลต ถกใชเพอจายน าใหถงแตละใบผานสายยางออนขนาดเสนผานศนยกลางภายใน 8 มลลเมตรและผานวาลว ทใชในการปรบความตานทานการไหลสาหรบปรบเปลยนโหมดการควบคมของกระบวนการ

ภาพท 3.2 โครงสรางกระบวนการระดบน า 4 ถง

วาลวทใชในการปรบพ นทหนาตดรน าทางดานออกของถงน าแตละใบ แสดงไดดงภาพท 3.3

ภาพท 3.3 วาลวทใชในการปรบพ นทหนาตดรน าดานออก

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

7

3.2 อปกรณวดระดบน า ( Gauge Pressure Sensor ) อปกรณทใชวดระดบน าทเลอกใชสาหรบกระบวนการน จะเลอกใช อปกรณวดแรงดนแบบความดนเกจ (Pressure Sensor 3.92kPa Gauge 1-Port) ของ Freescale Semiconductor รน MPXV5004GC7U Range 0-3.92 kPa คาความแมนยาคอ %5.1 of Span ใชพาวเวอรซพพลาย 5.25 VDC และ ใหเอาตพต 1-5 Volts รปของอปกรณวดระดบน าแสดงไดดงภาพท 3.4

ตารางท 3.1 รายละเอยดทางเทคนคของอปกรณวดระดบน า (Differential Pressure Transmitter)

Reference Accuracy +1.5% of Span

Analogue Output 1-5 Volts

Maximum Operating Temperature +85 C

Maximum Pressure Reading 3.92 kPa

Minimum Pressure Reading 0 kPa

Media Measured Air, Fluid

Pressure Reading Type Gauge

Supply Voltage 4.75 → 5.25 V dc

ภาพท 3.4 อปกรณวดระดบน า (Pressure Sensor 3.92kPa Gauge 1-Port)

การวดระดบน าน นจะใชสายยางขนาด 8 มลลเมตรทตอมาจากดานกนถงของถงน าใบท 1 และ 2 ตอเขาทางดานอนพตของตวตรวจวดแรงดน คาความดนเกจทวดโดยอปกรณตรวจวดความดนจงสมพนธกบระดบน าในถงดงตอไปน

ghP (3.1)

โดย คอ ความหนาแนนของน า 3kg/cm1000 g คอ แรงโนมถวงของโลก 2m/s81.9

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

8

h คอ ระดบน าทวด m P คอ ความดนแตกตาง KPa ในการทดลองกาหนด ชวงการวดอยทระยะ 0 เซนตเมตรถง 20.0 เซนตเมตร

(1000 9.81 0.20) /1000P (3.2)

1.962 KPa ดงน นจะไดชวงความดนเกจทสมพนธกบชวงการวดระดบน า เทากบ

0 1.962 KPaP

เมอกาหนดชวงความดนแตกตางขางตนใหเปนชวงการวดระดบ 0% ถง 100% ของระดบน าในถงท 1 และ 2 อปกรณวดแรงดนแบบความดนเกจ จะใหเอาตพตเปนคาแรงดนไฟฟาไฟฟา 1-5 Volts ทสมพนธกบระดบน าในถงท 1 และ 2 ทความสง 0 ถง 20.0 เซนตเมตร

3.3 อปกรณปรบแตงสญญาณ 4-20mA เปน 1-5V

ภาพท 3.5 อปกรณปรบแตงสญญาณ 4-20mA เปน 1-5V SC-95 เปนอปกรณททาหนาทแปลงสญญาณจาก 4 ถง 20 มลลแอมป เปน 1 ถง 5 โวลท เพอ

สงตอไปยงการดแปลงสญญาณ A/D และ D/A ขอมลคณสมบตและรายละเอยดของอปกรณปรบแตงสญญาณ แสดงไดดงตารางท 3.3

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

9

ตารางท 3.2 รายละเอยดทางเทคนคของอปกรณปรบแตงสญญาณ SC-95 Input voltage Rangeable from 10 mVDC to 100VDC Input current Rangeable from 100uA DC to 100mA DC Output 4-20 mA,0-20 mA/ 0-1 V,0-5 V,1-5 V,0-10 V Linearity < + 0.2% of span Power Supply 100 VAC.,110 VAC.,220 VAC.,24 VDC

3.4 ชดขบปมน า

ใชในการควบคมการทางานของมอเตอรปมน า โดยรบสญญาณ PWM (Pulse Width Modulation) จากไมโครคอนโทรลเลอรเพอนาไปควบคมมอเตอรดซ โดยบอรดขบมอเตอรดซน เปนบอรดสาเรจรป ทางานโดยใชมอสเฟต แบบ H-Bridge รน SE-HB40-1

ภาพท 3.6 ชดขบปมน า SE-HB40-1 SC-95 เปนอปกรณททาหนาทแปลงสญญาณจาก 4 ถง 20 มลลแอมป เปน 1 ถง 5 โวลท เพอ

สงตอไปยงการดแปลงสญญาณ A/D และ D/A ขอมลคณสมบตและรายละเอยดของอปกรณปรบแตงสญญาณ แสดงไดดงตารางท 3.3

ตารางท 3.3 รายละเอยดทางเทคนคของชดขบปมน า Output - Motor DC Supply 12-24 V 40A (Max.)

- Full-Complementary Power MOSFET Driver With ultrafast reverse recovery protection diodes

Input - Full Opto-isolated input interface signals - 5V 8 mA TTL – Level

Drive Mode - ON – OFF Control - Direction Control - Speed Control (PWM Drives)

PWM Frequency - 400 Hz - 1000 Hz (800 Hz Recommend )

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

10

3.5 ปมน า ปมน าทใชในการทดลองน นจะใชของบรษท API Instruments รน P6 10.0006 ซงจะเปนปม

น าแบบเกยรปม โดยรปของปมน าทใชในการทดลองแสดงไดดงภาพท 3.7 สวนขอมลคณสมบตและรายละเอยดของปมน าแสดงไดดงตารางท 3.4

ภาพท 3.7 ปมน า API Instrument

ตารางท 3.4 รายละเอยดทางเทคนคของปมน า Max Flow rate 2200 ml/min (Vdc) Max. Suction 10 ft. H2O wet, 4” dry Max. Pressure 20 psig (46 ft. H2O) Port Size (OD) 4.8 mm (0.18”) hose barb Power Require (Vdc) 24 Vdc (up to 28W) Max Operating Temp 930C (2000F) Ambient Fluid Temp 0 to 930C (32 to 2000F) Particulates No Run dry No Max. Viscosity 200 cps Dimensions 888192 mm (41.752.63) Weight 1.4 kg (3 lb.)

3.6 แหลงจายไฟสาหรบอปกรณ

แหลงจายไฟสาหรบอปกรณขบกระแสของปมน าน นจะใชแหลงจายไฟแบบสวตชง ขนาด 24 V, 6.5 A โดยรปบลอกไดอะแกรมของแหลงจายไฟแสดงดงภาพท 3.8 และรปอปกรณแหลงจายไฟแสดงดง

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

11

ภาพท 3.9 ขอดของสวตชงเพาเวอรซพพลายเมอเปรยบเทยบกบแหลงจายไฟแบบเชงเสน คอมประสทธภาพทสง ขนาดเลก และน าหนกเบากวาแหลงจายไฟแบบเชงเสน เนองจากแหลงจายไฟแบบเชงเสนใชหมอแปลงความถตาจงมขนาดใหญ และน าหนกมาก ขณะใชงานจะมแรงดนและกระแสผานตวหมอแปลงตลอดเวลา กาลงงานสญเสยทเกดจากหมอแปลงจงมคาสง

ภาพท 3.8 บลอกไดอะแกรมของแหลงจายไฟขนาด 24 V, 6.5 A

ภาพท 3.9 อปกรณแหลงจายไฟขนาด 24 V, 6.5 A

ตารางท 3.5 ตารางแสดงคณสมบตของ Switching Power Supply Output DC Voltage 24 V Output Rated Current 6.5 A Output Current Range 0–6.5 A Output Rated Power 156 W Output Voltage Adjust Range 21–28 V Input Voltage Range 85-132 VAC/170-264 VAC Input Frequency Range 50-60 Hz Input AC Current 2.0 Amax Input Leakage Current 3.5 mA/240V Overload 105-150% Rate Output Power Overvoltage 30-34.8V Working Temp. -10 - +60

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

12

3.7 ชดบอรดควบคมกระบวนการ

ภาพท 3.10 ไมโครคอนโทรลเลอร ARM7 บอรด ARM7 ทใชในงานวจยน เปนบอรดทมไมโครคอนโทรลเลอร ARM7 เบอร ADuC7024

ของบรษท Analog Device ตอใชงาน ซงบอรดน มหนาทเพอรบและสงสญญาณระหวางคอนโทรลเลอรกบกระบวนการ โดยสถาปตยกรรมของ ARM7 เปนซพยแบบ RISC ขนาด 32 บต ภายในมบสขนาด 32 บต ตวเดยวทใชสาหรบรบขอมลและคาสง ชดคาสงจะมขนาด 32 บต คงท ในขณะทขอมลสามารถเลอกไดวาจะมขนาด 8, 16 หรอ 32 บต

โครงสรางของ ARM7 จะเปนแบบทเรยบงาย มชดคาสงไมมากนก ประหยดพ นท สารกงตวนาทใชสรางประหยดพลงงาน ในการประมวลผลขอมลใดๆ ตองกระทาผานทางรจสเตอร เรมตนดวยการโหลดคาจากหนวยความจา เกบคาในรจสเตอร นาคามาประมวลผล เสรจแลวจะเขยนคาเกบในหนวยความจาดงเดม รจสเตอรของ ARM7 ทใชงานไดสาหรบผใชมท งหมด 16 ตวคอ R0-R15 โดยทกตวมขนาด 32 บต โดย R0-R12 เปนรจสเตอรทวไปไมไดกาหนดหนาทการทางานพเศษ สวน R12 ทาหนาทเปน stack pointer (SP) R14 ทาหนาทเปน link register (LR) และ R15 ทาหนาทเปน Program Counter (PC)

คณสมบตของบอรด เลอกใช MCU ตระกล ARM7 TDMI Core เบอร ADUc7024 ของ Analog Device

เปน MCU ประจาบอรด โดยเลอกใชแหลงกาเนดสญญาณนาฬกาแบบ XTAL คา 32.768 KHz ซงสามารถกาหนดการทางานรวมกบ Phase Lock Loop ให MCU สามารถประมวลผลดวยความเรวสงสดท 41.78 MHz ไดดวย โดยคณสมบตเดนๆของ MCU ไดแก

มหนวยความจา Flash สาหรบเขยนโปรแกรม 62KByte และ ม RAM ขนาด 8Kbyte

มพอรต I/O จานวน 5 พอรตคอ P0(6Bit),P1(8Bit),P2(1Bit),P3(8Bit) และ P4(8Bit)

มวงจรสอสารอนกรม UART จานวน 1 พอรต และมวงจรสอสาร SPI จานวน 1 พอรต

มวงจร Timer/Counter จานวน 4 ชด มวงจร ADC ขนาด 12บต จานวน 10 ชอง และ DAC ขนาด 12 บต จานวน 2

ชอง มวงจร Watchdog, Power-ON Reset, PWM

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

13

มข วตอสญญาณ I/O แบบ TTL แบบ Header 2x5 จานวน 3 ชด (P1,P3 และ P4) มข วตอ LCD แบบ Header 2x7 รองรบการเชอมตอกบ LCD Character (เชอมตอ

แบบ 4 บต) มข วตอใชงาน RS232 สาหรบใชงาน และ สาหรบ Download ผาน RS232 ใชแหลงจายไฟขนาด +5VDC รวมกบ Regulate 3.3V on Board พรอม LED

สถานะ Power ขนาด PCB Size เลกเพยง 8 x 6 cm.

ภาพท 3.11 สถาปตยกรรมภายในของไมโครคอนโทรลเลอร ARM7 เบอร ADuC7024

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

14

ภาพท 3.12 บอรด ET-BASE ARM7024 (ADUc7024) ในภาพท 3.12 แสดงองคประกอบของบอรดไมโครคอนโทรลเลอร ADuC7024 ซงม

รายละเอยดดงตอไปน - หมายเลข 1 คอ ข วตอแหลงจายไฟเล ยงวงจรของบอรด ใชกบแหลงจายไฟตรง +5VDC - หมายเลข 2 คอ Port-LCD ชนด Character Type ใชการเชอมตอแบบ 4 บต ผาน Port -

P4 [0..6] - หมายเลข 3 คอ ตวตานทานสาหรบปรบคาความสวางให LCD - หมายเลข 4 คอ Port-P4 ม ขนาด 8 Bit คอ P4 [0..7] - หมายเลข 5 คอ ข วตอ ADC จานวน 10 ชอง คอ ADC [0..9] - หมายเลข 6 คอ จดตอแรงดนอางองให ADC จากภายนอก - หมายเลข 7 คอ ข วตอ DAC จานวน 2 ชอง คอ DAC [0..1] - หมายเลข 8 คอ จดตอแรงดนอางองให DAC จากภายนอก - หมายเลข 9 คอ MCU เบอร ADUc7024 ซงเปน MCU ตระกล ARM7TDMI จาก Analog

Device - หมายเลข 10 คอ Crystal คา 32.768 KHz - หมายเลข 11 คอ Port-P0 ม ขนาด 6 Bit คอ P0[0,3,4,5,6,7] และ Port-P2 ม 1 บต คอ

P2 [0] - หมายเลข 12 คอ Port-P1 ม ขนาด 6 Bit คอ P1 [2..7] - หมายเลข 13 คอ Port-P3 ม ขนาด 8 Bit คอ P3 [0..7] - หมายเลข 14 คอ Switch RESET ใชสาหรบ Reset การทางานของ CPU - หมายเลข 15 คอ Switch LOAD ใชรวมกบ RESET สาหรบสง Download HEX ให MCU - หมายเลข 16 คอ ข วตอ ARM-JTAG สาหรบ Debug โปรแกรม - หมายเลข 17 คอ ข วตอ RS232 สาหรบใชงานทวไป และ Download HEX ให MCU - หมายเลข 18 คอ LED Power ใชแสดงสถานะของแหลงจายไฟ +5VDC

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

15

ขวสญญาณตาง ๆ สาหรบข วตอสญญาณของพอรต I/O จาก MCU น น จะถกออกแบบและจดเตรยมไวผานทาง

ข วตอแบบ IDE Header ขนาด 10Pin (2x5) จานวน 3 ชด คอ PORT-P1, PORT-P3 และ PORT-P4 ตามลาดบ สวน PORT-P0 และ PORT-P2 น นจะตอเปน Header ขนาด 1x7 ไว โดยทข วตอสญญาณแตละชด จะ ประกอบไปดวยสญญาณของ I/O ทเชอมตอมาจากขาสญญาณของ MCU โดยตรงท งหมด โดยจดเชอมตอกบสญญาณภายนอกของบอรด มดงน

- ข วตอแหลงจายขนาด +5VDC - ข วตอ PORT-P0 ม 6 บต คอ P0 [0,3,4,5,6,7] - ข วตอ PORT-P1 ม 6 บต คอ P1 [2,3,4,5,6,7] สวน P1.0 และ P1.1 จะจะถกเชอมตอผาน

วงจร - Line Driver (MAX232) สาหรบแปลงระดบสญญาณจากระดบโลจก TTL ของ MCU ให

เปน - สญญาณแรงดนตามมาตรฐานของ RS232 โดยสญญาณทไดรบการแปลงเปนแบบ RS232

จะถก - เชอมตอไปรอไวทข วตอแบบ CPA ขนาด 4 PIN (RS232) - ข วตอ PORT-P2 มขนาด 1 บต คอ P2.0 - ข วตอ PORT-P3 มขนาด 8 บต คอ P2 [0,1,2,3,4,5,6,7] - ข วตอ PORT-P4 มขนาด 8 บต คอ P4 [0,1,2,3,4,5,6,7] โดยมการตอสญญาณไปยงข ว

LCD ดวย - จานวน 7 บต คอ P4 [0,1,2,3,4,5,6] ตามลาดบ - ข วตอ ADC มขนาด 10 ชอง คอ ADC0-ADC9 โดยรบสญญาณ Analog ไดระหวาง 0-2.5V - จดรบแรงดนอางองของ DAC (DAC Reference) จากภายนอกขนาด 0-3V - ข วตอ DAC มขนาด 2 ชอง คอ DAC0, DAC1 โดยสามารถสรางสญญาณ Analog ได

0-2.5V - จดรบแรงดนอางองของ ADC (+Vref ADC) จากภายนอกขนาด 0-2.5V - ข วตอ ARM-JATG - ข วตอสญญาณ RS232

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

16

ภาพท 3.13 พอรต P1 มขนาด 6 บต

ภาพท 3.14 พอรต P3 มขนาด 8 บต

ภาพท 3.15 พอรต P4 มขนาด 8 บต

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

17

ภาพท 3.16 พอรต ARM-JTAG และวงจรสวนทใชในการเชอมตอกบ ARM-JTAG

พอรต CLCD ใชกบ Character LCD โดยเชอมตอแบบ 4 บต โดยสญญาณทใชเชอมตอกบ LCD เปนสญญาณชดเดยวกบทตอไปยงข วตอของ PORT-P4 โดยในการเชอมตอสายสญญาณจากข วตอของพอรต LCD ไปยงจอแสดงผล LCD น นมการจดเรยงขาสญญาณของ Character LCD แสดงดงภาพท3.18

ภาพท 3.17 การจดเรยงขาสญญาณของ Character LCD มาตรฐาน

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

18

พอรต RS232 เปนสญญาณ RS232 ซงผานวงจรแปลงระดบสญญาณ MAX232 สามารถใชเชอมตอกบสญญาณ RS232 เพอรบสงขอมล และสามารถใชงาน รวมกบ Switch PSEN และ Switch RESET เพอทาการ Download แบบ Manual

ภาพท 3.18 วงจรสวนทเชอมตอกบ RS232

ภาพท 3.19 ข วตอ ADC0 – ADC9

ภาพท 3.20 ข วตอ DAC0 และ DAC1

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

บทท 4 แบบจำลองทำงคณตศำสตรและกำรวเครำะหคณลกษณะของกระบวนกำรน ำ 4 ถง

กระบวนการระดบน า 4 ถง เปนกระบวนการในการศกษาและการทดลองแบบใหมซงถกแนะนาโดย K.H.Johansson [1] ซงกระบวนการน ไดถกออกแบบมาเพอทาการอธบายถงขดจากดสมรรถนะของระบบควบคมแบบ MIMO อนเนองมาจากตาแหนงของซโรของกระบวนการ โดยกระบวนการน นจะประกอบดวยถงน า 4 ใบและปมน า 2 ตว ซงอนพตทเขาสกระบวนการคอคาแรงดนทจายใหกบปมท ง 2 ตวและเอาตพตของกระบวนการคอ ระดบน าของถงน าดานลางท ง 2 ใบ เมอทาการวเคราะหแบบจาลองเชงเสนของกระบวนการระดบน า 4 ถง จะพบวาตาแหนงซโรของกระบวนการน นสามารถปรบตาแหนงใหอยไดท งดานซายและดานขวาของระนาบ s โดยการปรบเปลยนคาตาแหนงวาลว ซงกคอกระบวนการน สามารถเลอกโหมดการทางานใหเปนแบบเฟสตาสดหรอเฟสไมตาสดนนเอง

ภำพท 4.1 ชดทดลองกระบวนการระดบน า 4 ถง

4.1 แบบจำลองทำงคณตศำสตรของกระบวนกำรระดบน ำ 4 ถง พจารณากระบวนการระดบน า 4 ถง ในภาพท 4.1 เปาหมายของการควบคมกระบวนการหรอ

เอาตพตของระบบ คอระดบน าในถงท 1 และ 2 โดยอนพตของกระบวนการคอ คาแรงดนไฟฟาทจายใหกบปมน า 1u โดย i คอวาลวทใชในการปรบสดสวนการไหลของน าทเขาสแตละถง ซงในกรณศกษาน จะกาหนดให 3 และ 4 มคาเทากบ 21 และ 11 แบบจาลองทางคณตศาสตรสาหรบแบบจาลองไมเปนเชงเสนของกระบวนการระดบน า 4 ถงน สามารถหาไดจากสมการสมดลมวลและกฎของเบอรนล (Bernoulli’s) ดงรายละเอยด ตอไปน

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

20

1 3 31 1 1 11 3 1

1 1 1

2 2 2 4 4 2 22 4 2

2 2 2

3 2 23 33 2

3 3

4 1 14 44 1

4 4

2 2

2 2

12

12

dh t aa kgh t gh t u t

dt A A A

dh t a a kgh t gh t u t

dt A A A

dh t kagh t u t

dt A A

dh t kagh t u t

dt A A

(4.1)

โดย ih t คอ ระดบน าในถง i i = 1 ~ 4 ; cm

ia คอ พ นทหนาตดของรน าดานออกของถง i i = 1 ~ 4 ; cm2

iA คอ พ นทหนาตดของถง i i = 1 ~ 4 ; cm2

i คอ คาตาแหนงวาลวทตอดานออกจากถง i i = 1 ~ 4

i คอ คาตาแหนงวาลวทตออยกบปม i i = 1, 2

ik คอ คาอตราขยายของปม i i = 1, 2 ; cm3/Vs g คอ แรงโนมถวงของโลก 981 cm/s2

iu คอ แรงดนทจายใหกบปม i i = 1, 2 ; V

อตราการไหลของน าทไหลเขาถงท 1 จะเปนสดสวนกบ 1 1 1k u และอตราการไหลของน าทไหลเขาถงท 4 จะเปนสดสวนกบ 1 1 11 k u และในทานองเดยวกนสาหรบถงท 2 และถงท 3 สญญาณอนพตหรอสญญาณควบคมทปอนเขาสกระบวนการคอ u1 และ u2 (คาสญญาณแรงดนทจายใหกบปมน า) และสญญาณเอาตพตทวดจากกระบวนการคอ y1 และ y2 (คาสญญาณแรงดนจากอปกรณวด) จะถกปรบใหเปนสดสวนเดยวกนกบความสงของระดบน าทวดได คอ 1 1 1my k h และ 2 2 2my k h โดย 1 2 1m mk k

จากสมการ (4.1) สามารถทาใหเปนแบบจาลองเชงเสนในรปแบบของสมการสเตท -สเปซไดโดยกาหนดให 0

i i ix h h และ 0i i iu u u

1 13 31

. 11 3 3

11 2 22 4 4.

22 12 2 42

.2 23 3

2

33.4

24 1 1

4 4

00 0

( )00 0

( )

1( ) 00 0 0

( ) 10 0 0 0

kA

AT A Tx t x t kA

Ax t uT A Tx t

kx tx t

AT x tx t k

T A

2

t

u t

(4.2)

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

21

1

1 2

2 3

4

1 0 0 0

0 1 0 0

x t

y t x t

y t x t

x t

โดยคาคงตวเวลาสาหรบแบบจาลองเชงเสนของกระบวนการน คอ

02 i i

i

i i

A hT

a g (4.3)

และเมททรกฟงกชนถายโอนของแบบจาลองเชงเสนน คอ

2 2 11 1 1

1 1 3

1 1 2 2 2 2

2 4 2

1

1 1 1

1

1 1 1

p

k ck c

T s T s T sG s

k c k c

T s T s T s

(4.4)

โดย 11

1

T

CA

และ 22

2

T

CA

และสมการท (4.4) จะสมมลยกบเมททรกฟงกชนถายโอนดงน

11 12

21 22

p

G s G sG s

G s G s

(4.5)

จากสมการ (4.4) จะสงเกตเหนไดวา ฟงกชนถายโอนแตละคอนพต-เอาตพตน นไมมซโรซงการ

พจารณาแบบน เปนการพจารณาเพยงสวนยอยของระบบเทาน น โดยสาหรบกระบวนการแบบ MIMO น นการพจารณาโพลและซโรของกระบวนการท งหมด จะแตกตางจากระบบ SISO ซงวธในการหาจะอธบายในสวนของคณลกษณะของกระบวนการ

4.2 กำรวเครำะหคณลกษณะของกระบวนกำรระดบน ำ 4 ถง

4.2.1 ซโรของกระบวนการ MIMO การหาตาแหนงและทศทางซโรสาหรบกระบวนการแบบหลายอนพต-เอาตพต MIMO

น น เปนสงสาคญมาก เนองจากซโรของกระบวนการน นสามารถเกดข นไดแมวาฟงกชนถายโอนยอยของกระบวนการแตละอนพต-เอาตพตไมมซโรอยเลยกตาม กระบวนการระดบน า 4 ถงกเปนกระบวนการหนงทฟงกชนถายโอนยอยในแตละคอนพต -เอาตพตไมมซโร แตเมอวเคราะหท งระบบแลวน นจะพบวากระบวนการน มซโรซอนอย ซงซโรของกระบวนการสามารถอยไดท งดานซายหรอดานขวาของระนาบ s กไดโดยการปรบตาแหนงวาลว 1 และ 2 นอกจากน แลวผลจากการปรบคาตาแหนงวาลว 1 และ 2 ยงม

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

22

ผลทาใหทศทางของซโรเปลยนไป ซงทศทางของซโรน จะเปนตวกาหนดถงเอาตพตทจะไดรบผลกระทบจากซโรตวน น

ในสวนน จะอธบายถงวธการหาตาแหนง, ทศทางของซโรของกระบวนการระดบน า 4 ถง ซงสามารถอธบายไดในรปแบบของคาตาแหนงวาลว 1 และ 2 และอธบายถงผลกระทบจากตาแหนงและทศทางของซโรตอกระบวนการ

4.2.2 การหาตาแหนงซโร ซโรของเมททรกฟงกชนถายโอนในสมการ (3.4) น นกคอเทอมเศษ (Numerator) ของ

สมการพหนามซงหาไดจากการทาดเทอรมแนนทเมททรกฟงกชนถายโอน (4.4) นนเอง

1 21 2 1 2 1 2

3 44

1 2

1 1det 1 1

1p

i

i l

k k c cG s T s T s

T s

(4.6)

ดงน นเมททรกฟงกชนถายโอน )(sGp

จะมซโรอย 2 ตว โดยซโรตวหนงจะอยดานซายของระนาบ s เสมอในขณะทซโรอกตวหนงน นสามารถอยไดท งดานซายหรอดานขวาของระนาบ s กาหนดให 0,

1 2

1 2

1 1

(4.7)

ถา มคานอย 0 ซโรท ง 2 ตวจะเขาใกลตาแหนง 31/T และ 41/T

ในขณะท มคามาก ซโรตวหนงจะเขาใกล และซโรอกตวหนงจะเขาใกล ถา 1 จะมซโรตวหนงอยทจดศนยกลางของระนาบ s ซงสอดคลองกบ 1 2 1 จากสมการ (3.6)

เหนไดวาระบบจะเปนแบบเฟสไมตาสด สาหรบในกรณท 1 20 1 และเปนแบบเฟสตาสดสาหรบในกรณท 1 21 2

การทซโรของกระบวนการน ตวหนงอยไดท งดานซายและดานขวาของระนาบ s สามารถอธบายไดโดยคณสมบตทางกายภาพของกระบวนการคอ กาหนดให iq คออตราการไหลจากปม i

และสมมตใหอตราการไหล 1 2q q เมอน นผลรวมของปรมาณน าท งหมดทไหลเขาสถงดานบนคอ 1 2 12 ( ) q และผลรวมของปรมาณน าทไหลเขาสถงดานลางคอ 1 2 1( )q ดงน นปรมาณน าทไหลเขาสถงดานลางจะมากกวาถงดานบนกตอเมอ 1 2( ) 1 ซงสอดคลองกบการทกระบวนการมคณสมบตเปนแบบเฟสตาสด และถาปรมาณน าทไหลเขาสถงดานบนมากกวาถงดานลางกระบวนการกจะมคณลกษณะเปนแบบเฟสไมตาสด จากทไดทาการอธบายมาสามารถสงเกตเหนไดวา ถาปรมาณน าไหลเขาสถงดานลางมากกวาถงดานบน 1y และ 2y ควรทจะถกควบคมดวย 1u และ 2u ในทางกลบกนปรมาณน าทไหลเขาสถงดานบนมากกวาถงดานลาง 1y และ 2y กควรทจะถกควบคมดวย 2u และ 1u

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

23

4.2.3 ผลกระทบจากตาแหนงซโรตอระบบควบคม ดงไดอธบายในสวนทแลววา กระบวนการน สามารถเลอกรปแบบการทางานใหเปน

แบบเฟสตาสดหรอเฟสไมตาสดได โดยผลกระทบจากตาแหนงซโรตอระบบควบคมในกรณเฟสตาสดและเฟสไมตาสดจะแตกตางกน ซงสามารถอธบายไดดงน

กรณเฟสต ำสด ในกรณน ซโรของกระบวนการท ง 2 ตว จะอยดานซายของระนาบ s โดยเปนททราบกน

ดอยแลววา ตาแหนงซโรสาหรบกระบวนการ SISO น นจะมผลกระทบตอผลตอบสนองของระบบควบคมในรปของคาพงเกนและขดจากด ของอนพต อนเนองมาจากคาอตราขยายทสภาวะคงตวนอยซงสอดคลองกบการทซโรอยใกลจดศนยกลางของระนาบ s มาก แตสาหรบกระบวนการ MIMO เชนกระบวนการ 2 อนพต 2 เอาตพต ผลกระทบจากตาแหนงซโรตอระบบควบคมกจะคลายกบกระบวนการ SISO แตกตางกนตรงทตาแหนงของซโรน นสามารถมผลกระทบกบเอาตพตใดเอาตพตหนง หรออาจจะมผลกระทบตอท งสองเอาตพตกไดข นอยกบทศทางของซโร

กรณเฟสไมต ำสด ในกรณน ซโรของกระบวนการตวหนงจะมตาแหนงอยดานซายของระนาบ s และซโร

อกตวหนงจะมตาแหนงอยทางดานขวาของระนาบ s โดยผลกระทบจากการทซโรมตาแหนงอยทางดานซายของระนาบ s กจะเปนเชนเดยวกบทไดอธบายในกรณเฟสตาสด แตสาหรบซโรทมตาแหนงอยดานขวาของระนาบ s จะมผลทแตกตางกนออกไป คอซโรทมตาแหนงอยทางดานขวาของระนาบ s จะเปนตวจากดแบนดวดทของระบบควบคม ซงสอดคลองกบความเรวผลตอบสนองของระบบควบคมนนเอง โดยแบนดวดทของระบบควบคมในกรณทมซโรอยทางดานขวาของทางระนาบ s คอ

2b

z (4.8)

สมการ (4.8) สงเกตไดวา ถาซโรอยใกลจดศนยกลางของระนาบ s แบนดวดทของ

ระบบควบคมจะแคบ ในทางกลบกนถาซโรอยหางจากจดศนยกลางของระนาบ s แบนดวดทของระบบควบคมจะกวาง

จากททาการอธบายมาแสดงให เหนไดวากระบวนการระดบน า 4 ถงน นเปนกระบวนการทเหมาะสมสาหรบการศกษาถงพฤตกรรม และการอธบายถงขดจากดทางดานสมรรถนะในการออกแบบตวควบคมของระบบควบคมแบบหลายอนพต-หลายเอาตพต MIMO อนเนองมาจากตาแหนงซโรทอยทางดานขวาของระนาบ s ซงจากแบบจาลองเชงเสนของกระบวนการระดบน า 4ถง พบวา ตาแหนงซโรของกระบวนการน นจะข นอยกบคาตาแหนงของวาลว 1 2, (0,1) โดยถา 1 2 1 กระบวนการจะเปนแบบเฟสไมตาสดและถา 1 2 1 กระบวนการจะเปนแบบเฟสตาสด ทาใหสามารถเลอกคณลกษณะในการทางานของกระบวนการได

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

บทท 5 ความรพนฐานการประยกตใชงานดานซอฟตแวร

5.1 การใชงานโปรแกรม Matlab

ส ำหรบโปรแกรมทใชในงำนวจยนคอ โปรแกรม MatLab ซงสำมำรถใชควบคมไดเปนกระบวนกำรไดอยำงด อกทงยงสำมำรถท ำงำนรวมกบกำรด ADC และ DAC ของบรษท Advantech รน PCI-1711 ได โปรแกรม Matlab จะถกใชในกำรจ ำลองกระบวนกำร ส ำหรบเครองมอหรอโปรแกรมยอยของโปรแกรม MatLab นนมอยมำก ผวจยจงขออธบำยถงสวนประกอบของโปรแกรมทใชเฉพำะในงำนวจยนเทำนน ซงรำยละเอยดแสดงไดดงตอไปน

5.1.1 โปรแกรม Simulink Simulink เปนโปรแกรมทเปนสวนทเพมเตมเขำมำในโปรแกรม MATLAB ซงเปน

โปรแกรมทพฒนำโดยบรษท Mathworks โดยเปนโปรแกรมทมควำมสำมำรถในกำรแกปญหำทำงคณตศำสตรทมประสทธภำพสง ในสวนของ Simulink นนเปนเครองมอทใชในกำรเขยนโปรแกรมเพอหำค ำตอบของสมกำรทำงคณตศำสตรโดยใชลกษณะกำรโปรแกรมในรปแบบของ Block Diagram เปนหลก โดยเฉพำะอยำงยงระบบสมกำรเชงอนพนธซงมกจะพบปญหำในกำรหำ Closed Form Solution หรอกำรหำค ำตอบเมอเทยบกบเวลำในชวงเวลำใดๆ และเนองจำกระบบทำงวศวกรรมโดยสวนใหญจะสำมำรถอธบำยดวยระบบสมกำรเชงอนพนธ เชนกนดงนน Simulink จะเขำมำมบทบำทในกำรท ำใหกำรจ ำลองกำรตอบสนองของระบบมควำมสะดวกมำกยงขน

ส ำหรบองคประกอบของโปรแกรมนนไมวำจะเปนวงจรทำงตรรกศำสตรไปจนถง ระบบควบคมส ำหรบระบบพลศำสตรทซบซอนจะสำมำรถสรำงแบบจ ำลองไดโดยอำศยเพยง Building Blocks พนฐำนทมมำใหจำก Simulink Libraries นอกเหนอจำกนนยงมเครองมอใน สวนอนๆ ทในปจจบนไดเพมเตมเขำมำเพอใหกำรใชงำนมประสทธภำพมำกยงขน เชน Fuzzy Logic Toolbox, Neural Network Toolbox, Digital Signal Processing (DSP) Toolbox หรอ อนๆ ซงในปจจบนพบวำเครองมอตำงๆ ทมให สำมำรถท ำใหกำรจ ำลองหรอวเครำะหกำรท ำงำนของ ระบบสำมำรถท ำไดตงแตระบบทมควำมงำย จนถงระบบทมควำมซบซอนอยำงมำกโดยไมตอง มกำรเขยนโปรแกรมเพมเตมแตอยำงใด

5.1.1.1 กำรจ ำลองระบบพลศำสตร (Dynamic System Simulation) ดวย Simulink ในปจจบนคอมพวเตอรไดเขำมำมสวนชวยท ำใหกำรแกปญหำทำงวศวกรรมได

ใชประโยชนจำกคณตศำสตรอยำงเตมรปแบบในกำรจ ำลองระบบทำงพลศำสตรใดๆ โดยไมตองอำศยกำรศกษำหรอทดลองจำกระบบทำงกำยภำพจรงโดยกำรจ ำลองกำรท ำงำนของระบบพลศำสตร (Dynamic System Simulation) ดงกลำวนน ไดรบกำรพสจนแลววำมประโยชนอยำงมหำศำลในกำรท ำงำนทำงวศวกรรม โดยเฉพำะอยำงยงในงำนทำงดำนกำรออกแบบระบบ (System Design) และงำนกำรออกแบบระบบควบคม (Controller System Design) ทงนเนองจำกกำรจ ำลองปญหำชวยประหยดทงงบประมำณและเวลำ (Prototype) ของระบบทำงกำยภำพทสนใจซงในอดตจะตองสญเสยใหกบกำรสรำงระบบตนแบบ

5.1.1.2 หลกกำรของสญญำณและกำรไหลของตรรก (Signal and Logic Flow) ในโปรแกรม Simulink นนกำรจ ำลองปญหำจะอำศยกำรสรำงแผนภม

(Simulation Diagram) เพอกำรก ำเนด กำรรบ หรอสงผำนสญญำณ หรอขอมลทตองกำรทรำบ ในแผนภมทถกสรำงขนขอมล จำกบลอกประเภทตำงๆ จะถกสงผำนไปสบลอกอนๆ โดยเสนสญญำณท

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

25

เชอมตอระหวำง บลอกนนๆ สญญำณสำมำรถทจะถกสรำงและสงไปสบลอกอนๆ ทงแบบสถตยและแบบแปรผนขอมลสำมำรถปอนใหแกฟงกชนเพอกำรกระท ำทำงตรรกศำสตรหรอทำงคณตศำสตร ขอมลสำมำรถทจะถกสงไปสแหลงทงขอมล (Sink) ซงสำมำรถทจะแสดงใหเหนในลกษณะของ Oscilloscope หรอ Display หรอแมกระทงเกบในรปของไฟล (Save to Files) สงทตองพงระวงในกำรจ ำลองปญหำนน ขอมลตำงๆ จะถก ด ำเนนกำร รบและสง ในลกษณะเปนชวงเวลำ (Discrete Times) เทำนน ดงนน Step Time หรอ Simulation Time Step หรอ Integration Time Step ทก ำหนดเพอกำรจ ำลองปญหำนนจะเปน สวนทส ำคญอยำงยงโดยกำรเลอกใช Step Time ทเหมำะสมจะถกก ำหนดโดยระบบยอยทมกำร ตอบสนองเรวทสดในแผนภมทก ำหนดขน

ภาพท 5.1 ลกษณะของโปรแกรม Simulink

ในโปรแกรม Simulink นนกำรจ ำลองปญหำจะอำศยกำรสรำงแผนภม (Simulation Diagram) เพอกำรก ำเนด กำรรบ หรอสงผำนสญญำณ หรอขอมลทตองกำรทรำบ ในแผนภมทถกสรำงขนขอมล จำกบลอกประเภทตำงๆ จะถกสงผำนไปสบลอกอนๆ โดยเสนสญญำณท

5.1.1.3 กำรเชอมตอบลอก ในกำรเชอมตอบลอกบน Simulation Diagram นน ใหกดเมำสปมซำยท

Output ของ บลอกหนงแลวคำงปมเอำไวโดยเคอรเซอรของเมำสจะเปลยนรปเปนเครองหมำยบวก หลงจำกนนลำก (Drag) เมำส (จะเหนเสนประเกดขนและวงตำมเครองหมำยบวกดงกลำว) จำกบลอกหนง ไปส Input ของบลอกทตองกำรจะเชอมตอ เมอปลอยเมำสปมซำยท Input ของอกบลอกหนงแลวเสนประจะเปลยนเปนเสนทบแสดงถงกำรเชอมตอกนของบลอกทงสอง

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

26

5.1.1.4 กลมของบลอกทใชงำนบอยในเบองตน 1) แหลงก ำเนดสญญำณ (Sources) และแหลงทงสญญำณ (Sinks)

กลมบลอกแหลงก ำเนดสญญำณ (Sources) ทก ำหนดมำให ประกอบดวยแหลงก ำเนดขอมลหรอสญญำณ ทใชบอยในกำรวเครำะหระบบทำงพลศำสตร เชน แหลงก ำเนดคำคงท (Constant) แหลงก ำเนดสญญำณคลนซำยน (Sinusoidal Wave) แหลงก ำเนดสญญำณแบบ Step หรออนๆ นอกจำกนยงมแหลงก ำเนดสญญำณทท ำหนำทเสมอน Signal Generator รปทใชในกำรทดลองทำงวศวกรรมอนๆ หรอแหลงก ำเนดสญญำณนำฬกำ (Clock) ทมกจะใชบอยเพอ จบเวลำของกำรจ ำลองปญหำ หรออนๆ กลมบลอกแหลงทงสญญำณ (Sinks) เปนกลมบลอกทมกจะใชในกำรเกบสญญำณท ตองกำรมำกกวำกำรทงสญญำณอยำงทชอก ำหนด โดยทวไปแลวบลอกทจะใชบอยคอบลอกของ Scope ประเภทตำงๆ เพอตรวจสอบลกษณะกำรเปลยนแปลงของสญญำณในจดใดๆ ของระบบทก ำลงถกจ ำลองในขณะทก ำลงท ำกำรจ ำลอง หรอบลอกทเกบสญญำณ (To Workspace) เพอใชในกำรด ำเนนกำรอนๆ ทพนทท ำงำนของ MATLAB ภำพท 5.2 แสดงบลอกตำงๆ ของทงแหลงก ำเนด และแหลงสญญำณ ของ Simulink

ภาพท 5.2 แสดงบลอกตำงๆ ของแหลงก ำเนดสญญำณ (Sources) และแหลงสญญำณ (Sinks)

2) ระบบตอเนอง (Continuous) และระบบไมตอเนอง (Discrete) กลมบลอกของระบบตอเนอง (Continuous System) หรอระบบไม

ตอเนอง (Discrete System) เปนอกกลมหนงทมกำรใชในกำรจ ำลองปญหำบอย ระบบพลศำสตรทกระบบ สำมำรถทจะถกวเครำะหในลกษณะของระบบตอเนอง (Continuous System) หรอระบบไมตอเนอง (Discrete System) ซงไมวำระบบจะถกจ ำลองในลกษณะใด โปรแกรม Simulink นนสำมำรถ ตอบสนองตอลกษณะรปแบบของระบบไดในหลำยลกษณะ เชน Transfer Function หรอ Integration Blocks หรอ Delay Blocks หรออนๆ ภำพท 5.3 แสดงลกษณะบลอกทใชในกำรก ำหนด ระบบในลกษณะตำงๆ ของทงระบบตอเนอง (Continuous System) หรอระบบไมตอเนอง (Discrete System) ของ Simulink

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

27

ภาพท 5.3 แสดงบลอกตำงๆ ภำยในกลมบลอกของระบบตอเนอง (Continuous System) และระบบไมตอเนอง (Discrete System)

3) กำรด ำเนนกำรทำงคณตศำสตร (Math Operations)

กลมบลอกกำรด ำเนนกำรทำงคณตศำสตรเปนอกกลมหนงทมกำรใชในกำรจ ำลองปญหำบอย กลมบลอกนจะประกอบไปดวยบลอกยอยๆ ทมหนำทเกยวของกบกำรด ำเนนกำรตำงๆ ทำงคณตศำสตร เชน กำรน ำสญญำณมำบวกกน (Sum) กำรคณสญญำณดวยคำคงท (Gain) หรออนๆ ภำพท 5.4 แสดงลกษณะบลอกยอยในกลมบลอกกำรด ำเนนกำรทำงคณตศำสตร ของ Simulink

ภาพท 5.4 แสดงบลอกตำงๆ ภำยในกลมบลอกกำรด ำเนนกำรทำงคณตศำสตร (Math Operations)

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

28

4) ควำมไมตอเนอง (Discontinuities) ขอไดเปรยบขอหนงของโปรแกรม Simulink คอควำมสำมำรถในกำร

จ ำลองระบบแบบไมเปนเชงเสน (Nonlinear System Simulation) ซงในกำรหำค ำตอบดวยมอ หรอกำรหำ Closed Form Solutionโดยทวไปจะเปนกำรยำกฟงกชนหรอลกษณะของควำมไมเปนเชงเสนทพบบอยคอ Saturation, Signum, Limited Slew Rate หรออนๆ ภำพท 5.4 แสดงกลมบลอก Discontinuities ซง แสดงควำมไมเปนเชงเสนซงสำมำรถใชในกำรจ ำลองปรำกฏกำรณทำงวศวกรรมไดหลำยเหตกำรณ ยกตวอยำงเชนกำรใช Saturation บลอกมกจะใชแทนขอจ ำกดทำงกำยภำพเชนขดจ ำกดของแรงดนทำงเขำมอเตอรไฟฟำหรอระดงแรงดนสงสดในระบบไอดรอลกส บลอก Switches เปนอก บลอกหนงทใชบอย เปนบลอกทใชในกำรจ ำลองปญหำ IF-THEN เชนเดยวกบทพบในกำรเขยน โปรแกรมโดยทวไป บลอก Slew Rates ใชในกำรจ ำกดอตรำกำรเปลยนแปลงของคำทำงกำยภำพ เชน ควำมเรวของมอเตอรไฟฟำกระแสตรงเปนตน

5) ทำงเดนสญญำณ (Signal Routing) ในกำรจ ำลองระบบทมควำมซบซอน บำงครงมควำมจ ำเปนทจะตองม

กำรรบ/สง สญญำณจำกสวนหนงของระบบ ไปสอกสวนหนงของระบบ ซงกำรใชเสนเชอมอำจจะไมสะดวกในกำรท ำงำนซงบลอกในชดนเปนประเภท GOTO บลอกหรอ FROM บลอกบลอกประเภท Multiplexingจะมประโยชนในกำรจดระเบยบของแผนภมใหมควำมเปนระเบยบมำกขนภำพท 5.5 แสดงกลมบลอก Signal Routing

6) กำรก ำหนดคำคงทในกำรจ ำลองปญหำ (Parameters Configuration) กำรจ ำลองปญหำบนคอมพวเตอรจะตองอำศยเทคนคของระเบยบวธ

เชงตวเลข(Numerical Method) ในกำรแกปญหำและหำค ำตอบของสมกำรเชงอนพนธ ส ำหรบโปรแกรม Simulink นน ระบบในรปแบบตำงๆ สำมำรถทจะจ ำลองทงในแบบของระบบตอเนอง (Continuous System) หรอระบบไมตอเนอง (Discrete System) ขนอยกบลกษณะองคประกอบของระบบยอย กำรจ ำลองสำมำรถทจะถกก ำหนดใหเรม หรอหยดทชวงเวลำ หรอสวนหนงของเวลำไดตำมก ำหนด ขอสงเกตทตองพงระวงคอระยะเวลำทสนใจในกำรจ ำลองปญหำ กบระยะเวลำทใช ในกำรจ ำลอง ปญหำ หรอระยะเวลำทคอมพวเตอรใชในกำรหำค ำตอบของปญหำทสนใจจะไมตรงกน เชนคอมพวเตอรอำจจะใชระยะเวลำในกำรจ ำลองกำรตอบสนองในชวง 10 นำท ของระบบทสนใจ เพยง 1 วนำท เปนตน ในกำรจ ำลองแบบปญหำโดยใชระเบยบวธเชงตวเลขประเภทท Step Size มคำไมคงทนน (Variable Step Size) Step Size ทมำกทสดและนอยทสดสำมำรถก ำหนดได อยำงไรกตำมระเบยบวธเชงตวเลขประเภท Step Size คงท (Fixed Step Size) เปนวธทมกจะนยมใชในกำรจ ำลองปญหำ ทงนเนองจำกสำมำรถระบชวงเวลำ หรอจดของเวลำทสนใจไดอยำงแมนย ำ Step Size ทใชในกำรจ ำลองปญหำจะตองมกำรก ำหนดและจะมคำขนอยกบลกษณะของระบบพลศำสตรทสนใจ เชน ในระบบทำงควำมรอน Step Size อำจจะอยประมำณ 2 – 3 วนำท ในขณะทระบบคอบคมมอเตอรอำจจ ำเปนทจะตองใช Step Size ทมคำนอยถง 0.002 – 0.003 วนำท โดยทวไป กฏทใชใน กำรเลอก Step Size จะอยทประมำณอยำงนอย 4 – 20 เทำ ของระบบทมกำรตอบสนองทเรวทสด

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

29

ภาพท 5.5 แสดงกลมบลอก Discontinuities และกลม Signal Routing

ภาพท 5.6 แสดงหนำตำงทใชในกำรก ำหนดคำคงทในกำรจ ำลองปญหำ (Configuration Parameters)

5.1.1.5 กำรสรำงแบบจ ำลองระบบควบคม กำรสรำงแบบจ ำลองของระบบควบคมใน Simulink นนตองท ำกำรสรำง

หนำตำง ส ำหรบสรำงแบบจ ำลองขนมำกอนซงขนตอนในกำรสรำงแบบจ ำลองระบบควบคมท ำไดดงน 1) เลอก เมน File --> New --> Model จำกนนจะปรำกฏหนำตำงขนมำ

แสดงไดดงภำพท 5.7 ซงหนำตำงนจะใชส ำหรบกำรวำงบลอกทเลอกมำจำก Simulink Library Browser

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

30

ภาพท 5.7 หนำตำงส ำหรบสรำงแบบจ ำลอง

ในสวนบนของหนำตำงส ำหรบสรำงแบบจ ำลองจะเปนเมนบำรส ำหรบค ำสงตำงๆ ดงน

- เมน File เปนค ำสงเกยวกบกำรจดกำรทำมดวนแฟมขอมลทงหมด เชน กำรเปดไฟล กำรบนทกไฟล และกำรก ำหนดคณลกษณะของโปรแกรม Simulink เมน Edit เปนค ำสงเกยวกบกำรแกไขแบบจ ำลองทสรำงขนมำ

- เมน Edit เปนค ำสงเกยวกบกำรแกไขแบบจ ำลองทสรำงขนมำ - เมน View เปนค ำสงเกยวกบกำรแสดงเครองมออปกรณบน

หนำจอแบบจ ำลอง - เมน Simulation เปนค ำสงเกยวกบกำรจดกำรกำรจ ำลองกำร

ท ำงำนของระบบควบคมทท ำกำรสรำงขนมำ - เมน Format เปนค ำสงเกยวกนรปแบบกำรแสดงผมบน

หนำจอจ ำลอง - เมน Tools เปนค ำสงเกยวกบกำรเลอกใชเครองมอตำง ๆ - เมน Help เปนค ำสงเกยวกบกำรขอควำมชวยเหลอ

2) เมอท ำกำรสรำงหนำตำงส ำหรบสรำงแบบจ ำลองแลวท ำบลอกใน Simulink Library Browserมำวำงในหนำตำงส ำหรบสรำงแบบจ ำลองไดโดยท ำกำรคลกบลอกทตองกำรคำงไวจำกนนท ำกำรลำกมำไวในหนำตำงส ำหรบสรำงแบบจ ำลองจำกนนปลอยปมจะปรำกฏบลอกทตองกำรบน หนำตำงส ำหรบสรำงแบบจ ำลองแสดงไดดงภำพท 5.8

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

31

ภาพท 5.8 กำรเลอกบลอกทตองกำรจำก Simulink Library Browser

3) เมอไดบลอกทตองกำรแลวเรำสำมำรถน ำบลอกอนๆ มำวำงบนหนำตำงส ำหรบ สรำงแบบจ ำลองไดเชนกน ตอไปจะแสดงบลอกของระบบตวอยำง

ภาพท 5.9 บลอกของระบบตวอยำง

4) ภำพท 5.9 สงเกตไดวำแตละบลอกจะมชองสญญำณเขำและสญญำณออก ไวส ำหรบลำกเสนสญญำณเชอมตอระหวำงบลอกตำงๆ เขำดวยกนกำรลำกเสนเชอมตอระหวำงบลอกตำงๆ นน สำมำรถท ำไดโดยเลอนเมำสใหไปชทจดตอสญญำณของบลอกทตองกำร ตวชของเมำสจะเปลยนเปนเครองหมำยกำกบำท จำกนนคลกคำงไวแลวลำกตวชไปทจดตอสญญำณของบลอกทตองกำร แสดงไดดงภำพท 5.10

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

32

ภาพท 5.10 กำรเชอมตอสญญำณระหวำงบลอก

5) กำรเปลยนแปลงคำพำรำมเตอรของบลอกสำมำรถท ำไดโดยดบเบลคลกทบลอกซงจะ ปรำกฏไดอะลอกส ำหรบใหใสคำพำรำมเตอรของบลอก

ภาพท 5.11 กำรเปลยนแปลงคำพำรำมเตอรของบลอก

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

33

เพอใหเขำใจหลกกำรท ำงำนและวธกำรสรำงโปรแกรมดวย Simulink จะขอแสดงถงวธกำรสรำงแบบจ ำลองของระบบควบคมใน Simulink โดยกำรสรำงแบบจ ำลองของกระบวนกำรใน Simulink นนสำมำรถแบงเปน 3 วธดวยกน คอ

1. กำรสรำงแบบจ ำลองกระบวนกำรจำกสมกำร Differential Equation 2. กำรสรำงแบบจ ำลองกระบวนกำรจำกทรำนสเฟอรฟงกชน 3. กำรสรำงแบบจ ำลองระบบควบคมจำกสมกำร State-Space

ในงำนวจยนจะใชวธกำรสรำงแบบจ ำลองกระบวนกำรจำกทรำนสเฟอรฟงกชน วธกำรสรำงแบบจ ำลองของระบบทแสดงอยในรป 5.12 Transfer Function นนจะใชบลอก Transfer Fcn แสดงแทนระบบ กำรใสคำโพลโนเมยลในสวนของ Numerator และ Denominator นนท ำไดโดยดบเบลคลกทบลอกซงจะปรำกฏไดอะลอกทใหใสคำขนมำแสดงไดดงภำพท 5.13 โดยกำรใสคำลงไปนนมเงอนไขอยวำสวน Numerator นนตองมอนดบนอยกวำ สวน Denominator ซงสงเกตไดวำกำรสรำงแบบจ ำลองของระบบจำก Transfer Function นนจะท ำกำรวดผลตอบสนองไดทสวนเอำตพตของระบบเทำนน

ภาพท 5.12 ไดอะลอกใสคำพำรำมเตอรของบลอก Transfer Function

ภาพท 5.13 แบบจ ำลองระบบทำงกลในรปแบบของ Transfer Function

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

34

5.1.2 กำรตดตงโปรแกรมเพอใชงำน Real Time Windows Target

5.1.2.1 Simulink external model interface ในหนำตำง Command Windows ของโปรแกรม MATLAB ใหพมพค ำสง >> mex –setup

จำกนนโปรแกรม Matlab จะแสดงขอควำม

Please choose your compiler for building external interface (MEX) files: Would you like mex to locate installed compilers [y]/n?

ใหพมพ y เพอยนยน จำกนนโปรแกรม Matlab จะแสดงขอควำมเพอใหเลอก Compiler ทตองกำร

Select a compiler: [1] Lcc-win32 C 2.4.1 in C:\PROGRA~1\MATLAB\R2007a\sys\lcc [2] Microsoft Visual C++ 2005 in C:\Program Files\Microsoft Visual Studio 8 [3] Microsoft Visual C++ 6.0 in C:\Program Files\Microsoft Visual Studio [0] None

ในกำรวจยนผวจยจะเลอก Compiler Microsoft Visual C++ ซงท ำไดโดยกำรพมพเลข 2

Complier: 2

โปรแกรม Matlab จะแสดงขอควำมเพอใหเรำยนยน Compiler ทเหลอ Please verify your choices: Compiler: Microsoft Visual C++ 2005 Location: C:\Program Files\Microsoft Visual Studio 8 Are these correct?([y]/n):

ถำยนยนใหพมพ y แตถำไมยนยนใหพมพ n จำกนนโปรแกรมจะอพเดต

ขอมลของ Compiler และสนสดกำรตดตง Compiler โดยสงเกตขอควำมในโปรแกรม Matlab ดงตวอยำงดำนลำง

Trying to update options file: C:\Documents and Settings\xp\Application Data\MathWorks\MATLAB\R2007a\mexopts.bat From template: C:\PROGRA~1\MATLAB\R2007a\bin\win32\mexopts\ msvc80opts.bat Done . . .

5.1.2.2 กำรตดตง Real Time Windows Target Kernal ในหนำตำง Command Windows ของโปรแกรม MATLAB ใหพมพค ำสง

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

35

>> rtwintgt –install

จำกนนโปรแกรม Matlab จะแสดงขอควำมเพอเรมตนกำรตดตง You are going to install the Real-Time Windows Target kernel. Do you want to proceed? [y] :

พมพ y เพอยนยนกำรเรมตนกำรตดตง Real Time Windows Target Kernal หลงจำกนนโปรแกรมจะด ำเนนกำรตดตง เมอเสรจเรยบรอยแลวโปรแกรมจะแสดงขอควำม

The Real-Time Windows Target kernel has been successfully installed.

5.1.2.3 กำรก ำหนดคำพำรำมเตอรใน Simulink ส ำหรบ Real Time Workshop หลงจำกทสรำง Simulink Model จะตองก ำหนดพำรำมเตอรในหนำตำง

Simulation เพอให Real-Time Workshop สำมำรถสรำง Code ภำษำ C และสรำง Real-Time Application ได ซงมขนตอนในกำรก ำหนด ดงน

1) ในหนำตำง Simulink ไปท Simulation เมน คลกทConfiguration Parameters

2) คลกทหมวดของ Hardware Implementation 3) จำกรำยกำร Device Type เลอก 32-bit Real Time Windows Target 4) Emulation hardware เลอก None 5) คลกทหมวด Real Time Workshop 6) Target selection คลก Browse ทรำยกำร RTW system target file

เลอก system target file ส ำหรบ Real Time Windows Target และคลก Ok

7) คลก Ok เพอยนยนกำรเปลยนแปลงและปด Dialog box

ภาพท 5.14 Hardware Implementation

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

36

ภาพท 5.15 RTW System Target File

5.2 การเขยนโปรแกรมภาษาซส าหรบหนวยประมวลผล ARM7

5.2.1 สถำปตยกรรมไมโครคอนโทรลเลอร ARM7 (ADuC7024) ARM7 มรปแบบกำรออกแบบพนฐำนตำมสถำปตยกรรมของ Von Neumann ดวยบส

ขนำด 32 บต ซงสำมำรถรบสงค ำสงและขอมลขนำด 8 บต, 16 บตหรอ 32 บต โดยทวไปมคณสมบตดงน ใชรปแบบค ำสงแบบ load and store หมำยควำมวำกอนกำรประมวลผลจะตองท ำกำร

โหลดขอมลจำกรจสเตอรหรอหนวยควำมจ ำกอนหลงจำกนนจงกำรประมวลผลซงผลลพธทไดอำจจะเกบอยในรจสเตอรเพอไปสกระบวนกำรถดไปหรออำจจะบนทกกลบลงสหนวยควำมจ ำ

มโหมดของกำรอำงต ำแหนงแอดเดรสทไมมำกนก โดยสำมำรถกระท ำไดโดยอำงต ำแหนงจำกรจสเตอรและค ำสงเพยงค ำสงเดยวเทำนน

ขนำดของค ำสงมขนำดคงท (32 บต) ส ำหรบ ARM แลว ไดเพมควำมสำมำรถเพมเตม คอ ม shifter หรอตวเลอนบตแยกตำงหำกกอนทจะเขำ ALU (Arithmetic Logic Unit)

เพอเพมควำมเรวในกำรประมวลผล มโหมดกำรอำงต ำแหนงแบบ Auto-increment และ Auto-decrement เพอชวยให

กำรท ำงำนแบบลปงำยขน สำมำรถเพมเงอนไขภำยในแตละค ำสงเพอลดกำรสญเสยจำกกำรท ำงำนของ pipeline

ซงจะสงผลใหกำรท ำงำนเรวขน

1) กระบวนกำรแบบไปปไลน (instruction pipeline) ARM7 ใชไปปไลน 3 ระดบในกำรในกำรเพมควำมเรวในกำรท ำงำนกบชดค ำสง ทงน

คำในรจสเตอร program counter (PC) ทใชในกำรเอกซควตค ำสงจะมคำแอดเดรสน ำหนำไปสองค ำสงเสมอ ท ำใหเกดหลำยกำรปฏบตงำนในเวลำเดยวกน ดงรป จะเหนวำขณะทซพยท ำกำรเอกซควตค ำสงท 1

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

37

ซพยกถอดรหสค ำสงท 2 และท ำกำรเฟตชค ำสงท 3 จำกหนวยควำมจ ำไปพรอมกน. ท ำใหซพย ARM7ท ำงำนไดอยำงรวดเรวและสำมำรถรองรบกำรประมวลผลขอมลขนำดใหญ

ภาพท 5.16 แสดงกระบวนกำรท ำงำนของไปปไลนใน ARM7โปรเซสเซอร

2) กำรจดรปแบบขอมลในหนวยควำมจ ำ อนเตอรเฟส กบหนวยควำมจ ำของซพย ARM7 ถกออกแบบใหมสมรรถนะดเยยม

และลดกำรใชหนวยควำมจ ำใหนอยทสด สญญำณควบคมควำมเรวถกสงผำนทำงทอเพอใหมฟงกชนควบคมระบบทรองรบโหมดกำรเขำถงทรวดเรวโดยเทคโนโลยหนวยควำมจ ำแบบตำงๆ ARM7 มชนดของไซเคล 4 แบบ ดงน

- แบบภำยใน Internal - แบบไมเปนล ำดบ Non-sequential - แบบเปนล ำดบ Sequential - Coprocessor transfer

3) Coprocessor โปรเซสเซอรรวมเปนวงจรพเศษในชปไมโครโพรเซสเวอร ทไดรบกำรออกแบบให

ควบคมหรอท ำฟงกชนพเศษเรวกวำวงจรไมโครโพรเซสเวอรพนฐำน โดย ARM7 coprocessors ประกอบดวย

• Instruction pipeline • Instruction decode logic • Handshake logic • Register bank • Processing logic พเศษ สถำนะกำรท ำงำน : สถำนะกำรท ำงำนของ ARM แบงเปน 7 แบบ ไดแก 1. User mode (usr) เปนโหมดส ำหรบกำรเอกซควตโปรแกรมทใชทวไป ในโหมดน

จะไมสำมำรถดสเอเบลอนเตอรรปทได 2. Fast Interrupt mode (fiq) เปนโหมดส ำหรบโปรแกรมอนเตอรรปททมล ำดบ

ควำมส ำคญสงกวำอนเตอรรปทตวอน 3. Interrupt mode (irq) เปนโหมดส ำหรบโปรแกรมอนเตอรรปททวไป 4. Supervisor (svc) เปนโหมดส ำหรบระบบปฏบตกำร

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

38

5. Abort (abt) เปนโหมดส ำหรบกำรเขำถงหนวยควำมจ ำทไมมอยจรงเพอปองกนกำรท ำงำนของระบบ

6. Undefined (und) เปนโหมดส ำหรบกำรเอกซควตค ำสงท ARM ไมรจก 7. System (SYS) – เปน user mode แบบพเศษส ำหรบระบบปฏบตกำร

ในแตละโหมดจะมลกษณะกำรใชงำนทแตกตำงกน ดงรป

ภาพท 5.17 ลกษณะกำรใชงำน ARM ทง 7 โหมด

โหมดอนนอกจำก user mode ถอเปน privileged mode ซงกคอโหมด พเศษทใชส ำหรบใหบรกำรอนเทอรรฟทเอกเซปชนหรอกำรเขำถง resource ทถกปองกน

4) ARM registers ARM มรจสเตอรแบบ 32 บต ทงหมด 37 ตว แบงเปน รจสเตอรส ำหรบใชงำนทวไป

30 ตว รจสเตอรแสดงสถำนะ 6 ตว และ programs counter 1 ตว หนำทของรจสเตอรทส ำคญสรปไดดงน

Stack pointer รจสเตอร R13 ท ำหนำทเกบ ต ำแหนงของค ำสงในหนวยควำมจ ำทตองท ำเปนล ำดบถดไป เมอท ำงำนในโปรแกรมยอยเสรจแลวใหแก Program Counter Register

Link register รจสเตอร R14 ท ำหนำทในกำรเกบคำทอยของค ำสงถดไปหลงจำกค ำสง Branch with Link (BL) ทใชเวลำเรยกโปรแกรมยอยของ ARM

Program counter รจสเตอร R15 ท ำหนำทเปน Program Counter ท ำกำรชไปยงต ำแหนงของค ำสงถดไป เมอเรมท ำกำร execute ค ำสงปจจบน

CPSR (Current Program Status Register) เกบคำสถำนะโปรแกรม ณ เวลำปจจบน

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

39

SPSR (Saved Program Status Register) เกบคำของ CPSR กอนจะเกดเอกเซปชน

ARM Instruction set แบงได 4 ประเภทคอ 1) Branch Instruction - General branch instruction - Branch with Link - Software interrupt (SWI) ใชเรยกเพอเขำสกำรท ำงำนของระบบปฏบตกำร - THUMB instruction (16 บต) 2) Data - processing Instruction - Arithmetic/logic instructions ม 16ค ำสง ซงมรปแบบรวมกน - Multiply instructions มแบบ 32 บต และ 64 บต - Status register transfer instruction โหลดหรอเกบคำจำก SPSR หรอ CPSR 3) Load - store Instruction แบงเปน 3 ประเภทคอ - Load or store the value of a single register คอ ในกำรโหลดคำมำเกบไว

ในรจสเตอรสำมำรถท ำไดครงละ 32 บต, 16 บต หรอ 8 บต จำก memory ในกำรstore ก - Load and store multiple register values สำมำรถโหลดหรอเกบคำในชวง

ของMemory โดยเพมหรอลด address ไดโดยอตโนมต - ในกำรอำงแอดเดรสแบบ Increment หรอ decrement จะเปนสงทระบวำคำ

ของ pointer จะเลอนขนหรอเลอนลง และในสวนของ pre หรอ post จะระบวำขณะนน pointer ชในจดทมขอมลอยหรอไม ถำมอยตองเลอนpoint กอนแลวคอยใสคำลงไป หรอถำไมมขอมลอยจะใสคำกอน แลวจงเลอน pointer ไป

- Swap a register with the value of a memory location คอกำรสลบคำระหวำงregisterโดยผำน memory หรอสลบคำระหวำง memory กบ register ได

4) Co – processor Instruction - Data-processing instructions ใชจดกำรกำรจดกำรภำยในของโปรเซสเซอร

รวม - Register transfers ยำยคำภำยในโปรเซสเซอรรวมมำยง ARM รจสเตอร หรอ

จำกARM รจสเตอรออกไป - Data-transfer instructions ยำยขอมลของโปรเซสเซอรรวมมำยงหรอออก

จำก memory โดยต ำแหนงจะถกค ำนวณโดย ARM

5.2.2 โปรแกรม Keil uVision 3.11 โปรแกรม Keil RealView [11] สำมำรถดำวนโหลดไดจำกเวบไซดของบรษท Keil ท

http//keil.com แลวเลอกทเมน Software Download จำกนนเลอกท Evaluation Software โดยกอนทจะท ำกำรดำวนโหลดซอฟตแวรจะตองท ำกำรลงทะเบยนกบทำงเวบไซดกอนจงจะสำมำรถดำวนโหลดได หลงจำกดำวนโหลดเสรจสนจะไดไฟลทมนำมสกล *.exe (ในทนคอ rvmdk311.exe) ดบเบลคลกทไฟลเพอตดตงโปรแกรม โดยโปรแกรมจะแสดงหนำตำงส ำหรบตดตงโปรแกรมดงภำพท 5.17

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

40

ภาพท 5.18 หนำตำง Setup Real View Microcontroller Development Kit Version 3.11

เมอคลกปม Next จะปรำกฎหนำตำง License Agreement เพอแจงลขสทธของโปรแกรมคลกท หนำขอควำม I agree to all terms of proceeding License Agreement แลวคลกปม Next

หลงจำกนนจะมหนำตำง Folder Selection เลอกโฟลเดอรส ำหรบกำรตดตงโปรแกรม ในทนใหเลอกเปน C:\Keil ตำมทเครองก ำหนดมำให แลวคลก Next จะปรำกฎหนำตำง customer Information เพอกรอกขอมลของผใชงำน ซงควรจะกรอกขอมลตำมควำมเปนจรง โดยเฉพำะในชองของ e-mail ถำไมกรอกขอมลจะไมสำมำรถคลกปม Next เพอด ำเนนกำรในขนตอนตอไปได แสดงดงภำพท 5.18

ภาพท 5.19 หนำตำง customer Information

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

41

หลงจำกนนขนตอนกำรตดตงโปรแกรมกจะเรมขน หลงจำกเสรจเรยบรอยแลวจะปรำกฏหนำตำง Setup Complete เพอเปนกำรยนยนกำรตดตงโปรแกรมใหคลกทปม Finish เปนกำรเสรจสนกำรตดตงโปรแกรม แสดงดงรป 5.19

ภาพท 5.20 หนำตำงแสดงกำรสนสดกำรตดตงโปรแกรม

5.2.2.1 กำรเรมตนใชงำนโปรแกรม Keil uVision3 กำรใชงำนโปรแกรม Keil RealView ในกำรเขยนโปรแกรมนนจะตองท ำกำร

สรำงโพรเจกตขนมำและท ำกำรก ำหนดคำกำรใชงำนใหถกตองเสยกอนจงจะสำมำรถใชงำนโปรแกรมได โดยเรมตนจำกกำรเปดโปรแกรม Keil uVision3 ขนมำ แสดงดงภำพท 4.20

ภาพท 5.21 หนำตำงหลกของโปรแกรม Keil uVision

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

42

ก ำหนดคำเลอกตวคอมไพเลอรในกำรแปลค ำสงใหกบโปรแกรม Keil uVision3 โดยคลกท Project -> Manage -> Components, Environments, Books…. เพอเปดหนำตำง Components, Environment and Books ซงมสวนทตองก ำหนดอย 2 จดคอ จดแรกในสวนของ Select ARM Development Tool จะมคอมไพเลอรใหเลอกอย 2 ตว ซงในสวนนใหเลอกคอมไพเลอร RealView Compiler และอกจดหนงทตองก ำหนดคอในสวนของ Development Tool Folder โดยท Tool Base Folder ใหก ำหนดไวท C:\Keil\ARM เสรจแลวกดปม OK

ภาพท 5.22 หนำตำง Components, Environment and Books

ตอจำกนนจะตองท ำกำรสรำงโพรเจกตใหมขนมำโดยเลอกท Project -> New uVision Project จะปรำกฎหนำตำง Create New Project ขนมำ แลวท ำกำรสรำงโฟลเดอรใหมขนมำ แลวตงชอโฟลเดอร จำกนนตงชอโพรเจกตทตองกำร แลวท ำกำรบนทกโพรเจกต แสดงดงภำพท 5.22

ภาพท 5.23 หนำตำง Create New Project

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

43

เมอสงกดปม Save แลวจะปรำกฎหนำตำง Select Device for Target ‘Target 1’ เพอใหผใชเลอก MCU ทใชงำน ซงในทนเลอกไมโครคอนโทรลเลอรของบรษท Analog Devices จำกนนจะมรำยละเอยดเกยวกบเบอรของไมโครคอนโทรลเลอร Analog Devices ซงเบอรทใชคอ ADuC7024 จำกนนกดปม OK โปรแกรมจะถำมวำตองกำรทจะเพมไฟล Startup เขำไปในโพรเจกตหรอไม (ถำตองกำรกด YES ถำไมกด NO)

ภาพท 5.24 หนำตำง Select Device for Target

หลงจำกขนตอนนเรำกจะสำมำรถเรมเขยนโปรแกรมไดแลวโดยเลอกท File -> New... ซงจะปรำกฎหนำตำงส ำหรบเขยน Text File ขนมำ ไปทหนำตำง Text Editor ใหคลกขวำแลวเลอก Insert ‘#include <ADuC7024.H>’ ขอควำม #include <ADuc7024.H> จะถกแทรกในบรรทดท 1 หลงจำกทเขยนโปรแกรมเรยบรอยแลวใหบนทกไฟลทมนำมสกล .c

ภาพท 5.25 หนำตำง Add File to Group

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

44

ในสวนของ Project Workspace ในภำพท 5.24 จะมโฟลเดอร Target 1 คลกตรงเครองหมำยบวกจะมโฟลเดอรยอยชอ Source Group 1 ใหคลกขวำจะมเมนยอยใหเลอกท Add File to Group ‘Source Group 1’ แลวเลอกแอดไฟลโปรแกรม (นำมสกล .c) และไฟล Startup เขำมำในโพรเจกต จำกนนท ำกำรก ำหนดคำ Option ของ Project File โดยคลกปม Option for Target เพอเปดหนำตำง Option for Target ‘Target1’ เลอกแทป Target เพอก ำหนด MCU Target โดย ก ำหนดคำ Xtal เปน 0.032768 ดงภำพท 5.25

ภาพท 5.26 หนำตำงก ำหนด Options for Target

ตอไปเลอกแทปก ำหนด Output Information โดยเลอกท Output แลวคลกเลอก Create Executable และเลอกท Debug information และ Create HEX file ดงภำพท 5.26

ภาพท 5.27 หนำตำงก ำหนด Output Information

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

45

หลงจำกทเขยนโปรแกรมเรยบรอยแลวตองท ำกำร Compile และ Build โปรแกรมเสยกอนโดยในภำพท 5.27 มจดส ำหรบ Compile และ Build อย 3 แบบคอ Translate current file, Build target และ Rebuild all target file หลงจำกท Compile และ Build โปรแกรมเรยบรอยแลวในสวนดำนลำงคอ Output Window ทท ำหนำทรำยงำนผลของกำร Compile โปรแกรม ถำโปรแกรมถกตองทงหมดจะตองขน 0 Error(s), 0 Warning(s) แตถำมจดผดพลำดโปรแกรมกจะรำยงำนวำมทผดกทและผดทตรงไหน ซงจะชวยใหเรำสำมำรถแกไขโปรแกรมไดสะดวกขน

ภาพท 5.28 กำร compile และกำร Build โพรเจกต

5.2.2.2 กำร debug โปรแกรมภำษำ C ส ำหรบ ARM7 กำรดบคโปรแกรมเปนกำรตรวจสอบกำรท ำงำนของโปรแกรมทเรำเขยนขนมำ

วำมควำมถกตองและเปนไปตำมทเรำตองกำรหรอไม ซงสำมำรถตรวจสอบไดเปนล ำดบขนตอนอกทงยงตรวจหำจดผดของโปรแกรมไดดวย ซงหลงจำกทท ำกำรคอมไพลผำนแลวใหก ำหนดคำตำมภำพท 5.28 จำกนนใหคลกทปมดบค (ตำมภำพท 5.29 หรอเลอกทเมน Debug -> Start/Stop Debug Session โปรแกรมกจะเขำสโหมดดบค (โปรแกรมทใชในกำรดบคเปนโปรแกรมส ำหรบ LED ตดดบโดยพอรตทใชเปนพอรต P3.x)

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

46

ภาพท 5.29 ปม Build Target

เมอก ำหนดคำแลวใหไปท Debug -> Start/Stop Debug Session ดงแสดงในภำพท 5.29

ภาพท 5.30 กำรเขำสโหมด Simulation หรอ Debug

หลงจำกทเขำสโหมดดบคแลวใหเลอกท Peripherals -> General Purpose Input/Output ->GPIO Port (0-4) ดงภำพท 5.30

ภาพท 5.31 แสดงสถำนะเตรยมพรอม Simulator

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

47

ถงขนตอนนกสำมำรถ Run โปรแกรมไดแลว โดยไปท Debug -> Run หรอกด F5 ดงแสดงในภำพท 5.31

Step intoStep Over

Step Out

Run to

Cursor line

ภาพท 5.32 ปมกำร Debug แบบตำงๆ

5.2.2.3 กำรตดตงซอฟตแวร ARMWSD หลงจำกทเขยนโปรแกรมภำษำ C เสรจแลว ท ำกำรคอมไฟลจะไดไฟล

ภำษำเครองนำมสกล .hex ซงจะตองใชซอฟตแวร ARMWSD เพอดำวนโหลดไฟล .hex ทไดลงไปในหนวยควำมจ ำแฟลชของไมโครคอนโทรลเลอร ARM7 ผำนสำย RS-232 โดยทองคประกอบของซอฟตแวร ARMSWD จะมไฟล 3 ตวคอ ARMWSD.exe, armwsd.ini และ sample.hex กำรใชงำนโปรแกรม ARMWSD นนไมตองท ำกำรตดตงโปรแกรมกสำมำรถใชงำนได เพยงแตตองใหไฟลทง 3 ท ำงำนรวมกนโดยอำจวำงไวในโฟลเดอรเดยวกน วธกำรใชงำนเพยงแคคลกทไฟล ARMWSD.exe กพรอมใชงำน แสดงดงภำพท 5.32

ภาพท 5.33 หนำตำงกำรใชงำนของโปรแกรม ARMWSD

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

48

กำรใชงำนโปรแกรมเรมจำกคลกทปม Browse แลวเลอกไฟลทตองกำรดำวนโหลดลงไปยงไมโครคอนโทรลเลอร ARM7 (ไฟลทมนำมสกล .hex) จำกนนคลกทปม Configure จะมหนำตำง ARMWSD Configuration เพอใหก ำหนดคำในกำรดำวนโหลด โดยจะมสวนทตองก ำหนดคำอย 3 สวนคอ Serial Port เลอกพอรตใหตรงกบพอรตคอมพวเตอรทสำย RS-232 ตออย ในสวนของ Baud rate ใหเลอกคำ 9600 และในสวน Flash ใหคลกเลอกท Mass Erase, Program และ Verify แลวคลกปม OK เปนกำรเสรจสนกำรก ำหนดคำ กำรดำวนโหลดโปรแกรมท ำไดโดยกำรคลกทปม Start โปรแกรมกจะโหลดซอพตแวรลงไปยงไมโครคอนโทรเลอร แลวคลกปม RUN ไมโครคอนโทรเลอรกจะเรมกำรท ำงำน

ภาพท 5.34 กำร Configuration โปรแกรม ARMWSD กอนใชงำน

5.3 พนฐานการเขยนภาษาซ (Basic C For ARM7)

5.3.1 ควำมหมำยภำษำ C ส ำหรบ ARM7 ภำษำ C ส ำหรบ ARM7 คอ ภำษำทใชเขยนโปรแกรมเพอสงงำนและควบคม

ไมโครคอนโทรลเลอร ARM7 ซงภำษำ C ส ำหรบ ARM7 ถอวำเปนภำษำระดบกลำงมโครงสรำง (Structure) และไวยำกรณ (Syntax) เหมอนกบภำษำ C ทวไปควำมหมำยภำษำ C ส ำหรบ ARM73

กำรท ำงำนของภำษำซเรมจำกใช Editor เขยนโปรแกรมเมอบนทกเปนไฟลนำมสกล *.C จำกนนท ำกำรคอมไพลถำหำกไมมกำรผดพลำดจะไดไฟล *.Obj แลวท ำกำร Link ไฟล *.Obj เขำกบไฟล Libraries หำกไมมขอผดพลำดจะไดไฟล *.EXE

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

49

ภาพท 5.35 Flow Chart กำรประมวลผลภำษำซส ำหรบ ARM7

5.3.2 โครงสรำงโปรแกรมภำษำ C ส ำหรบ ARM7 1) Complier Directive คอ สวนทใชบอก Complier วำใหท ำอะไรกอน กอนท

complier จะท ำกำร Compile โปรแกรม เชน กำรรวมไฟลอนๆ เขำกบโปรแกรม กำรสรำงเงอนไขของกำร Compile โปรแกรมจะขนตนดวยเครองหมำย #

2) Functions คอ โปรแกรมยอย (Sub Program) ชนดหนงสำมำรถท ำงำนอยำงใดอยำงหนงเสรจสนภำยในตวเอง โดยท function อำจจะมกำรรบคำเขำ function และสงกลบในชอของ function หรออำจจะไมมกไดโดยฟงกชนในภำษำ C แบงไดเปน 2 ประเภทดวยกน คอ ฟงกชนทเรำสรำงขนมำเอง และฟงกชนทภำษำซสรำงมำเพอใหใชในกำรท ำงำนทวไป อยำงเชน ฟงกชนส ำหรบแสดงผล ฟงกชนทใชในกำรค ำนวณ หรอฟงกชนส ำหรบจดกำรกบไฟล เปนตน

3) สวนกำรประกำศ (Declarations) เปนสวนทใชก ำหนดประเภทของขอมลแบบตำงๆ เชนกำรประกำศตวแปร (Variable) กำรประกำศคำคงท (Constants) หรอชนดขอมล (Data Type) เปนตน

4) สวนของค ำสง (Executable Statements) เปนสวนของประโยคค ำสง ทมผลใหมกำรปฎบตกำรอยำงใดอยำงหนง สวนของค ำสงนมกเปนสวนทอยในขอบเขตของเครองหมำย {…}

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

50

ภาพท 5.36 โครงสรำงโปรแกรมภำษำซ 5.3.3 ตวแปรชนดตำง ๆ และคำคงท ภำษำ C ส ำหรบ ARM7 มโครงสรำงเหมอนกบภำษำ C ทวไปท ำใหกำรประกำศตวแปร

และคำคงทจงคลำยกน ตวแปรและคำคงท ทประกำศไวจะถกจองพนทและเกบคำไวในหนวยควำมจ ำ (RAM)

5.3.4 ชนดของตวแปรในภำษำซ

ตารางท 5.1 ชนดของตวแปรในภำษำซ ชนดของตวแปร ขนาด ชวงของขอมล การก าหนดชนดของตวแปร

1. Character 8 บต -128 ถง +127 char 2. Unsigned character 8 บต 0 ถง 255 unsigned char 3. Integer 16 บต -32768 ถง +32767 int 4. Unsigned integer 16 บต 0 ถง 65535 unsigned int 5. Long integer 32 บต -2147483648 ถง 2147483647 long int 6. Unsigned Long 32 บต 0 ถง 4,294,967,295 unsigned long int 7. Floating point 32 บต 3.4x10-38 ถง 3.4x10+38 float

1) Character ตวแปรชนดตวอกษรหรอจ ำนวนเตม 8 บต ใชเกบขอมลทเปนตวอกษร

หรอจ ำนวนเตมทมคำอยในชวง -128 ถง +127 2) Unsigned character ตวแปรชนดตวอกษรหรอจ ำนวนเตม 8 บต แบบไมคด

เครองหมำยใชเกบขอมลทเปนตวอกษรหรอจ ำนวนเตมบวกทมคำอยในชวง 0 ถง 255

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

51

3) Integer ตวแปรชนดจ ำนวนเตมขนำด 16 บต ใชเกบขอมลทเปนจ ำนวนเตมทมคำอยในชวง -32768 ถง +32767

4) Unsigned integer ตวแปรชนดจ ำนวนเตมขนำด 16 บต แบบไมคดเครองหมำยหรอจ ำนวนเตมบวก ใชเกบขอมลทเปนจ ำนวนเตมทมคำอยในชวง 0 ถง 65535

5) Long integer ตวแปรชนดจ ำนวนเตมขนำด 32 บต ใชเกบขอมลทเปนจ ำนวนเตมทมคำอยในชวง -2147483648 ถง +2147483648

6) Unsigned Long ตวแปรชนดจ ำนวนเตมขนำด 32 บต แบบไมคดเครองหมำยหรอจ ำนวนเตมบวก ใชเกบขอมลทเปนจ ำนวนเตมทมคำอยในชวง 0 ถง 4,294,967,295

7) Floating point ตวแปรชนดทศนยม ใชเกบขอมลเลขทศนยมทมคำอยในชวง 3.4x10-38 ถง 3.4x10+38

ตวอยำงกำรประกำศตวแบบ char และ int ARM7 จะไปจองพนในหนวยควำมไวตำมชนดของตวแปร คอ char = 1 Byte และ int = 2 Byte

ภาพท 5.37 ตวอยำงกำรประกำศตวแบบ char และ int

5.3.5 กำรประกำศตวแปร ในกำรเขยนโปรแกรมภำษำ C ส ำหรบ ARM7 กำรประกำศตวแปรเพอใชเกบคำขอมลม

รปดงน Syntax : ชนดของตวแปร ชอตวแปร;

ตวอยำง : char i; สรำงตวแปรชอ i ส ำหรบเกบคำขอมล-128 ถง 127 int j; สรำงตวแปรชอ j ส ำหรบเกบคำขอมล -32,768 ถง 32,767 unsigned int count; สรำงตวแปรชอ cont ส ำหรบเกบคำขอมล 0 ถง 65,535 long x; สรำงตวแปรชอ x ส ำหรบเกบคำขอมล -2,147,483,648 ถง 2,147,483,647 float y; สรำงตวแปรชอ y ส ำหรบเกบคำขอมลทศนยม

กำรประกำศตวแปรพรอมกบคำเรมตน Syntax : ชนดของตวแปร ชอตวแปร = คำเรมตน;

ตวอยำง: unsigned int count = 10,000; float y = 99.9999;

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

52

กำรประกำศตวแปรแบบคำคงท (Constant) กำรประกำศตวแปรแบบคำคงท เปนกำรประกำศตวแปรพรอมกบก ำหนดคำใหตวนนเลย ซงคำในตวแปรจะไมสำมำรถแกไขหรอเปลยนแปลงไดภำยหลง กำรประกำศตวแปรคำคงทจะประกำศไวตรงสวนหวของโปรแกรม

#include <ADuC7024.H> static const float pi =3.14; static const int y = 5;

5.3.6 ตวแปรแบบอำรเรย ตวแปรแบบอำรเรย (Array) คอ ตวแปรทใชเกบขอมลแบบชด หรอกลมขอมลทเปน

ชนดเดยวกน โดยมโครงสรำงดงน

ภาพท 5.38 อำรเรย 1 มต

unsigned char a[2][5];

ภาพท 5.39 อำรเรย 2 มต

5.3.7 เครองหมำยตวด ำเนนกำร เครองหมำยและตวด ำเนนกำรภำษำซ ทเรำรจกและจ ำเปนตองใชงำนอยเปนประจ ำ

สำมำรถแบงออกเปน 5 แบบคอ

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

53

ตารางท 5.2 เครองหมำยตวด ำเนนกำรทำงคณตศำสตร

เครองหมาย การด าเนนการ ตวอยาง + บวก a = b + c;

- ลบ a = b – c;

* คณ a = b * c;

/ หำร a = b / c;

% หำรเอำเศษ a = b % c;

ตารางท 5.3 เครองหมำยตวด ำเนนกำรทำงดำนกำรเปรยบเทยบ

เครองหมาย การด าเนนการ ตวอยาง > มากกวา a>b (ถำ a มำกกวำ b ผลลพทธ = จรง ) < นอยกวา a<b (ถำ a นอยกวำ b ผลลพทธ = จรง ) >= มากกวาหรอเทากบ a>=b (ถำ a มำกกวำหรอเทำกบ b ผลลพทธ = จรง ) <= นอยกวาหรอเทากบ a<=b (ถำ a นอยกวำหรอเทำกบ b ผลลพทธ = จรง ) == เทากบ a == b (ถำ a เทำกบ b ผลลพทธ = จรง ) && AND a && b (ผลลพธจะเปนจรงกตอเมอ a และ b เปนจรง) || OR a || b(ผลลพธจะเปนจรงกตอเมอ a หรอ b เปนจรง) ! NOT !a (เมอ a เปนจรง !a ผลลพธจะเปนเทจ)

ตารางท 5.4 เครองหมำยตวด ำเนนกำรระดบบต

เครองหมาย การด าเนนการ ตวอยาง

& AND a = b & 0xF8; (1111 1000) ถำ b = 1010 1010 ;a เทำกบ 1010 1000

| OR a= b | 0xF8; (1111 1000) ถำ b = 1010 1010 ;a เทำกบ 1111 1010

^ XOR a= b ^ 0xF8; (1111 1000) ถำ b = 1010 1010 ;a เทำกบ 0101 0010

~ Complement a=~b (1111 1000) ; a เทำกบ 0000 0111

ตารางท 5.5 เครองหมำยตวด ำเนนกำรเพมคำและลดคำ

เครองหมาย การด าเนนการ ตวอยาง

++ เพมคา a = i++; น ำคำตว i ไปเกบทตวแปร a แลวบวกคำ i เพมขนหนงคำ a= ++i; บวกคำ i เพมขนหนงคำ แลวน ำคำ i ไปเกบทตวแปร a

-- ลดคา a = i--; น ำคำตว i ไปเกบทตวแปร a แลวลบคำ i ลงขนหนงคำ a = --i; ลบคำ i ลงหนงคำ แลวน ำคำ i ไปเกบทตวแปร a

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

54

ตารางท 5.6 เครองหมำยตวด ำเนนกำรเลอนบต (ซำย, ขวำ)

เครองหมาย การด าเนนการ ตวอยาง

<< เลอนบตไปทางซาย

a << 3 เลอนบตขอมลในตวแปร a ไปทำงซำย 3 บต a (0000 0001) ผลลพธ a = 0000 1000

>> เลอนบตไปทางขวา

a >> b เลอนบตขอมลในตวแปร a ไปทำงซำย b บต a (0011 0000), b = 4 ; ผลลพธ a = 0000 0011

ตารางท 5.7 ตวก ำหนดชนดขอมลของภำษำซ

ตวก าหนดชนดขอมล ความหมายของตวก าหนดชนดขอมล %c แสดงขอมลในรปตวอกษร %d แสดงขอมลในรปตวเลขจ ำนวนเตม %e แสดงขอมลในรปเอกซโพเนลเชยล %f แสดงขอมลในรปตวเลขทศนยม %o แสดงขอมลในรปตวเลขฐำน 8 %x แสดงขอมลในรปตวเลขฐำน 16 %u แสดงขอมลในรปของจ ำนวนเตมบวก %s แสดงขอมลในรปของขอควำม (String) %p แสดงขอมลในรปของทอยของตวแปร (Address) %% แสดงเครองหมำย %

กำรก ำหนดชนดของตวแปร ควรก ำหนดใหสอดคลองกบกำรใชงำน เชน ถำมกำร

ค ำนวณเปนจดทศนยม ควรก ำหนดชนดของตวแปรเปนแบบ float หรอกำรก ำหนดตวแปรเพอใชในกำรวนรอบทไมเกน 127 รอบ ควรก ำหนดตวแปรเปน char เปนตน เพอลดขนำดของโปรแกรมใหเลกลงและท ำใหกำรประมวลผลเรวขน

5.3.8 รปแบบกำรเขยนค ำสง

• ค ำสงตองเขยนดวยตวพมพเลก ในภำษำ C ถอวำตวพมพเลกและตวพมพใหญตำงกน

for( ), while( ), if..else.., unsigned int count; • เมอจบค ำสงจะมตองลงทำยดวยเครอง “ ; “ และสำมำรถเขยนหลำยค ำสงใน

บรรทดเดยวกนได unsigned char i, j; i = 0; j = 0; j++; • หลงฟงกชนไมตองลงทำยดวยเครองหมำย “ ; ”

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

55

void delay (unsigned long count) { while (count > 0) { count--; } } • ในหนงโปรแกรมจะมกฟงกชนกไดแตจะตองมฟงกชนทชอ main() เสมอ void main(void) {

} • กำรตงชอตวแปรใดๆ ในโปรแกรม : เปนกำรก ำหนดชอตำงๆ เชน ชอคำคงท ชอ

โปรแกรม ชอฟงกชน ชอของประเภทขอมล ฯลฯ เพอน ำไปใชในโปรแกรม ซงเปนชอทผเขยนโปรแกรมก ำหนดขนมำ โดยกำรก ำหนดชอมกฎเกณฑดงตอไปน

- ประกอบดวยตวอกษรตงแต A ถง Z หรอตวเลขตงแต 0 ถง 9 ทไมมสญลกษณพเศษอนๆ อย

- ขนตนดวยตวอกษรภำษำองกฤษ (หำมเปนตวเลข) และตวถดไปอำจเปนตวเลข ตวอกษร หรอเครองหมำย Underscore ( _ ) กได

- ตวอกษรตวใหญกบตวเลกจะถอวำเปนคนละตวกน i, j, count, Count, count1, count2, x_y, _irq 29x, “xy”, +x, y-, 12345 • กำรแทรกค ำบรรยำย (Comment) : กำรเขยนค ำบรรยำยแทรกไวภำยในโปรแกรม

จะชวยเพมควำมเขำใจของตวเรำ หรอเพอใหคนอนมำอำนโปรแกรมไดเขำใจสงทเรำเขยนดวย ค ำบรรยำยแทรก โดยใชเครองหมำย /* ขอควำมทตองกำร */

// ขอควำมแทรกทงบรรทด

/* function delay time calling by main function */ void delay(unsigned int count) { while (count>0) count--; // Counter }

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

56

5.3.8.1 ค ำสงเงอนไขและกำรท ำซ ำ 1) ค ำสงเงอนไข (Condition)

กำรเขยนโปรแกรมภำษำ c ในบำงกรณจ ำเปนตองให ARM7 ตดสนใจด ำเนนกำรอยำงใดหนง โดยกำรก ำหนดเปนเงอนไข (Condition) เชน ถำเงอนไขเปน “จรง” ให ARM7 ด ำเนนกำรตำมชดค ำสง A แตถำเปนเงอนไขเปน “เทจ” ให ARM7 ด ำเนนกำรตำมชดค ำสง B เปนตน ค ำสงก ำหนดเงอนไขไดแก ค ำสง if, if - else, if – else – if และ Switch-Case

ตวอยาง ค าสง if

ตวอยาง ค าสง if-else

if (เงอนไข) { ค าสง }

if (เงอนไข) { ค าสง } else { ค าสง } ค าสง }

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

57

ตวอยาง ค าสง if-else-if

ตวอยาง ค าสง Switch – Case

if (เงอนไข) { ค าสง } else if (เงอนไข) { ค าสง } else { ค าสง }

switch (เงอนไข) { case 1 : ค าสง; break; case 2 : ค าสง; break; case n : ค าสง; break; }

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

58

2) กำรท ำซ ำ (Loop) กำรท ำซ ำหรอกำรท ำ Loop เปนกำรสงให ARM7 ท ำชดค ำสงเดมซ ำๆจนครบตำมจ ำนวนรอบทก ำหนด หรอ ตำมเงอนไขทก ำหนด ซงค ำสงกำรท ำซ ำ ไดแก for, while และ do – while

ตวอยำง ค าสง for ค ำสง for เปนกำรท ำซ ำทผเขยนโปรแกรมสำมำรถก ำหนดจ ำนวนครงใหกระท ำค ำสงได

โดยกำรกำรก ำหนดเรมตนใหแกตวแปร Counter และจ ำนวนรอบทตองกำรท ำซ ำ เมอกระท ำซ ำค ำสงใน {…} จนครบตำมจ ำนวนรอบกจะไปท ำค ำสงหลงเครองหมำย } (ออกจำก Loop)

ค าสง while

ค ำสง while เปนกำรท ำซ ำโดยกำรตรวจสอบเงอนไขกอน ถำเงอนเปนจรงจะกระท ำซ ำค ำสงทอยใน { .. } และหำกเงอนไขเปนเทจจะกระท ำค ำสงหลง }.. (หลดออกจำก Loop)

ค าสง do - while

ค ำสง do - while เปนกำรท ำซ ำโดยจะกระท ำซ ำค ำสงทอยใน { .. } กอนแลวตรวจสอบเงอนไขทหลง จนกระทงเงอนไขเปนเทจจะกระท ำค ำสงหลง } (หลดจำก Loop)

unsigned int i; for (i=0;i<100;i++) { ค าสง } ค าสง

unsigned int i; i = 0; While (i < 100) { ค าสง i++; } ค าสง

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

59

5.3.8.2 Standard Function และ User define Function Standard Function เปนฟงกชนมำตรฐำนทไมโครคอนโทรเลอร

ARM7 ไดเตรยมไวใหผใชงำนสำมำรถเรยกใชงำนได ซงฟงกชนมำตรำฐำนของไมโครคอนโทรเลอร ARM7 (ADuC7024) เชน <stdio.h>, printf(), scanf(), clear(), getchar() เปนตน สวน User define Function เปนฟงกชนทนอกเหนอจำก Standard Function ทไมโครคอนโทรเลอร ARM7 ใหมำโดยผเขยนโปรแกรมสรำงขนมำใชงำนเองเพอตอบสนองควำมตองกำรในกำรเขยนโปรแกรม ตวอยำงเชน

void show_menu(void) { printf("******** Main Menu *********\n"); printf("1. Test ADC 12Bit 10Ch\n"); printf("2. Test DAC 12Bit 2Ch\n"); printf("****************************\n"); printf("\n"); printf( "Select Choice(1...4)......"); } void main(void) { show_menu(); }

unsigned int i; i = 0; do { ค าสง i++; } while (i<100); ค าสง

i < 100

i= 0

i++;

10.144

57/KM

ITL.re

s.2012

.22

เมอ 25

/01/25

65 01:

27:12

บทท 6 การออกแบบระบบควบคมพไอดสาหรบกระบวนการระดบน า 4 ถง

จากอดตจนถงปจจบนเปนทนาสงเกตไดวา มากกวาครงหนงของตวควบคมทใชอยในอตสาหกรรม เปนตวควบคมแบบพไอดแบบดงเดม หรอแบบดดแปลง ดวยเหตผลทวา ตวควบคมแบบพไอดนน มพฤตกรรมทผใชสามารถเขาใจไดและมวธการหาคาพารามเตอรของตวควบคมทหลากหลายวธ สะดวกในการใชงานและดดแปลงไปใชเชน ตวควบคมแบบ ไอ-พด หรอตวควบคมแบบสององศาอสระ แมในกรณทไมสามารถท าการออกแบบระบบควบคมโดยการวเคราะหโมเดลของกระบวนการ ตวควบคมแบบพไอดกยงสามารถใชงานไดด เนอหาในบทนเราจะกลาวถง กรยาการควบคมแบบพไอด การออกแบบระบบควบคมแบบพไอดดวยเทคนคทางเดนราก และการออกแบบตวควบคมดคปปลงส าหรบกระบวนการแบบหลายอนพตหลายเอาตพต เพอใชเปนแนวทางในออกแบบระบบควบคมพไอดส าหรบกระบวนการระดบน า 4 ถง ใหมผลตอบสนองของระบบมคณสมบตตามทตองการ

6.1 การควบคมแบบพไอด เปนการรวมกนของกรยาควบคมทงแบบ P, I, D ดงสมการ

tp

p p di

K de tu t K e t e t dt K T

T dt 0

(6.1)

แสดงการหา transfer function ของระบบควบคมดงน

p d

i

U sK T s

E s T s

11 (6.2)

โดยท pK เปนคาอตราขยายของ P

dT derivative time

iT เรยกวา integral time ตงแต dynamic และ static characteristics ของตวตรวจวดมผลกระทบตอการชบอกของคา

จรงของการเปลยนไปของเอาตพต ตวทกระท าการวดเปนบทบาทส าคญในการแสดงผลตดสนทงหมดของระบบการควบคม

โดยทวไปตวตรวจวดหาไดจากคา transfer function ของ feed back path ถาคาคงทเวลาของตวตรวจวดเปนการเปรยบเทยบทสามารถมองขามไดของคาคงทคาเวลาอนของระบบการควบคม กบ transfer function ของตวตรวจวดเปลยนแปลงมาเปนคาคงท