albert giban papua bisa karena surga kecil jatuh ke bumi

-

Upload

albert-giban -

Category

Education

-

view

35 -

download

0

Transcript of albert giban papua bisa karena surga kecil jatuh ke bumi

Transkripsi

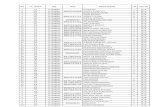

1 JENIS-JENIS REGISTER (Tugas Sistem Digital) Oleh: EKO SARIYANTO 0917041026 SITI KHOLIFAH 1017041042 JURUSAN FISIKA FAKULTAS MATEMATIKA DAN ILMU PENGETAHUAN ALAM UNIVERSITAS LAMPUNG 2013

2 Register adalah kumpulan elemen-elemen memori yang bekerja bersama sebagai satu unit. Register dapat dibentuk dari rangkaian logika sekuensial yang dibentuk dari flip-flop. Berdasarkan fungsinya register terdiri atas, register buffer dan register geser. Register Buffer Gambar 1 Rangkaian buffer 4 D-FF yang tersambung dalam sebuah rangkaian serial in, serial out shift register. Register buffer berfungsi untuk menyimpan kata digital. Setiap datang pulsa clock, data dari input D dari masing-masing FF akan di transfer kepada Q output. Pada awalnya, isi dari register diset 0 dengan mengirimkan clock pada clear. Jika 1 merupakan input dari FF yang pertama, maka pada pulsa berikutnya 1 akan di trasnfer ke output FF1 dan sekaligus menjadi input FF2. Gambar 2 Aliran data pada register buffer

3 a. Register Buffer terkendali Gambar 3 Register Buffer terkendali Register Buffer Terkendali adalah register buffer yang ditambah dengan beberapa gerbang logika dasar AND, OR, dan NOT. Gambar rangkaian menunjukkan sebuah Register buffer terkendali dengan CLR aktif tinggi. Apabila CLR = 1, maka akan terjadi reset pada flip-flop dan data yang tersimpan (Q) menjadi 0000. dan ketika CLR = 0, register siap beroperasi kembali. Sinyal kendali LOAD adalah input kendali yang menentukan operasi rangkaian.ketika LOAD = 0, semua input data tidak diizinkan masuk, artinya flip-flop mengisolasi input data atau menahan semua data yang ada di dalamnya. Dengan kata lain, register tidak berubah selama LOAD = 0. Ketika LOAD = 1, semua input data akan diterima oleh register. Ketika LOAD kembali = 0, maka input data yang diterima register tadi akan tersimpan dengan aman tanpa gangguan perubahan input. Gambar 4. D Flip-Flop

4 Tabel 1. Table kebebaran D flip-flop Input Output D Q n+1 0 0 1 1 Register geser a. Register geser serial in serial out (SISO) Dasar register geser empat-bit dapat dirangkai dengan menggunakan empat D flipflop, seperti yang diperlihatkan di bawah. Selama pulsa clock, satu bit ditransmisikan dari kiri ke kanan. Menerima suatu kata data menjadi 1001. Gambar 3. Rangkaian register geser SISO Data di angkut pada register, saat garis kontrol tinggi (HIGH dengan kata lain WRITE).

Data dapat di geser keluar dari register saat garis kontrol rendah ( LOW dengan kata lain READ). Aliran data pada register SISO ini diibaratkan Pada Gambar 4. Data in Data out Gambar 4 Ilustrasi data masuk dan keluar register SISO

5 b. Register geser serial in - parallel out (SIPO) Dari jenis register ini, bit-bit data dimasukan secara serial sama artinya sama dengan SISO. Perbedaanya adalah cara dimana bit-bit data dipindahkan dari register. Sekali data disimpan, setiap bit muncul pada masing-masing baris keluarannya, dan semua bit-bitnya mampu secara simultan. Sebuah susunan empat-bit register SIPO diperlihatkan di bawah ini. Gambar 5. Register SIPO dalam susunan 4 bit Pada jenis SIPO ini, hasil keluaran dari register geser dapat diilustrasikan seperti pada Gambar 6. Data in Data out Gambar 6. Aliran data keluara dari SIPO c. Register geser parallel in serial out (PISO) Gambar 7. Register PISO

6 D0, D1, D2 dan D3 adalah paralel input, dimana D0 adalah most significant bit (MSB) dan D3 adalah least significant bit (LSB). Untuk menulis data masuk, baris pengontrolan mode diambil pada rendah dan data di-clock masuk. Data dapat digeser saat baris kontrol mode tinggi bersamaan SHIFT aktif tinggi. Register menampilkan operasi geser kanan pada aplikasi satu pulsa clock. Ilustrasi keluaran dari register PISO terlihat pada Gambar 8. Data in Gambar 8. Aliran data pada PISO Data out d. Register geser parallel In - parallel out (PIPO) Untuk register Parallel In Parallel Out, semua bit-bit data muncuk pada keluaran-keluaran paralel secara mendadak mengikuti masukan yang simultan dari bit-bit data. Gambar 9. Register PIPO Masukan-masukan D dan keluaran Q adalah paralel. Sekali register di-clock, semua data di D input muncul pada keluaran Q yang berhubungan secara simultan.pada register geser ini, keluarannya diilustrasikan oleh Gambar 10.

7 Data in Data out e. Bidirectional Shift Registers Suatu register dua arah dalam data dijadikan geser kanan atau kiri. Bidirectional Shift Registers menggunakan D flip-flop ditunjukan dibawah. Gambar 7. Bidirectional Shift Registers Dalam hal ini kumpulan gerbang NAND dikonfigurasi sebagai gerbang OR untuk memilih data masukan dari dua keadaan stabil yang berdekatan kanan atau kiri (the right or left adjacent bistables), seperti yang dipilih dengan LEFT/RIGHT baris pengontrolan. Contoh soal 1. Gambarkan bentuk rangkaian register buffer 4D. 2. Bagaimanakah aliran data pada register buffer data masukkan 0111 untuk setiap kali clock? Gambarkan aliran data untuk setiap clock.

8 3. Pada registr buffer menggunakan rangkaian D flip-flop, bagaimanakah keluaran dari D flip-flop bila input hight dan low. Gambarkan dalam tabel kebenaran. 4. Pada jenis register geser, apa yang anda ketahui tentang register geser SISO? 5. Gambarkan rangkaian register geser SISO 4 bit. 6. Gambarkan ilustrasi aliran data pada register geser SISO. 7. Pada jenis register geser, apa yang anda ketahui tentang register geser SIPO? 8. Gambarkan rangkaian register geser SIPO 4 bit. 9. Gambarkan ilustrasi aliran data pada register geser SIPO. 10. Pada jenis register geser, apa yang anda ketahui tentang register geser PISO? 11. Gambarkan rangkaian register geser PISO 4 bit. 12. Gambarkan ilustrasi aliran data pada register geser PISO. 13. Pada jenis register geser, apa yang anda ketahui tentang register geser PIPO? 14. Gambarkan rangkaian register geser PIPO 4 bit. 15. Gambarkan ilustrasi aliran data pada register geser PIPO. 16. Bagaimana prisip kerja dari register Bidirectional Shift? 17. Gambarkan rangkaian dari register Bidirectional Shift.