Test pattere06199995

-

Upload

independent -

Category

Documents

-

view

0 -

download

0

Transcript of Test pattere06199995

614 IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, VOL. 21, NO. 4, APRIL 2013

Test Patterns of Multiple SIC Vectors: Theoryand Application in BIST Schemes

Feng Liang, Luwen Zhang, Shaochong Lei, Guohe Zhang, Kaile Gao, and Bin Liang

Abstract— This paper proposes a novel test pattern generator(TPG) for built-in self-test. Our method generates multiple single-input change (MSIC) vectors in a pattern, i.e., each vector appliedto a scan chain is an SIC vector. A reconfigurable Johnsoncounter and a scalable SIC counter are developed to generatea class of minimum transition sequences. The proposed TPG isflexible to both the test-per-clock and the test-per-scan schemes.A theory is also developed to represent and analyze the sequencesand to extract a class of MSIC sequences. Analysis results showthat the produced MSIC sequences have the favorable featuresof uniform distribution and low input transition density. Theperformances of the designed TPGs and the circuits undertest with 45 nm are evaluated. Simulation results with ISCASbenchmarks demonstrate that MSIC can save test power andimpose no more than 7.5% overhead for a scan design. It alsoachieves the target fault coverage without increasing the testlength.

Index Terms— Built-in self-test (BIST), low power, single-inputchange (SIC), test pattern generator (TPG).

I. INTRODUCTION

BUILT-IN SELF-TEST (BIST) techniques can effectivelyreduce the difficulty and complexity of VLSI testing, by

introducing on-chip test hardware into the circuit-under-test(CUT). In conventional BIST architectures, the linear feedbackshift register (LFSR) is commonly used in the test patterngenerators (TPGs) and output response analyzers. A majordrawback of these architectures is that the pseudorandompatterns generated by the LFSR lead to significantly highswitching activities in the CUT [1], which can cause excessivepower dissipation. They can also damage the circuit and reduceproduct yield and lifetime [2], [3]. In addition, the LFSRusually needs to generate very long pseudorandom sequencesin order to achieve the target fault coverage in nanometertechnology.

A. Prior Work

Several advanced BIST techniques have been studied andapplied. The first class is the LFSR tuning. Girard et al.analyzed the impact of an LFSR’s polynomial and seedselection on the CUT’s switching activity, and proposed amethod to select the LFSR seed for energy reduction [4].

Manuscript received July 18, 2011; revised April 5, 2012; accepted April 12,2012. Date of publication May 14, 2012; date of current version March 18,2013. This work was supported in part by the Fundamental Research Fundsfor the Central Universities under Grant xjj20100053 and the National NaturalScience Foundation of China under Grant 61006033.

The authors are with the School of Electronic and InformationEngineering, Xi’an Jiaotong University, Xi’an 710049, China (e-mail:[email protected]).

Digital Object Identifier 10.1109/TVLSI.2012.2195689

The second class is low-power TPGs. One approach isto design low-transition TPGs. Wang and Gupta used twoLFSRs of different speeds to control those inputs that haveelevated transition densities [5]. Corno et al. provided a low-power TPG based on the cellular automata to reduce the testpower in combinational circuits [6]. Another approach focuseson modifying LFSRs. The scheme in [7] reduces the powerin the CUT in general and clock tree in particular. In [8],a low-power BIST for data path architecture is proposed,which is circuit dependent. However, this dependency impliesthat nondetecting subsequences must be determined for eachcircuit test sequence. Bonhomme et al. [9] used a clock gatingtechnique where two nonoverlapping clocks control the oddand even scan cells of the scan chain so that the shift powerdissipation is reduced by a factor of two. The ring generator[10] can generate a single-input change (SIC) sequence whichcan effectively reduce test power. The third approach aimsto reduce the dynamic power dissipation during scan shiftthrough gating of the outputs of a portion of the scan cells.Bhunia et al. [11] inserted blocking logic into the stimuluspath of the scan flip-flops to prevent the propagation of thescan ripple effect to logic gates. The need for transistorsinsertion, however, makes it difficult to use with standardcell libraries that do not have power-gated cells. In [12], theefficient selection of the most suitable subset of scan cells forgating along with their gating values is studied.

The third class makes use of the prevention of pseudoran-dom patterns that do not have new fault detecting abilities[13]–[15]. These architectures apply the minimum number oftest vectors required to attain the target fault coverage andtherefore reduce the power. However, these methods havehigh area overhead, need to be customized for the CUT, andstart with a specific seed. Gerstendorfer et al. also proposedto filter out nondetecting patterns using gate-based blockinglogics [16], which, however, add significant delay in the signalpropagation path from the scan flip-flop to logic.

Several low-power approaches have also been proposed forscan-based BIST. The architecture in [17] modifies scan-pathstructures, and lets the CUT inputs remain unchanged duringa shift operation. Using multiple scan chains with many scan-enable (SE) inputs to activate one scan chain at a time, theTPG proposed in [18] can reduce average power consumptionduring scan-based tests and the peak power in the CUT.In [19], a pseudorandom BIST scheme was proposed toreduce switching activities in scan chains. Other approachesinclude LT-LFSR [20], a low-transition random TPG [21],and the weighted LFSR [22]. The TPG in [20] can reducethe transitions in the scan inputs by assigning the same

1063-8210/$31.00 © 2012 IEEE

LIANG et al.: TEST PATTERNS OF MULTIPLE SIC VECTORS 615

value to most neighboring bits in the scan chain. In [21],power reduction is achieved by increasing the correlationbetween consecutive test patterns. The weighted LFSR in [22]decreases energy consumption and increases fault coverage byadding weights to tune the pseudorandom vectors for variousprobabilities.

B. Contribution and Paper Organization

This paper presents the theory and application of a classof minimum transition sequences. The proposed methodgenerates SIC sequences, and converts them to low transi-tion sequences for each scan chain. This can decrease theswitching activity in scan cells during scan-in shifting. Theadvantages of the proposed sequence can be summarized asfollows.

1) Minimum transitions: In the proposed pattern, eachgenerated vector applied to each scan chain is an SICvector, which can minimize the input transition andreduce test power.

2) Uniqueness of patterns: The proposed sequence does notcontain any repeated patterns, and the number of distinctpatterns in a sequence can meet the requirement of thetarget fault coverage for the CUT.

3) Uniform distribution of patterns: The conventional algo-rithms of modifying the test vectors generated by theLFSR use extra hardware to get more correlated testvectors with a low number of transitions. However, theymay reduce the randomness in the patterns, which mayresult in lower fault coverage and higher test time [23].It is proved in this paper that our multiple SIC (MSIC)sequence is nearly uniformly distributed.

4) Low hardware overhead consumed by extra TPGs: Thelinear relations are selected with consecutive vectors orwithin a pattern, which has the benefit of generatinga sequence with a sequential decompressor. Hence, theproposed TPG can be easily implemented by hardware.

The rest of this paper is organized as follows. In Section II,the proposed MSIC-TPG scheme is presented. The principleof the new MSIC sequences is described in Section III.In Section IV, the properties of the MSIC sequences areanalyzed. In Section V, experimental methods and results ontest power, fault coverage, and area overhead are providedto demonstrate the performance of the propsoed MSIC-TPGs.Conclusions are given in Section VI.

II. PROPOSED MSIC-TPG SCHEME

This section develops a TPG scheme that can convert anSIC vector to unique low transition vectors for multiple scanchains. First, the SIC vector is decompressed to its multiplecodewords. Meanwhile, the generated codewords will bit-XOR

with a same seed vector in turn. Hence, a test pattern withsimilar test vectors will be applied to all scan chains. Theproposed MSIC-TPG consists of an SIC generator, a seedgenerator, an XOR gate network, and a clock and control block.

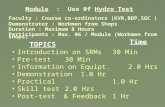

Fig. 1. (a) Symbolic simulation of an MSIC pattern for scan chains.(b) Symbolic representation of an MSIC pattern.

A. Test Pattern Generation Method

Assume there are m primary inputs (PIs) and M scanchains in a full scan design, and each scan chain has lscan cells. Fig. 1(a) shows the symbolic simulation for onegenerated pattern. The vector generated by an m-bit LFSRwith the primitive polynomial can be expressed as S(t) =S0(t)S1(t)S2(t), . . . , Sm−1(t) (hereinafter referred to as theseed), and the vector generated by an l-bit Johnson countercan be expressed as J (t) = J0(t)J1(t)J2(t), . . . , Jl−1(t).

In the first clock cycle, J = J0 J1 J2, . . . , Jl−1 willbit-XOR with S = S0S1S2, . . . , SM−1, and the resultsX1 Xl+1 X2l+1, . . . , X(M−1)l+1 will be shifted into Mscan chains, respectively. In the second clock cycle,J = J0 J1 J2, . . . , Jl−1 will be circularly shifted as J =Jl−1 J0 J1, . . . , Jl−2, which will also bit-XOR withthe seed S = S0S1 S2, . . . , SM−1. The resultingX2 Xl+2 X2l+2, . . . , X(M−1)l+2 will be shifted into Mscan chains, respectively. After l clocks, each scan chain willbe fully loaded with a unique Johnson codeword, and seedS0S1 S2, . . . , Sm−1 will be applied to m PIs.

Since the circular Johnson counter can generate l uniqueJohnson codewords through circular shifting a Johnson vector,the circular Johnson counter and XOR gates in Fig. 1 actuallyconstitute a linear sequential decompressor.

B. Reconfigurable Johnson Counter

According to the different scenarios of scan length, thispaper develops two kinds of SIC generators to generateJohnson vectors and Johnson codewords, i.e., the reconfig-urable Johnson counter and the scalable SIC counter.

616 IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, VOL. 21, NO. 4, APRIL 2013

Fig. 2. SIC generators. (a) Reconfigurable Johnson counter. (b) Scalable SICcounter. (c) Waveforms of the scalable SIC counter.

For a short scan length, we develop a reconfigurableJohnson counter to generate an SIC sequence in time domain.As shown in Fig. 2(a), it can operate in three modes.

1) Initialization: When RJ_Mode is set to 1 and Init isset to logic 0, the reconfigurable Johnson counter willbe initialized to all zero states by clocking CLK2 morethan l times.

2) Circular shift register mode: When RJ_Mode and Initare set to logic 1, each stage of the Johnson counterwill output a Johnson codeword by clocking CLK2 ltimes.

3) Normal mode: When RJ_Mode is set to logic 0, thereconfigurable Johnson counter will generate 2l uniqueSIC vectors by clocking CLK2 2l times.

C. Scalable SIC Counter

When the maximal scan chain length l is much larger thanthe scan chain number M , we develop an SIC counter namedthe “scalable SIC counter.” As shown in Fig. 2(b), it containsa k-bit adder clocked by the rising SE signal, a k-bit subtractorclocked by test clock CLK2, an M-bit shift register clockedby test clock CLK2, and k multiplexers. The value of k is theinteger of log2(l − M). The waveforms of the scalable SICcounter are shown in Fig. 2(c). The k-bit adder is clocked bythe falling SE signal, and generates a new count that is thenumber of 1s (0s) to fill into the shift register. As shown inFig. 2(b), it can operate in three modes.

1) If SE = 0, the count from the adder is stored to thek-bit subtractor. During SE = 1, the contents of thek-bit subtractor will be decreased from the stored countto all zeros gradually.

2) If SE = 1 and the contents of the k-bit subtractor arenot all zeros, M-Johnson will be kept at logic 1 (0).

3) Otherwise, it will be kept at logic 0 (1). Thus, the needed1s (0s) will be shifted into the M-bit shift register byclocking CLK2 l times, and unique Johnson codewordswill be applied into different scan chains.

For example, after full-scan design, ISCAS’89 s13207has 10 scan chains whose maximum scan length is 64. Toimplement a scalable SIC counter as shown in Fig. 2(b), itonly needs 6 D-type flip-flops (DFFs) for the adder, 6 DFFsfor the subtractor, 10 DFFs for a 10-bit shift register for10 scan chains, 6 multiplexers, and additional 19 combina-tional logic gates. The equivalent gates are 204 in total. Fora 64-bit Johnson counter, it needs 64 DFFs, which are about428 equivalent gates. The overhead of a MSIC-TPG can thusbe effectively decreased by using the scalable SIC counter.

Generally, the gate overhead of a MSIC-TPG can beestimated by the number of DFFs (NDFF) used

NDFF = m + M + 2log2l = (m + M)

(1 + 2log2l

m + M

)(1)

where m, M, and l are the seed number, scan chain number,and the maximum scan length, respectively. If l is doubled,the number of DFFs is only increased by 2/(m + M) times.If 2i−1 < l < 2i (i is a natural number), the number of DFFsdoes not vary with the CUTs’ sizes. For example, as will beshown in Table II, for ISCAS’89 benchmarks, when the seednumber increases from 20 to 38 and the maximum scan lengthincreases from 54 to 87, their area overheads change only from397.40 to 488.29 μm2.

D. MSIC-TPGs for Test-per-Clock Schemes

The MSIC-TPG for test-per-clock schemes is illustrated inFig. 3(a). The CUT’s PIs X1 − Xmn are arranged as an n × mSRAM-like grid structure. Each grid has a two-input XOR gatewhose inputs are tapped from a seed output and an outputof the Johnson counter. The outputs of the XOR gates areapplied to the CUT’s PIs. A seed generator is an m-stageconventional LFSR, and operates at low frequency CLK1. Thetest procedure is as follows.

1) The seed generator generates a new seed by clockingCLK1 one time.

2) The Johnson counter generates a new vector by clockingCLK2 one time.

3) Repeat 2 until 2l Johnson vectors are generated.4) Repeat 1–3 until the expected fault coverage or test

length is achieved.

E. MSIC-TPGs for Test-per-Scan Schemes

The MSIC-TPG for test-per-scan schemes is illustrated inFig. 3(b). The stage of the SIC generator is the same as themaximum scan length, and the width of a seed generator is

LIANG et al.: TEST PATTERNS OF MULTIPLE SIC VECTORS 617

Fig. 3. MSIC-TPGs for (a) test-per-clock and (b) test-per-scan schemes.

not smaller than the scan chain number. The inputs of theXOR gates come from the seed generator and the SIC counter,and their outputs are applied to M scan chains, respectively.The outputs of the seed generator and XOR gates are applied tothe CUT’s PIs, respectively. The test procedure is as follows.

1) The seed circuit generates a new seed by clocking CLK1one time.

2) RJ_Mode is set to “0”. The reconfigurable Johnsoncounter will operate in the Johnson counter mode andgenerate a Johnson vector by clocking CLK2 one time.

3) After a new Johnson vector is generated, RJ_Mode andInit are set to 1. The reconfigurable Johnson counteroperates as a circular shift register, and generates lcodewords by clocking CLK2 l times. Then, a captureoperation is inserted.

4) Repeat 2–3 until 2l Johnson vectors are generated.5) Repeat 1–4 until the expected fault coverage or test

length is achieved.

III. PRINCIPLE OF MSIC SEQUENCES

The main objective of the proposed algorithm is to reducethe switching activity. In order to reduce the hardware over-head, the linear relations are selected with consecutive vectorsor within a pattern, which can generate a sequence with a

sequential decompressor, facilitating hardware implementa-tion. Another requirement is that the MSIC sequence shouldnot contain any repeated test patterns, because repeated pat-terns could prolong the test time and reduce test efficiency [5].Finally, uniformly distributed patterns are desired to reduce thetest length (number of patterns required to achieve a targetfault coverage) [21]. This section aims to extract a class oftest sequences that meets these requirements.

A. Algebraic Model of MSIC Sequence

Assume there are m PIs and M scan chains in a full scandesign, and each scan chain has l scan cells. At time t, a testvector applied to the ith scan chain can be expressed as

Ci (t, x) =⎛⎝ l∑

j=1

Mi (t, j)x j−1

⎞⎠ x (i−1)l+m (2)

where i∈(1, M), and Mi (t, j) is the content of the jthscan cell in the ith scan chain. Assume an m-bit LFSRwith the primitive polynomial generates a vector S(t) =S0(t)S1(t)S2(t), . . . , Sm−1(t), and an l-bit Johnson countergenerates a vector J (t) = J0(t)J1(t)J2(t), . . . , Jl−1(t). Thesetwo vectors can be used to construct the vector for the ithscan chain as

Ci (t, x) =⎧⎨⎩

l∑j=1

Si (t)x j−1 + Ji (t, x)

⎫⎬⎭ x (i−1)l+m (3)

where “+” denotes the bit-XOR operation, andJi (t, x) is the tth codeword of the Johnson vectorJ (t) = J0(t)J1(t)J2(t), . . . , Jl−1(t). More precisely

J1(t, x) = J0(t, x)+J1(t, x)x+ · · · +Jl−2(t, x)xl−2

+Jl−1(t, x)xl−1

J2(t, x) = Jl−1(t, x)+J0(t, x)x+ · · · +Jl−3(t, x)xl−2

+Jl−2(t, x)xl−1

...

Jl−1(t, x) = J2(t, x)+J3(t, x)x+ · · · +J0(t, x)xl−2

+J1(t, x)xl−1

Jl(t, x) = J1(t, x)+J2(t, x)x+ · · · +Jl−1(t, x)xl−2

+J0(t, x)xl−1. (4)

As described in Section II-E [Figs. 1 and 3(b)], the seedcircuit generates a new seed by clocking the slow clock CLK1one time. When RJ_Mode is set to “0,” the reconfigurableJohnson counter will operate in the Johnson counter modeand generate a Johnson vector by clocking the normal clockCLK2 one time. After a new Johnson vector is generated,RJ_Mode and Init are set to 1. The reconfigurable Johnsoncounter will then operate as a circular shift register andgenerate l codewords by clocking CLK2 l times. Meanwhile,M of these codewords will be shifted into M scan chains.A capture operation is then inserted. Therefore, the timerequired for a Johnson vector to be applied to the CUT isl normal clock cycles. Since an l-stage Johnson counter cangenerate 2l different Johnson vectors, the period of a Johnson

618 IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, VOL. 21, NO. 4, APRIL 2013

sequence is actually 2l2 normal clock cycles in this paper.Therefore, the constraint equations of S and J are given by

S(t) = S([t/2l2]) J (t + 2l2) = J (t) (5)

where [t/2l2] denotes the integer part of t/2l2.With these considerations, the kth pattern applied to

the combinational part of the CUT, i.e., X (tk, x), can beexpressed as

X (k) = X (tk, x)

=m∑

q=1

Sq−1(tk)xq−1

+M∑

i=1

⎧⎨⎩

l∑j=1

Si (tk)x j−1 + Ji (tk, x)

⎫⎬⎭ x (i−1)l+m (6)

where tk = [t/ l]. A sequence satisfying (3)–(6) is called anMSIC sequence.

Theorem 1: The period of a MSIC sequence is 2l(2m − 1).Proof: The pth pattern applied to the combinational part

of the CUT can be expressed as

X (p) = X (tp, x)

=m∑

q=1

Sq−1(tp)xq−1

+M∑

i=1

⎧⎨⎩

l∑j=1

Si (tp)x j−1 + Ji (tp, x)

⎫⎬⎭ x (i−1)l+m .

The bit-XOR result of the pth pattern and the kth patterncan be expressed as

X (tp, x)+X (tk, x)

=m∑

q=1

(Sq−1(tp) + Sq−1(tk))xq−1

+M∑

i=1

⎧⎨⎩

l∑j=1

(Si (tk) + Si (tp))x j−1

⎫⎬⎭ x (i−1)l+m

+M∑

i=1

{Ji (tp, x) + Ji (tk, x)

}x (i−1)l+m . (7)

If S(tp) �= S(tk), the following expressions are true:m∑

q=1

(Sq−1(tp) + Sq−1(tk))xq−1 �= 0

M∑i=1

⎧⎨⎩

l∑j=1

(Si (tk) + Si (tp))x j−1

⎫⎬⎭ x (i−1)l+m �= 0. (8)

Therefore, (7) is not zero for unique seeds. If S(tp) = S(tk),(7) can be simplified as

X (tp, x)+X (tk, x)=M∑

i=1

{Ji (tp, x) + Ji (tk, x)

}x (i−1)l+m . (9)

From (3), we know that (9) is not zero for unique Johnsonvectors. Combining (8) and (9), we can conclude that (7) iszero for a maximum length LFSR sequence. Since the periodof an l-bit Johnson sequence and an m-bit LFSR sequence are

2l and 2m − 1, respectively, the period of an MSIC sequencedefined in (6) is thus 2l(2m − 1).

The theorem shows that the generated MSIC sequence canbe applied to a CUT as a consecutive sequence. This makes theproposed TPG flexible to different lengths of scan chains. Thetradeoff between the target fault coverage and the overheaddetermines the design process of MSIC-TPGs. In fact, thenumber 2l(2m − 1) is large enough for general CUTs, whichcan achieve the target fault coverage. Hence, the numbersof Johnson counter stages and LFSR stages can be selectedaccording to the demand. Let s and j be the number of LFSRstages and the number of Johnson counter stages, respectively.For test-per-clock schemes, the product of s and j only needsto satisfy the condition s × j ≥ m such that 2 j (2s − 1) canachieve the target fault coverage. For test-per-scan schemes, jusually equals to l, and s is selected as half the number of PIsor a fixed number which is not smaller than the scan chainnumber. The principle of selecting s is to reduce the overheadand achieve the target fault coverage. Experimental results inthis paper will show that the selection of s based on theseprinciples has negligible impact on the test length.

B. Example

Suppose there are four scan chains whose lengths are 8 ina full-scan design. The 8-bit Johnson codewords and 4-bit (ormore bits) seeds can be used to generate an MSIC sequence.A MSIC sequence with seed 01101 is

chain1... chain2

... chain3... chain4

... PIs

X (1) 10000000... 10111111

... 11011111... 00010000

... 01101

X (2) 11000000... 10011111

... 11001111... 00011000

... 01101

X (3) 11100000... 10001111

... 11000111... 00001110

... 01101

X (4) 11110000... 10000111

... 11000011... 00001111

... 01101...

X (15) 00000001... 01111111

... 10111111... 00100000

... 01101

X (16) 00000000... 11111111

... 11111111... 00000000

... 01101.

For (25 − 1) unique seeds, there are 31 such blocks.Therefore, there are 16 × 31 = 496 unique patterns in thisMSIC sequence. Also, the transition between patterns X(t) andX(t+1) is one for every scan chain, and transitions for scanchain 2 to scan in “1001111” are two per clock. Seed “01101”is kept unchanged for patterns X (1) to X (16).

However, if the seed circuit and the Johnson counter areclocked by the same frequency clocks, a sequence based on(3) is as follows:

chain1... chain2

.

.

. chain3... chain4

.

.

. PIs

X (1) 01111011... 11001110

.

.

. 11000111... 11100000

.

.

. 10001 → 11010

X (2) 01011101... 11100111

.

.

. 01100011... 11010000

.

.

. 01101 → 01111

X (3) 00101110... 11110111

.

.

. 10110001... 11101100

.

.

. 00111 → 11101

X (5) 00000111... 01010101

.

.

. 11011000... 11110100

.

.

. 01110 → 00001...

X (32) 01111011... 11001110

.

.

. 11000111... 11100000

.

.

. 10001 → 11010 .

LIANG et al.: TEST PATTERNS OF MULTIPLE SIC VECTORS 619

TABLE I

SWITCHING ACTIVITY DURING SHIFTING

CUT TLWSAavg WSApk WSAavg Red. % WSApk Red. %

MSIC LFSR MSIC LFSR MSIC [3] [20] MSIC [3]

s13207 100 000 2561 4477 5291 8021 43 59 45 34 41s15850 100 000 2403 4531 4352 7126 47 NA 58 39 NAs38417 100 000 2664 11 318 7064 16 304 76 54 56 57 39s35932 200 1031 8580 2543 14 625 88 65 56 83 55s38584 100 000 5268 11 194 3911 15 949 53 49 59 25 51Average NA NA NA NA NA 61 56 54 47 46

It can be seen that X (1) and X (32) are the same. The periodof this sequence is thus 31. The transitions in each scan chainor between neighbor patterns would be higher.

For a combinational circuit, its m PIs can be split into Msegments. Equation (6) can also be used to generate an MSICsequence for it.

The theory and examples above show that there are enoughunique MSIC patterns to achieve the target fault coverage.Also, there are linear relations between these patterns or withina pattern.

IV. PROPERTIES OF MSIC SEQUENCES

A. Switching Activity Reduction

For test-per-clock schemes, M segments of the CUT’sprimary inputs are applied with M unique SIC vectors. Themean input transition density of the CUT is close to 1/ l.For test-per-scan schemes, the CUT’s PIs are kept unchangedduring 2l2 shifting-in clock cycles, and the transitions of aJohnson codeword are not greater than 2. Therefore, the meaninput transition density of the CUT during scan-in operationsis less than 2/ l.

For the five largest ISCAS’89 benchmarks with 20 evenlydistributed scan chains, Table I compares the weighted switch-ing activity (WSA) of scan cells during shifting with the pro-posed MSIC sequence and the conventional LFSR sequence,respectively. The column labeled “TL” lists the number oftest patterns applied to the CUT. The next four columns arethe average WSA (WSAavg) of all shifting operations andthe maximum WSA in a clock cycle (WSApk). The last fivecolumns show the percentages of reductions over LFSR, wherethe performances of the reordering method in [3] and theLT-RTPG method in [20] are also included.

Compared to LFSR sequence, the proposed MSIC sequencecan reduce the average WSA by 43%–88% and peak WSA by25%–83%. Compared with the methods in [3] and [20], theMSIC sequence also shows higher reduction ratios. Therefore,the CUT’ transitions with an MSIC sequence can be effectivelyreduced.

B. Uniform Distribution of MSIC Patterns

If test patterns are not uniformly distributed, there mightbe some inputs that are assigned the same values in mosttest patterns. Hence, faults that can only be detected bypatterns that are not generated may escape, leading to lowfault coverage. Therefore, uniformly distributed test patterns

Fig. 4. (a) Forms of test vectors for scan chain 1. (b) Numbers of 1s in 638scan cells of s13207. (c) Test length-fault coverage curves for c2670.

are desired for most circuits in order to achieve higher faultcoverage [5].

The form of MSIC vectors with seed S0S1 S2, . . . , SM−1 forscan chain 1 is shown in Fig. 4(a). If the test length L is a

620 IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, VOL. 21, NO. 4, APRIL 2013

TABLE II

OVERHEAD OF TPGs

CUT PIsCircuit sizeGates+ DFFs

Width/bitMSIC-TPG LFSR

[21] [24]Area Total power Peak power Area Total power Peak power

SIC Seed μm2 � μW � μW � μm2 � μW � μW � �A �P �A

c2670 233 1193+0 16 15 745.53 157 27.17 70 1019 235 1224.58 258 163.1 423 1060 244 NA 21.87 NAc3540 50 1669+0 5 10 219.68 27 13.91 17 296.7 32 267.46 33 37.68 46 322.5 35 15 19.51 NA

c5315 178 2307+0 13 14 592.32 51 24.05 27 620.5 54 935.76 81 124 112 780.1 67 NA 16.94 NA

c6288 32 2406+0 7 5 169.89 21 12.07 3 196.3 8 172.94 22 24.84 7 222.4 9 NA NA NAc7552 207 3512+0 11 16 601.48 45 24.32 18 819.9 55 1088.04 82 144.3 105 908.1 61 NA NA NA

Average NA NA NA NA 465.78 60.2 20.30 27 590.48 76.8 737.75 95.2 98.78 138.6 658.6 83.2 15 19.44 NA

s13207 62 7951+638 64 32 421.38 6.4 17.5 2.7 351.8 4.8 401.62 6.2 52.81 7.6 454.1 6.2 NA 14 11.3s15850 77 9772+534 54 38 488.29 7.5 18.25 2.8 381.3 5.8 498.48 7.7 65.38 10.1 552.7 8.5 NA NA 8.3

s38417 28 22 179+1636 82 20 397.4 2 25.29 1.2 306.5 1.6 178.18 0.9 23.77 1.1 214.7 1.1 14 NA 3.8s35932 35 12 204+1728 87 20 481.15 2.5 25.51 1.3 326.4 1.6 223.38 1.1 29.67 1.2 268 1.3 NA NA NA

s38584 38 192 53+1426 72 20 482.04 2.3 25.3 1.2 323.4 1.6 246.64 1.2 32.66 1.6 299.5 1.5 12 18.6 4.2

Average NA NA NA NA 454.05 4.14 22.37 1.84 337.88 3.08 309.66 3.4 40.85 4.3 357.8 3.7 13 16.3 6.9

multiple of 2l, all MSIC patterns can be divided into L/2l suchblocks. The probability of 1 (or 0) applied to each scan cellis 0.5. For example, the number of S0 (S0) is l in the firstcolumn.

If the test length L is not a multiple of 2l, the differenceexists only in the last L − integer(L/2l) patterns. So thedifference in the number of 1s and 0s applied to each scancell does not exceed l. Therefore, the probability of 1 (or 0)for a scan cell is

|probabilty(i) − 0.5| ≤ l/L (10)

where i ∈ (0, 1). Fig. 4(b) shows the numbers of 1s in 638scan cells of s13207. The test length is 9974, and the numberof 1s applied to each scan cell is between 4730 and 5194.The probabilities of 1 for all scan cells are between 0.4974and 0.526. For all of the five largest ISCAS’89 benchmarks,simulation results with different initial seeds show that theprobabilities of 1 for all scan cells are between 0.465 and0.535. This shows that an MSIC sequence is nearly uniformlydistributed, and the initial seed state has negligible impact onthe uniform distribution of MSIC pattern.

C. Relationship Between Test Length and Fault Coverage

The test length of conventional LFSR methods is related tothe initial test vector. In other words, the number of patternsto hit the target fault coverage depends on the initial vector inconventional LFSR TPGs [21].

Fig. 4(c) shows the test length-fault coverage relation-ships of c2670 with a conventional LFSR and with a MSICsequence, respectively. The fault model in Fig. 4(c) is stuck at.The width of the seed and the Johnson counter is provided inTable II. For the LFSR sequences, the rates of growth of faultcoverage vary greatly with the TPG’s initial states, as shownby the curves marked with “Best case, LFSR” and “Worstcase, LFSR.” For MSIC sequences, the numbers of patternsto hit the target fault coverage with different initial seeds arenearly the same, as shown by curves marked with “Best case,MSIC” and “Worst case, MSIC.” Also, the rate of growth ofthe fault coverage with the MSIC sequence is very close tothat with the LFSR in the best case. For example, the fault

TABLE III

FAULT COVERAGE RANGE WITH THE SAME TEST LENGTH

CUT TL SFCmin SFCmax δrange

c2670 1988 89.03 92.84 −1.58%∼2.63%c3540 1052 94.36 97.65 −0.74%∼2.71%c5315 1129 99.02 99.62 −0.31%∼0.30%c6288 112 98.45 99.63 −1.00%∼0.18%c7552 1024 94.98 96.46 −0.48%∼1.07%s13207 9942 91.3 93.66 −1.23%∼1.32%s15850 9533 89.16 94.21 −1.73%∼3.83%s38417 9601 91.35 91.93 −0.34%∼0.29%s35932 4800 97.49 99.99 −2.44%∼0.06%s38584 9645 96.5 97.65 −0.76%∼0.42%

coverage curves rise to 91.50 and 91.24% after 1988 patternswith the MSIC sequence and “Best case, LFSR,” respectively.Hence, the uniform distribution of MSIC patterns alleviatesthe dependency relationship between the test length and TPG’sinitial states.

The above conclusion can also be confirmed from anotherperspective. Table III shows the fault coverage range thatMSIC can achieve with the same test length for a given CUT.For every benchmark CUT, 50 fault simulations have beencarried out with 50 different seeds. Columns labeled SFCminand SFCmax refer to the min and max stuck-at fault coveragewith the same test length, which is under the column “TL”.The column “δrange” refers to the relative error range of thefault coverage for a given CUT. The i th relative error, i.e., δi ,can be given by

δi =SFCi − 1

50

50∑i=1

SFCi

150

50∑i=1

SFCi

× 100% (11)

where SFCi is the SFC value of the i th simulation for a givenCUT. It can be seen from this table that the maximum absolutevalue of relative error is less than 3.83%, which shows thatthe TL is independent of the seed.

LIANG et al.: TEST PATTERNS OF MULTIPLE SIC VECTORS 621

TABLE IV

FAULT COVERAGE COMPARISON

CUTMSIC-TPG LFSR [7] [21]

TL SFC TFC SFC TFC TL SFC TL SFC

c2670 1988 91.5 82.46 91.24 70.23 NA NA 1988 91.5

c3540 1052 97.65 92.08 97.8 90.66 NA NA 1052 97.8

c5315 1129 99.62 95.99 98.73 57.97 NA NA 1111 99.7

c6288 112 98.45 93.8 98.22 92.92 87 99.56 NA NA

c7552 1024 95.55 89.68 95.21 80.17 8491 94.08 NA NA

s13207 9942 93.66 81.35 90.9 80.04 9942 92.4 78832 97.7

s15850 9533 94.21 80.93 90.81 65.37 9533 90.6 96413 98.8

s38417 9601 91.35 89.04 91.66 85.81 9601 91.7 116208 97.5

s35932 4800 97.59 62.99 96.5 63.86 NA NA NA NA

s38584 9645 97.16 81.08 94.24 80.01 9645 94.1 79360 99.3

TABLE V

TOTAL AND PEAK POWER REDUCTION OF CUTS

CUTPtot /uW � Ptot Ppeak /uW � Ppeak [25]

MSIC LFSR MSIC LFSR �Ptot �Ppeak

c2670 19.9 38.55 48.4 312.4 433.1 27.9 47 6

c3540 46.6 81.44 42.8 755.5 918.3 17.7 14 1

c5315 55.1 110 50 821.8 1157 29 48 25

c6288 274.8 366.2 25 1994 2363 15.6 21 14

c7552 69.6 137 49.2 1012 1502 32.6 NA NA

Average 93.2 146.63 43.08 979.1 1274.6 24.5 32 11

s13207 359.8 462.1 22.14 3986 5082 21.6 47 39

s15850 509.9 648.6 21.38 5370 6471 17 29 30

s38417 136.4 2083 34.52 12980 19190 32.4 NA NA

s35932 1312 1858 29.39 20190 20790 3 NA NA

s38584 1494 1983 24.66 18000 19560 8 15 36

Average 762.4 1406.9 26.41 12105 14218 16.4 30.3 35

V. PERFORMANCE ANALYSIS

To analyze the performance of the proposed MSIC-TPG,experiments on ISCAS’85 benchmarks and standard full-scandesigns of ISCAS’89 benchmarks are conducted. The perfor-mance simulations are carried out with the Synopsys DesignAnalyzer and Prime Power. Fault simulations are carriedout with Synopsys Tetramax. Synthesis are carried out withNangate library based on 45-nm typical technology. The testfrequency is 100 MHz, and the power supply voltage is 1.1 V.The test application method is test-per-clock for ISCAS’85benchmarks and test-per-scan for ISCAS’89 benchmarks. Thenumber of scan chains is 10 for s13207 and s15850, and 20for s38417, s35932 and s38584.

A. Performances of MSIC-TPGs

Table II summarizes the simulation results about MSIC-TPGs. The first three columns are the name, the numberof PIs, and the size of the CUT. The next two columnsare the widths of the seed generator and the SIC counter.The columns under “MSIC-TPG” and “LFSR” are the testoverheads of the two methods in area, total power, and peakpower, where the columns labeled “�” are the corresponding

overhead percentages. The results of [21] and [24] are alsoincluded for comparison.

For ISCAS’85 benchmarks, the area overheads of MSICand LFSR are 21%–157% and 22%–258%, respectively.The MSIC-TPG thus incurs less area overhead than the LFSR.Taking c2670’s TPGs for example, the LFSR TPG contains233 DFFs and 3 XOR gates, while the MSIC-TPG contains 233XOR gates in the XOR array, 16 DFFs in the Johnson counter,15 DFFs and 3 XOR gate in the seed generator, and 67 addi-tional logic gates for the control and clock circuit. The numberof total equivalent gates is about 2309 for the conventionalLFSR and 1089 for the MSIC-TPG.

For ISCAS’89 benchmarks, the seed width is selected asa half the number of Pls for s13207 and s15850, and 20for s38417, s35932, and s38584. As shown in Fig. 3(b),the primary inputs are applied with the outputs of the XOR

gates and seed generator, respectively. Simulation results with45-nm technology show that TPGs’ area overheads are2.0%–7.5% with MSIC-TPGs, and 0.9%–7.7% with the con-ventional LFSRs. Both methods do not have a high impact onarea overhead of the CUT.

Although the sizes of benchmarks vary more than 30 timesin Table II, the total power of the MSIC-TPG only varies from12.07 to 27.17 μW and from 17.5 to 25.51 μW for ISCAS’85

622 IEEE TRANSACTIONS ON VERY LARGE SCALE INTEGRATION (VLSI) SYSTEMS, VOL. 21, NO. 4, APRIL 2013

and ISCAS’89 benchmarks, respectively. The correspondingaverage total power overhead percentage is only 1.84% forISCAS’89 benchmarks because of their larger sizes, and theaverage power overhead percentage is 27% for ISCAS’85benchmarks. In terms of peak power, both the MSIC-TPGand the LFSR-TPG have negligible impacts for ISCAS’89benchmarks. However, the LFSR consumes much more totalpower than the MSIC-TPG for ISCAS’85 benchmarks.

The TPG in [21] imposes 12%–15% more area overhead,and consumes 14%–21.87% less total power against the con-ventional LFSR. The TPG in [24] has an average of 6.9% morearea overhead than the conventional LFSR. Compared with theTPGs in [21] and [24], the MSIC-TPG imposes compatiblearea overhead and consumes less total power.

B. Fault Coverage Comparison

Table IV shows the fault coverages for ISCAS benchmarkswith the MSIC-TPG, the conventional LFSR, and the methodsin [7] and [21]. In this table, the columns labeled SFC, TFC,and TL refer to the stuck-at fault coverage, transition faultcoverage, and test length, respectively. The TFC values of thistable correspond to launch-on-shift test patterns. In order toachieve fair comparisons, for ISCAS’89 benchmarks, our TLsare chosen to be the same as those in [7]. For the first threeISCAS’85 benchmarks, our TLs are chosen according to [21].The last two ISCAS’85 benchmarks are selected to havesimilar fault coverages as [7].

Compared with the conventional LFSR, the MSIC-TPGachieves similar stuck-at fault coverage for ISCAS’85 bench-marks and higher stuck-at fault coverage for ISCAS’89 bench-marks except for s38417. It also achieves higher transitionfault coverage for both ISCAS’85 and ISCAS’89 benchmarksexcept for s35392.

Compared to the LT-LFSR method in [21], it can be seenfrom the ISCAS’85 benchmarks that, with the same TL, theMSIC-TPG achieves similar test efficiency. Compared to theTPG in [7], the results with ISCAS’89 benchmarks show that,with the same TL, the MSIC-TPG has higher efficiency, exceptfor s38417. Note that, for ISCAS’89 benchmarks, the resultsof our method and those of [21] in the table should not becompared directly because of the different TLs.

C. Average and Peak Power Reduction

Table V compares the total and peak power reductions ofCUTs with the MSIC-TPG and with the LFSR-TPG, wherecolumns labeled “Ptot” and “Ppeak” refer to the CUT’s totalpower and peak power with the MSIC-TPG, respectively.Columns labeled “�Ptot” and “�Ppeak” refer to the percent-ages of different methods’ total power reduction and peakpower reduction with respect to the LFSR method, respec-tively. The results of [25] are also included for comparison.

For ISCAS’85 benchmarks, the MSIC-TPG saves25%–50.0% total power and 15.6%–32.6% peak poweragainst the conventional LFSR. All total power reductionsand peak power reductions are higher than those withvariable-length ring counter in [25].

For ISCAS’89 benchmarks, the MSIC-TPG can save21.38%–34.52% total power and 3%–32.4% peak poweragainst the conventional LFSR. The total power reductionsand peak power reductions are not higher than those with thevariable-length ring counter in [25]. One reason for this isthat the power simulation results for the MSIC-TPG are with45-nm technology, whereas results in [25] are with 0.25-μmtechnology. Experimental results show that leak power con-tributes about 10% to total power with 45-nm technology,but contributes little to total power with 0.18- or 0.25-μmtechnology.

VI. CONCLUSION

This paper has proposed a low-power test pattern generationmethod that could be easily implemented by hardware. It alsodeveloped a theory to express a sequence generated by linearsequential architectures, and extracted a class of SIC sequencesnamed MSIC. Analysis results showed that an MSIC sequencehad the favorable features of uniform distribution, low inputtransition density, and low dependency relationship betweenthe test length and the TPG’s initial states. Combined withthe proposed reconfigurable Johnson counter or scalable SICcounter, the MSIC-TPG can be easily implemented, and isflexible to test-per-clock schemes and test-per-scan schemes.For a test-per-clock scheme, the MSIC-TPG applies SICsequences to the CUT with the SRAM-like grid. For a test-per-scan scheme, the MSIC-TPG converts an SIC vector to lowtransition vectors for all scan chains. Experimental results andanalysis results demonstrate that the MSIC-TPG is scalable toscan length, and has negligible impact on the test overhead.

REFERENCES

[1] Y. Zorian, “A distributed BIST control scheme for complex VLSIdevices,” in 11th Annu. IEEE VLSI Test Symp. Dig. Papers, Apr. 1993,pp. 4–9.

[2] P. Girard, “Survey of low-power testing of VLSI circuits,” IEEE DesignTest Comput., vol. 19, no. 3, pp. 80–90, May–Jun. 2002.

[3] A. Abu-Issa and S. Quigley, “Bit-swapping LFSR and scan-chainordering: A novel technique for peak- and average-power reduction inscan-based BIST,” IEEE Trans. Comput.-Aided Design Integr. CircuitsSyst., vol. 28, no. 5, pp. 755–759, May 2009.

[4] P. Girard, L. Guiller, C. Landrault, S. Pravossoudovitch, J. Figueras,S. Manich, P. Teixeira, and M. Santos, “Low-energy BIST design:Impact of the LFSR TPG parameters on the weighted switching activ-ity,” in Proc. IEEE Int. Symp. Circuits Syst., vol. 1. Jul. 1999, pp.110–113.

[5] S. Wang and S. Gupta, “DS-LFSR: A BIST TPG for low switchingactivity,” IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.,vol. 21, no. 7, pp. 842–851, Jul. 2002.

[6] F. Corno, M. Rebaudengo, M. Reorda, G. Squillero, and M. Violante,“Low power BIST via non-linear hybrid cellular automata,”in Proc. 18th IEEE VLSI Test Symp., Apr.–May 2000, pp.29–34.

[7] P. Girard, L. Guiller, C. Landrault, S. Pravossoudovitch, and H. Wun-derlich, “A modified clock scheme for a low power BIST test patterngenerator,” in Proc. 19th IEEE VTS VLSI Test Symp., Mar.–Apr. 2001,pp. 306–311.

[8] D. Gizopoulos, N. Krantitis, A. Paschalis, M. Psarakis, and Y. Zorian,“Low power/energy BIST scheme for datapaths,” in Proc. 18th IEEEVLSI Test Symp., Apr.–May 2000, pp. 23–28.

[9] Y. Bonhomme, P. Girard, L. Guiller, C. Landrault, and S. Pravos-soudovitch, “A gated clock scheme for low power scan testing of logicICs or embedded cores,” in Proc. 10th Asian Test Symp., Nov. 2001, pp.253–258.

LIANG et al.: TEST PATTERNS OF MULTIPLE SIC VECTORS 623

[10] C. Laoudias and D. Nikolos, “A new test pattern generator for highdefect coverage in a BIST environment,” in Proc. 14th ACM Great LakesSymp. VLSI, Apr. 2004, pp. 417–420.

[11] S. Bhunia, H. Mahmoodi, D. Ghosh, S. Mukhopadhyay, and K. Roy,“Low-power scan design using first-level supply gating,” IEEE Trans.Very Large Scale Integr. (VLSI) Syst., vol. 13, no. 3, pp. 384–395, Mar.2005.

[12] X. Kavousianos, D. Bakalis, and D. Nikolos, “Efficient partial scan cellgating for low-power scan-based testing,” ACM Trans. Design Autom.Electron. Syst., vol. 14, no. 2, pp. 28-1–28-15, Mar. 2009.

[13] P. Girard, L. Guiller, C. Landrault, and S. Pravossoudovitch, “A testvector inhibiting technique for low energy BIST design,” in Proc. 17thIEEE VLSI Test Symp., Apr. 1999, pp. 407–412.

[14] S. Manich, A. Gabarro, M. Lopez, J. Figueras, P. Girard, L. Guiller,C. Landrault, S. Pravossoudovitch, P. Teixeira, and M. Santos, “Lowpower BIST by filtering non-detecting vectors,” J. Electron. Test.-TheoryAppl., vol. 16, no. 3, pp. 193–202, Jun. 2000.

[15] F. Corno, M. Rebaudengo, M. Reorda, and M. Violante, “A new BISTarchitecture for low power circuits,” in Proc. Eur. Test Workshop, May1999, pp. 160–164.

[16] S. Gerstendorfer and H.-J. Wunderlich, “Minimized power consumptionfor scan-based BIST,” in Proc. Int. Test Conf., Sep. 1999, pp. 77–84.

[17] A. Hertwing and H. Wunderlich, “Low power serial built-in self-test,”in Proc. Eur. Test Workshop, 1998, pp. 49–53.

[18] S. Wang and W. Wei, “A technique to reduce peak current and averagepower dissipation in scan designs by limited capture,” in Proc. AsiaSouth Pacific Design Autom. Conf., Jan. 2007, pp. 810–816.

[19] N. Basturkmen, S. Reddy, and I. Pomeranz, “A low power pseudo-random BIST technique,” in Proc. IEEE Int. Conf. Comput. Design:VLSI Comput. Process., Sep. 2002, pp. 468–473.

[20] S. Wang and S. Gupta, “LT-RTPG: A new test-per-scan BIST TPGfor low switching activity,” IEEE Trans. Comput.-Aided Design Integr.Circuits Syst., vol. 25, no. 8, pp. 1565–1574, Aug. 2006.

[21] M. Nourani, M. Tehranipoor, and N. Ahmed, “Low-transition test patterngeneration for BIST-based applications,” IEEE Trans. Comput., vol. 57,no. 3, pp. 303–315, Mar. 2008.

[22] X. Zhang, K. Roy, and S. Bhawmik, “POWERTEST: A tool for energyconscious weighted random pattern testing,” in Proc. 12th Int. Conf.VLSI Design, Jan. 1999, pp. 416–422.

[23] S. F. Q. Abdallatif and S. Abu-Issa, “Multi-degree smoother for lowpower consumption in single and multiple scan-chains BIST,” in Proc.11th Int. Symp. Qual. Electron. Design, Apr. 2010, pp. 689–696.

[24] S. Chun, T. Kim, and S. Kang, “A new low energy BIST using astatistical code,” in Proc. Asia South Pacific Design Autom. Conf., Mar.2008, pp. 647–652.

[25] B. Zhou, Y.-Z. Ye, Z.-L. Li, X.-C. Wu, and R. Ke, “A new low power testpattern generator using a variable-length ring counter,” in Proc. Qual.Electron. Design, Mar. 2009, pp. 248–252.

Feng Liang received the B.E. degree from Zhengzhou University, Henan,China, in 1998, and the M.E. and Ph.D. degrees from Xi’an JiaotongUniversity (XJU), Xi’an, China, in 2001 and 2008, respectively.

He is currently an Associate Professor with the School of Electronic andInformation Engineering, XJU. His current research interests include VLSIdesigns, test, and computer architecture.

Luwen Zhang received the B.E. degree in electronic science and technologyfrom the Xi’an University of Technology, Xi’an, China, in 2009. He iscurrently pursuing the M.E. degree in electrical engineering from Xi’anJiaotong University, Xi’an.

His current research interests include VLSI testing.

Shaochong Lei received the M.S.E. and Ph.D. degrees from Xi’an JiaotongUniversity (XJU), Xi’an, China, in 1990 and 2007, respectively.

He is currently an Associate Professor with the Microelectronics Engineer-ing Department, XJU. His current research interests include VLSI computer-aided designs, system-on-chip testing, and design-for-test.

Guohe Zhang received the B.S. degree in microelectronics and the Ph.D.degree in electronic science and technology from Xi’an Jiaotong University(XJU), Xi’an, China, in 2003 and 2008, respectively.

He is currently with the Department of Microelectronics, XJU. His currentresearch interests include low-power and high-speed CMOS circuit designs,semiconductor device designs, and modeling.

Kaile Gao received the B.E. degree from the Changchun University of Scienceand Technology, Changchun, China, in 2010. He is currently pursuing theM.E. degree in electrical engineering with Xi’an Jiaotong University, Xi’an,China.

His current research interests include design-for-test.

Bin Liang received the B.E. degree in electrical engineering from the Xi’anUniversity of Technology, Xi’an, China, in 2010. He is currently pursuing theM.E. degree in electrical engineering with Xi’an Jiaotong University, Xi’an.

His current research interests include design-for-test, system-on-chiptesting, and VLSI testing.