Cadence 2 Report Yang Lu

-

Upload

abuharithhamzah -

Category

Documents

-

view

85 -

download

3

Transcript of Cadence 2 Report Yang Lu

ESE 570 Cadence Lab Assignment 2:

Introduction to Spectre, Manual Layout Drawing and

Post Layout Simulation (PLS)

Yang Lu, Department of Material Science and Engineering

Exercises Part A

i. Transient Simulation

Schematic View

Simulation Results

C = 0F

Rise time = 3.063ns – 3.011ns = 52ps

Fall time = 1.083ns – 1.019ns = 64ps

C=100fF

Rise time = 3.239ns – 3.033ns = 206ps

Fall time = 1.329ns – 1.053ns = 276ps

ii. Inverter DC characteristics

Schematic View

Simulation Results

Vth decreases with larger W.

Wp/Wn=3/1, Wn=5um:

Vout=VDD/2=2.5V, Vin=2.78V

Exercises Part B

i. Inverter

Layout Extracted Layout

LVS

PLS

C = 0F

Rise time = 3.063ns – 3.011ns = 52ps

Fall time = 1.083ns – 1.019ns = 64ps

Vth=2.635V

C = 100fF

Rise time = 3.239ns – 3.033ns = 206ps

Fall time = 1.329ns – 1.053ns = 276ps

Vth=2.633V

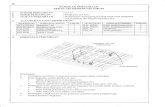

ii. 2-input NAND

Layout Extracted Layout

LVS

PLS

1. Case 1: in1, in2 0V-5V or 5V-0V

C = 0F

Rise time = 3.045ns – 3.008ns = 37ps

Fall time = 1.221ns – 1.054ns = 167ps

C=100fF

Rise time = 3.136ns – 3.022ns = 114ps

Fall time = 1.666ns – 1.124ns = 542ps

2. Case 2: in2=5V, in1 0V-5V or 5V-0V

C = 0F

Rise time = 3.081ns – 3.014ns = 67ps

Fall time = 1.211ns – 1.041ns = 170ps

C = 100fF

Rise time = 3.257ns – 3.034ns = 223ps

Fall time = 1.64ns – 1.091ns = 549ps

3. Case 3: in1=5V, in2 0V-5V or 5V-0V

C = 0F

Rise time = 3.108ns – 3.017ns = 91ps

Fall time = 1.231ns – 1.061ns = 170ps

C = 100fF

Rise time = 3.275ns – 3.033ns = 242ps

Fall time = 1.656ns – 1.106ns = 550ps

Case C trise (ps) tfall (ps)

in1, in2 0V-5V or 5V-0V 0F 37 114

in1, in2 0V-5V or 5V-0V 100fF 167 542

in2=5V, in1 0V-5V or 5V-0V 0F 67 223

in2=5V, in1 0V-5V or 5V-0V 100fF 170 549

in1=5V, in2 0V-5V or 5V-0V (worst case) 0F 91 242

in1=5V, in2 0V-5V or 5V-0V (worst case) 100fF 170 550

iii. 2-input NOR

Layout Extracted Layout

LVS

PLS

1. Case 1: in1, in2 0V-5V or 5V-0V

C=0F

Rise time = 3.173ns – 3.025ns = 148ps

Fall time = 1.051ns – 1.012ns = 39ps

C=100fF

Rise time = 3.513ns – 3.074ns = 439ps

Fall time = 1.176ns – 1.031ns = 145ps

2. Case 2: in1=0V, in2 0V-5V or 5V-0V

C=0F

Rise time = 3.203ns – 3.053ns = 150ps

Fall time = 1.179ns – 1.027ns = 152ps

C=100fF

Rise time = 3.523ns – 3.081ns = 442ps

Fall time = 1.414ns – 1.052ns = 362ps

3. Case 3: in2=0V, in1 0V-5V or 5V-0V

C=0F

Rise time = 3. 163ns – 3.018ns = 145ps

Fall time = 1.097ns – 1.022ns = 75ps

C=100fF

Rise time = 3.497ns – 3.055ns = 442ps

Fall time = 1.414ns – 1.052ns = 286ps

Case C trise (ps) tfall (ps)

in1, in2 0V-5V or 5V-0V 0F 148 39

in1, in2 0V-5V or 5V-0V 100fF 439 145

in2=0V, in1 0V-5V or 5V-0V 0F 145 75

in2=0V, in1 0V-5V or 5V-0V 100fF 442 286

in1=0V, in2 0V-5V or 5V-0V (worst case) 0F 150 152

in1=0V, in2 0V-5V or 5V-0V (worst case) 100fF 442 362

iv. D flip flop

Layout

Extracted Layout

LVS