Sistem Digital

-

Upload

ferry-setiyawan -

Category

Documents

-

view

69 -

download

9

description

Transcript of Sistem Digital

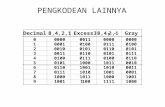

BAB 10

PERCOBAAN 9

Encoder, Dekoder, dan Demultiplekser (HDL)

10.1 Tujuan

1. Praktikan dapat memahami blok rangkaian kombinasional dari

enkoder 4-ke-2, dekoder 3-ke-8 dan demux 3-ke-8.

2. Praktikan dapat mengimplementasikan blok rangkaian tersebut

sebagai modul menggunakan desain secara prosedural maupun

struktural.

3. Praktikan dapat mengaplikasikan modul (reusable) tersebut untuk

membuat suatu rangkaian berbasis komponen.

4. Praktikan dapat memahami (dan membedakan) hasil sintesis

rangkaian RTL (register transfer level) kedua bentuk desain tersebut

serta utilisasi/penggunaan device untuk desain tersebut.

5. Praktikan dapat menganalisis perilaku masukan-keluaran desain di

board Starter Kit.

10.2 Alat dan bahan

1. Board Starter Kit Spartan-3E berbasis Xilinx FPGA XC3S500E-

4FG320C. Modul (komponen) I/O yang akan digunakan dalam

praktikum :

a) 4 buah tombol push-button (BTN North, BTN East, BTN South,

BTN West)

b) 4 buah saklar geser (SW0, SW1, SW2, SW3)

c) 8 buah LED (LD0-7)

2. Kabel USB dengan konektor tipe-B

3. Adaptor sumber daya DC 5 Volt

4. Software Xilinx ISE Webpack 11.1

10.3 Dasar teori

Board Starter Kit beserta komponennya dan Xilinx ISE Webpack

telah dijelaskan dalam modul praktikum 1. Di bab ini akan dijelaskan

tentang blok rangkaian kombinasional yang akan digunakan dalam

praktikum ini. Blok rangkaian kombinasional yang akan dibahas adalah

enkoder 4-ke-2, dekoder 3-ke-8 dan demux 3-ke-8.

10.3.1. Enkoder 4-ke-2

Enkoder 4-ke-2 mengkodekan data 4-masukan ke

dalam kode keluaran 2-bit. Keluaran merepresentasikan

bilangan biner yang mengidentifikasikan masukan mana yang

bernilai '1'. Salah satu aplikasi enkoder adalah untuk

mentransmisikan informasi di sistem digital. Salah satu tipe

enkoder adalah priority encoder. Tiap input mempunyai level

prioritas (Gambar 10.1).

Gambar 10.1 Enkoder prioritas 4-ke-2

10.3.2. Dekoder 3-ke-8

Rangkaian dekoder 3-ke-8 mendekodekan data

masukan 3-bit menjadi data 8-keluaran. Hanya satu keluaran

yang diaktifkan (one-hot encoding) dan tiap keluaran

menyatakan valuasi nilai masukannya. Dekoder 3-ke-8 dapat

tersusun atas 2 buah dekoder 2-ke-4 (Gambar 1). Salah satu

aplikasi dekoder adalah untuk mendekodekan jalur alamat di

chip memori.

Gambar 10.2 Dekoder 3-ke-8

10.3.3. Demultiplekser 3-ke-8

Demux 3-ke-8 dapat diimplementasikan dengan

menggunakan dekoder 3-ke-8. Jalur data {w0,w1,w2}

digunakan sebagai jalur kontrol untuk menempatkan data 1

masukan En ke salah satu dari 8 jalur keluaran.

Gambar 10.3 Demultiplekser 3-ke-8

10.4 Langkah kerja dan hasil percobaan

10.4.1. Membuat project baru

Langkah-langkah membuat proyek baru :

1. Pilih menu File New Project (Alt+F W). Dialog pop-up

New Project Wizard akan muncul. Ketik field Name dengan

nama proyek (Format: <nama_kelompok>-Percobaan9-

RangkaianKombinasional). Browse lokasi proyek/Location

(folder <nama_kelompok>). Isi field Description dengan

penjelasan tentang proyek. Tipe source top-level

menggunakan HDL. Tuliskan field Name, Location dan

Description dalam lembar kegiatan.

Gambar 10.4 New Project Wizard

2. Klik tombol Next. Jendela Device Properties muncul. Pilih

Family (Spartan3E), Device (XC3S500E), Package

(FG320) dan Speed (-4). Properti ini adalah device-

dependent (Starter Kit menggunakan FPGA XC3S500E-

4FG320C), jadi harus dimasukkan dengan benar. Set

Preferred Language dengan Verilog. Catat field Family,

Device, Package dan Speed ini dalam lembar kegiatan.

Gambar 10.5 Device Properties

3. Setelah memilih next pada jendela device properties,

muncul project summary. Klik finish untuk memulai

percobaan.

Gambar 10.6 Project Summary

10.4.2. Membuat file desain .v (procedural) dan .ucf

File .v (verilog) dibuat dengan memilih tipe source

verilog module pada new source wizard seperti pada gambar

10.7 sebelah kiri, sedangkan file .ucf dengan memilih tipe

source implementation constraints file seperti pada gambar

sebelah kanan :

Gambar 10.7 New source wizard

Pada new source wizard, cukup beri nama pada source

yang akan dibuat dan tidak perlu memberikan definisi input

maupun output, cukup klik next saja lalu finish. Pemberian

nama file implementation constraints (.ucf) dan verilog (.v)

seperti pada gambar berikut :

Gambar 10.8 rangkaian kombinasional.ucf

Gambar 10.9 dekoder_proc

Gambar 10.10 dekoder_proc_top

Gambar 10.11 enkoder_proc

Gambar 10.12 enkoder_proc_top

Gambar 10.13 demux_proc

Gambar 10.14 demux_proc_top

Selanjutnya tinggal memberikan list kode program

seperti pada point 10.4.3.

10.4.3. Hipotesis

Berikut tampilan dari kode rangkaian kombinasional (.ucf ) :

Gambar 10.15 rangkaian kombinasional.ucf

Kode di atas berfungsi untuk menerapkan atau

menterjemahkan komponen abstrak pada sistem verilog menjadi

komponen nyata pada board praktikum.

Berikut tampilan dari masing-masing verilog module :

1. Dekoder 3-ke-8

a. File verilog dekoder_proc

Gambar 10.16 Listing dekoder_proc

Definisi perilaku desain di atas, jalur output (y_out)

ke-“n” akan diberikan nilai 1 jika enable = 1 dan nilai “n”

ditentukan oleh nilai 3-bit biner “w_in” sebagai selektor.

Perilaku tersebut disesuaikan dengan dekoder 3-ke-8.

b. File verilog dekoder_proc_top

Gambar 10.17 Listing dekoder_proc_top

Kode di atas memanggil modul verilog dekoder_proc

dan menerapkan input SW [ 2, 1, 0 ] sebagai “w_in” dan

input SW[3] sebagai input “enable”. LED sebagai indikator

jalur “y_out”.

2. Enkoder 4-ke-2

a. File verilog enkoder_proc

Gambar 10.18 Listing enkoder_proc

Definisi perilaku dari desain, kedua jalur output (y_out)

diatur untuk memberikan kode biner 2-bit sesuai dengan

jalur input (w_in) tertinggi yang bernilai 1 dan

mengabaikan jalur input yang lebih kecil.

Output zero_reg digunakan untuk membedakan kondisi

saat terdapat input pada jalur 1 (zero = 1) dan kondisi tanpa

input (zero = 0). Perilaku tersebut disesuaikan dengan

enkoder prioritas 4-ke-2.

b. File verilog enkoder_proc_top

Gambar 10.19 Listing enkoder_proc_top

Kode di atas memanggil modul verilog enkoder_proc dan

menerapkan input SW [ 3, 2, 1, 0 ] sebagai “w_in”. LED

sebagai indikator zero dan jalur y_out.

3. Demux 3-ke-8

a. File verilog demux_proc

Gambar 10.20 Listing demux_proc

Definisi perilaku dari desain di atas, jalur output

(data_out) ke-“n” akan diberikan nilai yang sama dengan

nilai data_in, dimana nilai “n” ditentukan oleh nilai 3-bit

biner “sel” sebagai selektor. Perilaku tersebut disesuaikan

dengan demux 3-ke-8.

b. File verilog demux_proc_top

Gambar 10.21 Listing demux_proc_top

Kode di atas memanggil modul verilog demux_proc

dan menerapkan input SW [ 2, 1, 0 ] sebagai “w_in” dan

input BTN_NORTH sebagai input “data_in”. LED sebagai

indikator jalur data_out.

10.4.4. Mengkompilasi dan membangkitkan file programming

Sebelum mentransfer program ke dalam board starter

kit, pastikan tidak ada kesalahan dalam program dengan

Generate Programming File. Lakukan 3 kali dengan mengganti

top modul untuk dekoder, enkoder, dan demux.

Gambar 10.22 Generate Programming File

10.4.5. Membangkitkan dan menganalisa skematik RTL

Untuk melihat Skematik RTL dari program, gunakan

Synthesize –XST lalu View RTL Schematic :

Gambar 10.23 View RTL Schematic

Jendela Create RTL Schematic akan muncul.

Tambahkan semua komponen dalam folder Primitive lalu Create

Schematic. Berikut 3 gambar schematic yang di dapat :

Gambar 10.24 RTL dekoder

Gambar 10.25 RTL enkoder prioritas

Gambar 10.26 RTL demux

10.4.6. Konfigurasi device target FPGA menggunakan iMPACT

Proses terakhir dari praktikum adalah menjalankan

program pada board starter kit. Gunakan Manage Configuration

Project (iMPACT) untuk proses ini. Pastikan Board sudah

menyala dan terhubung dengan komputer.

Gambar 10.27 Membuka ISE iMPACT

Jendela ISE iMPACT akan muncul. Klik ganda pada

Boundary Scan, kemudian klik kanan dan pilih Initialize Chain

untuk menginisialisasi Boundary Scan.

Gambar 10.28 Boundary Scan

Jendela untuk memasukkan file konfigurasi FPGA

muncul. Pilih file konfigurasi (.bit) untuk konfigurasi FPGA.

Device lain biarkan bypass. Chain JTAG sudah terkonfigurasi,

klik kanan pada device, kemudian program. Bila berhasil, akan

tampil Program Succeeded. Selanjutnya adalah memeriksa

jalannya program pada board starter kit.

10.5 Analisa Percobaan

10.5.1. Enkoder

Tabel 10. 1 Enkoder prioritas 4-ke-2

SW3 SW2 SW1 SW0Y1

(LED1)Y2

(LED0)ZERO_REG

(LED7)

0 0 0 0 0 0 0

0 0 0 1 0 0 1

0 0 1 0 0 1 1

0 0 1 1 0 1 1

0 1 0 0 1 0 1

0 1 0 1 1 0 1

0 1 1 0 1 0 1

0 1 1 1 1 0 1

1 0 0 0 1 1 1

1 0 0 1 1 1 1

1 0 1 0 1 1 1

1 0 1 1 1 1 1

1 1 0 0 1 1 1

1 1 0 1 1 1 1

1 1 1 0 1 1 1

1 1 1 1 1 1 1

Ternyata hasil pengamatan sama dengan hipotesis : dimana kode

[y1,y2] merepresentasikan jalur input [SW] tertinggi yang aktif,

dan jika tak ada jalur input yang aktif, maka “zero_reg” bernilai 0.

10.5.2. Dekoder

Tabel 10. 2 Dekoder 3-ke-8

Masukan Keluaran

S

W

3

S

W

2

S

W

1

S

W

0

LED

0

LED

1

LED

2

LED

3

LED

4

LED

5

LED

6

LED

7

1 0 0 0 1 0 0 0 0 0 0 0

1 0 0 1 0 1 0 0 0 0 0 0

1 0 1 0 0 0 1 0 0 0 0 0

1 0 1 1 0 0 0 1 0 0 0 0

1 1 0 0 0 0 0 0 1 0 0 0

1 1 0 1 0 0 0 0 0 1 0 0

1 1 1 0 0 0 0 0 0 0 1 0

1 1 1 1 0 0 0 0 0 0 0 1

Pada dekoder pun, hasil pengamatan sama dengan hipotesis : jalur

keluaran y_out (LED ke-n) akan bernilai 1 jika enable (SW3)

bernilai 1 dan nilai n itu sendiri merupakan nilai 3-bit biner input

pada [SW2,SW1,SW0] yang berfungsi sebagai selektor.

10.5.3. Demultiplekser

Tabel 10. 3 Demux 3-ke-8

Masukan Keluaran

BTN_North

S

W

2

S

W

1

S

W

0

L

E

D

0

L

E

D

1

L

E

D

2

L

E

D

3

L

E

D

4

L

E

D

5

L

E

D

6

L

E

D

7

1 0 0 0 1 0 0 0 0 0 0 0

1 0 0 1 0 1 0 0 0 0 0 0

1 0 1 0 0 0 1 0 0 0 0 0

1 0 1 1 0 0 0 1 0 0 0 0

1 1 0 0 0 0 0 0 1 0 0 0

1 1 0 1 0 0 0 0 0 1 0 0

1 1 1 0 0 0 0 0 0 0 1 0

1 1 1 1 0 0 0 0 0 0 0 1

Hasil pengamatan demux di atas pun sama dengan hipotesis : jalur

keluaran data_out (LED ke-n) akan diberikan nilai yang sama

dengan nilai data_in (BTN_North) dimana nilai n ditentukan oleh

nilai 3-bit biner input pada [SW2,SW1,SW0] yang berfungsi

sebagai selektor.

10.6 Kesimpulan

1. File berekstensi .v dibuat untuk mendesain modul yang diinginkan sedangkan file berekstensi .ucf dibuat untuk menginisialisasi komponen dalam board starter kit.

2. Modul_proc digunakan untuk mendesain perilaku sistem dengan data input dan output yang diinginkan.

3. Sedangkan proc_top untuk menggunakan desain pada modul_proc dengan merepresentasikan komponen untuk input/output.

4. Enkoder berperan menggunakan outputnya untuk menentukan kode biner yang menunjukkan jalur input tertinggi yang aktif ataupun bernilai 1.

5. Dekoder memiliki fungsi untuk memberikan nilai tertentu pada outputnya sesuai dengan kode biner pada inputnya. Dalam praktikum ini, nilai kode biner pada input merepresentasikan jalur output yang harus diberikan nilai 1.

6. Demultiplekser bertujuan untuk menyeleksi jalur output yang harus diaktifkan untuk melewatkan data_in. Dalam praktikum ini, nilai kode biner pada input merepresentasikan jalur output yang harus diaktifkan atau diberi nilai sama dengan data_in.

7. Perbedaan dari dekoder dan demultiplekser adalah : pada dekoder hanya terdapat input untuk selektor, sedangkan pada demultiplekser terdapat tambahan input untuk data_in.

8. Perbedaan dari dekoder dan demultiplekser adalah dekoder

merupakan rangkaian 3 ke 8 mengkodekan data masukan 3bit

menjadi data 8 keluaran sedangkan Enkoder adalah rangkaian 4 ke

2 dengan 4 masukan data dan 2 keluaran bitnya.