metode tabulasi

description

Transcript of metode tabulasi

A. KOMPETENSI

1. Setelah selesai pembelajaran mahasiswa mampu.

2. Menyelesaikan pers sum of product dalam bentuk rangkaian minimal dengan metode

tabulasi.

3. Menentukan rangkaian yang mengandung hazard statik 1 dan hazard statik 0.

4. Mengatasi rangkaian yang mengandung hazard statik 1 dan hazard statik 0.

B. SUB KOMPETENSI

Mahasiswa mampu.

1. Membuat tabel tabulasi.

2. Merealisasikan rangkaian.

3. Menentukan rangkaian mengandung hazard statik 1 dan hazard statik 0.

4. Mengatasi rangkaian mengandung hazard statik 1 dan hazard statik 0.

C. DASAR TEORI

1. Metode tabulasi Quin Mac Cluskey: mengelompokkan menurut jumlah satunya,

mencentang antar anggota kelompok yang berdekatan dengan pola hanya berbeda

satu. Posisi, menulis hasilnya Lakukan sampai semua kelompok teridentifikasi.

Ulangi hal yang sama pada step berikutnya.sampai sudah tidak ada lagi pasngan yang

dicentang.

2. Peta Karnaugh : area yang terpisah indikator adanya potensi Hazard.

3. Hazard Statik satu : seharusnya output bernilai Satu tapi terdapat down spike Nol.

4. Hazard Statik Nol : Seharusnya output bernilai Nol tapi terdapat spike Satu.

D. ALAT/INSTRUMEN

1. IC OR

2. IC AND

3. IC NAND

4. Catu Daya DC 5V

5. CRO

6. Pembangkit pulsa 1 kHz

E. KESELAMATAN KERJA

1. Perhatikan Positip dan Negatif.

2. Perhatikan variabel yang berubah, variabel yang konstan nol, dan konstan satu.

F. LANGKAH KERJA

1. Selesaikan sum of Produc soal diskusi dengan metode Tabulasi.

2. Cek hasil dengan Peta karnaugh.

3. Realisasikan dengan gerbang NAND.

4. Amati hazard yang terjadi.

5. Atasi Hazard dengan menambahkan rangkaian sesuai dengan peta Karnaug.

6. Amati tidak terjadi Hazard.

7. Buatlah persamaan infers dengan melihat sel nol pada peta Karnaugh.

8. Inverskan kembali dengan metode dualitas .

9. Implementasikan formula dengan menggunakan gerbang OR.

10. Amati hazard yang terjadi.

11. Atasi Hazard dengan menambahkan rangkaian sesuai dengan peta Karnaugh.

12. Amati tidak terjadi Hazard.

G. BAHAN DISKUSI/PRAKTIKUM

Yang harus di kerjakan

1. F(A,B,C,D) =` ∑ 0, 2, 4, 5, 6 8, 9,11, 12, 14, 15

2. F(A,B,C,D) =` ∑ 3, 4, 5, 6 11, 12, 13, 15

H. HASIL PENGAMATAN

1. Menyelesaikan soal bahan diskusi dengan metode tabulasi seperti dibawah

ini :

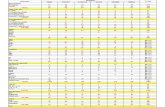

0 0,2 (2) ⱱ 0,4,2,6 (4,2)2 0,4 (4) ⱱ 0,2,4,6 (2,4) ⱱ4 0,8 (8) ⱱ 0,4,8,12 (4,8) ⱱ8 2,6 (4) ⱱ 0,8,4,12 (8,4)5 4,5 (1) 4,6,12,14 (2,8) ⱱ6 4,6 (2) ⱱ 4,12,6,14 (8,2)9 4,12 (8) ⱱ12 8,9 (1)11 8,12 (4) ⱱ14 6,14 (8) ⱱ15 9,11 (2) 12,14 (2) ⱱ 11,15 (4)

14,15 (1) 0 2 4 5 6 8 9 11 12 14 15 4,5 (1) ⱱ ⱱ 8,9 (1) ⱱ ⱱ 9,11 (2) ⱱ ⱱ 11,15 (4) ⱱ ⱱ 14,15 (1) ⱱ ⱱ

0,2,4,6 (2,4) ⱱ ⱱ ⱱ ⱱ 0,4,8,12(4,8) ⱱ ⱱ ⱱ ⱱ 4,6,12,14 (2,8) ⱱ ⱱ ⱱ ⱱ ⱱ ⱱ ⱱ ⱱ ⱱ

A B C D4,5 (1) 0 1 0 1 = A’BC’9,11 (2) 1 0 1 1 = AB’D14,15 (1) 1 1 1 1 = ABC0,2,4,6 (2,4) 0 1 1 0 = A’D’0,4,8,12 (4,8) 1 1 0 0 = C’D’

Jadi rumus booleannya soal no 1 adalah F (ABCD) = C’D’ + A’BC’ + AB’D + ABC + A’D’

Untuk mengecek metode tabulasi di atas, maka bisa dicheck dengan metode kernaugh map seperti gambar 1.0 di bawah ini :

Gambar 1.0

Jadi rumus Boolean untuk kernaugh map diatas adalah :F (ABCD) = C’D’ + A’BC’ + AB’D + ABC + A’D’

Dari hasil metode kernaugh map diatas maka dapat disimpulkan bahwa metode tabulasi diatas adalah benar, karena metode tabulasi memiliki hasil yang sesuai dengan hasil pada metode tabulasi

Dari rumus Boolean hasil dari metode kernaugh map pada gambar 1.0 dan metode tabulasi diatas,maka dapat dibuat suatu rangkaian hazzard dasar yaitu:

Gambar 1.1 (F (ABCD) = C’D’ + A’BC’ + AB’D + ABC + A’D’)

Rangkaian dasar diatas masih memliki hazard 1 dan dapat diperbaiki mengunakkan metode kernaugh map seperti gambar 1.2 seperti dibawah ini :

Gambar 1.2

a. Menentukan VCC, Ground dan clock pada rangkaian hazard 1 pertama:A = 1 = VCCB = 0 = GroundC = 0 – 0 = GroundD = 0 – 1 = VCCDari kondisi diatas maka dapat dibuat suatu rangkaian seperti dibawah ini menggunakan IC NAND

Gambar 1.3 (F (ABCD) = C’D’ + A’BC’ + AB’D + ABC + A’D’)

Pulsa Clock gambar 1.3

Hazard 1

Gambar 1.4

Hazzard pada gambar 1.4 dapat diatasi dengan menambahkan rangkaian AB’C’Setelah ditambahkan rangkaian AB’C’ maka rangkaian menjadi:F (ABCD) = C’D’ + A’BC’ + AB’D + ABC + A’D’+ AB’C

Gambar 1.5 F( (ABCD) = C’D’ + A’BC’ + AB’D + ABC + A’D’+ AB’C )

Pulsa clock gambar 1.5

Hazard hilang

Gambar 1.6 b. Menentukan VCC, Ground dan clock pada rangkaian hazard 1 kedua :

A = 1 – 1 = VCCB = 0 – 1 = ClockC = 1 = VCCD = 1 = VCCDari kondisi diatas maka dapat dibuat suatu rangkaian seperti dibawah ini menggunakan IC NAND :

Gambar 1.7(F (ABCD) = C’D’ + A’BC’ + AB’D + ABC + A’D’)

Pulsa clock gambar 1.7

Hazzard 1

Gambar 1.8

Hazzard 1 pada gambar 1.8 dapat diatasi dengan menambahkan rangkaian ACDSetelah ditambahkan rangkaian ACD maka rangkaian menjadi:F (ABCD) = A’BC’ + AB’D + ABC + A’D’ + C’D’ + ACD

Gambar 1.9 (F (ABCD) = C’D’ + A’BC’ + AB’D + ABC + A’D’+ ACD )

Pulsa clock gambar 1.9

Hazzard hilang

Gambar 2.0

c. Menentukan VCC, Ground dan clock pada rangkaian hazard 1 ketiga :A = 0 – 1 = ClockB = 1 – 1 = VCCC = 0 – 1 = ClockD = 0 – 0 = GroundDari kondisi diatas maka dapat dibuat suatu rangkaian seperti dibawah ini menggunakan IC NAND

Gambar 2.1(F (ABCD) = C’D’ + A’BC’ + AB’D + ABC + A’D’)

Pulsa clock gambar 2.1

Hazzard 1

Gambar 2.2

Hazzard 1 pada gambar 2.2 dapat diatasi dengan menambahkan rangkaian BD’Setelah ditambahkan rangkaian BD’ maka rangkaian menjadi:F (ABCD) = A’BC’ + AB’D + ABC + A’D’ + C’D’ + BD’

Gambar 2.3 (F (ABCD) = A’BC’ + AB’D + ABC + A’D’ + C’D’ + BD’) Pulsa clock gambar 2.3

Hazzard hilang

Gambar 2.4

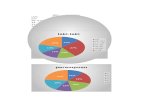

Selain hazard 1, pada soal F(A,B,C,D) = ∑ 0, 2, 4, 5, 6 8, 9,11, 12, 14. 15 juga memiliki hazzard 0 dapat dilihat pada kernaugh map dibawah ini :

Dari rumus kernaugh map diatas maka diperoleh rumus Boolean :F (A,B,C,D) = ABC’D + AB’CD’ + A’BCD + A’B’DDari rumus Boolean maka dapat dibuat rangkaian dasar seperti di bawah :

Gambar 2.5 (F (A,B,C,D) = ABC’D + AB’CD’ + A’BCD + A’B’D)Rangkaian dasar pada gambar 2.5 diatas masih memliki hazard 0, untuk mengatasi hazzard 0 tersebut maka kita dapat membuat rangkaian baru melalui metode kernaugh map seperti gambar di bawah ini :

Gambar 2.6

d. Menentukan VCC, Ground dan clock pada rangkaian hazard 0 :A = 0 – 0 = GroundB = 0 – 1 = ClockC = 1 = VCCD = 1 = VCCDari kondisi diatas maka dapat dibuat suatu rangkaian seperti dibawah ini menggunakan IC NAND

Gambar 2.7(F (A,B,C,D) = ABC’D + AB’CD’ + A’BCD + A’B’D)

Pulsa clock gambar 2.3

Hazzard 0

Gambar 2.8 Hazzard 0 pada gambar 2.8 dapat diatasi dengan menambahkan rangkaian

A’CDSetelah ditambahkan rangkaian A’CD maka rangkaian menjadi:F (ABCD) = A’BC’ + AB’D + ABC + A’D’ + C’D’ + A’CD

Gambar 2.9 (F (ABCD) = A’BC’ + AB’D + ABC + A’D’ + C’D’ + A’CD)

Pulsa clock gambar 2.9

Hazardhilang

Gambar 2.9

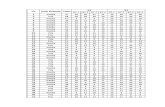

2. Untuk menyelesaikan soal no 2 F(A,B,C,D) =` ∑ 3, 4, 5, 6 11, 12, 13, 15 kita dapat

langsung menggunakan metode kernaugh map seperti dibawah ini :

Gambar 3.0

Dari metode kernaugh map diatas maka didapatkan rumus Boolean yaitu :F ( A,B,C,D ) = BC’ + ACD + B’CD + A’BD’Dari rumus booelan diatas maka dapat kita buat suatu rangkaian dasar seperti di bawah ini :

Gambar3.1

Rangkaian dasar pada gambar 3.1 diatas masih memliki hazard 1, untuk mengatasi hazzard 1 tersebut maka kita dapat membuat rangkaian baru melalui metode kernaugh map seperti gambar di bawah ini :

Gambar 3.2

a. Menentukan VCC, Ground dan clock pada rangkaian hazard 1 :A = 1 = VCCB = 1 = VCCC = 0 – 1 = ClockD = 1 – 1 = VCCDari kondisi diatas maka dapat dibuat suatu rangkaian seperti dibawah ini menggunakan IC NAND

Gambar 3.3 (F ( A,B,C,D ) = BC’ + ACD + B’CD + A’BD’)

Pulsa clock gambar 3.3

Hazzard1

Gambar 3.4

Hazzard 1 pada gambar 3.4 dapat diatasi dengan menambahkan rangkaian ABDSetelah ditambahkan rangkaian ABD maka rangkaian menjadi:F (ABCD) = BC’ + ACD + B’CD + A’BD’ +ABD

Gambar 3.5 F (ABCD) = BC’ + ACD + B’CD + A’BD’ +ABD

Pulsa clock gambar 3.5

Hazzard hilang

Gambar 3.6

I. Kesimpulan1. Dalam merancang metode tabulasi harus benar – benar teliti dalam

mengeliminasi dan mengelompokan bilangan menurut binernya.

2. Dalam praktek mengunakan metode tabulasi kita dapat melakukan

pengecekan dengan metode kernaugh map dengan cara mencocokan hasil akhir rumus

booelan yang didapat dari kedua metode tersebut.

3. Dalam metode kernaugh map, apabila kita melingkari sel yang berlogik 1

maka akan terjadi hazard 1. Sedangkan apabila kita melingkari sel yang berlogik 0

maka kemungkinan akan terjadi hazzard 0.

4. Untuk menghilangkan hazard pada hazard 1 maupun 0 kita dapat

menggunakan cara melingkari sel – sel yang belum dilingkari. Biasanya sel – sel yang

belum dilingkari ini terletak diantara dua buah sel yang telah dilingkari sebelumnya

dan bersebelahan. Apabila kita sudah menemukan dan melingkari sel – sel yang

tersebut maka kita akan menemukan persamaan rumus boolean baru. Tambahkan

persamaan baru tersebut ke rangkaian bersangkutan yang terjadi hazard.dalam praktik

ini terdapat 3 buah hazard 1 dan 1 buah hazzard 0. Penyelesainya harus satu persatu

dengan pedoman pembuatan rangkaian yang berbeda – beda sesuai letak hazardnya.

Pedoman pembuatan rangkaian dengan melihat letak dan logic hazard yang terdapat

pada Kernaugh map :

1 – 1 = VCC 0 – 0 = Ground

0 – 1 = Clock

5. Hazard 1 merupakan sum of product,sedang hazard 0 product of sum

6. Apabila ingin membuat rangkaian yang menggunakan NAND alangkah

lebih baik dan mudah apabila kita mengetahui rangkaian dasar dan gerbang – gerbang

dasar ( AND, OR, NOT ) yang digunakan terlebih dahulu.