Fliflop Dan Register

-

Upload

desi-novianti -

Category

Documents

-

view

47 -

download

13

Transcript of Fliflop Dan Register

S-R FLIP-FLOP GERBANG NAND

S R Q Q’

0 0 Q Q’

0 1 Q Q

1 0 1 0

1 0 TERLARANG

S-R FLIP-FLOP BERDETAK

DETAK/CLOCK

S R Q Q’

0 X X Q Q’

1 0 0 Q Q’

1 0 1 Q Q

1 1 0 1 0

1 1 0 TERLARANG

TOGGLE/ T FLIP-FLOP

DETAK/CLOCK

T Q Q’

0 X Q Q’

1 0 Q Q’

1 1 Q’ Q

DELAY/ D FLIP-FLOP

DETAK/CLOCK

T Q Q’

0 X Q Q’

1 0 0 1

1 1 1 0

J-K FLIP-FLOP BERDETAK

DETAK/ CLOCK

J K Q Q’

0 X X Q Q’

1 0 0 Q Q’

1 1 0 1 0

1 0 1 0 1

1 1 1 TOGGLE/ Q’

Q

MASTER-SLAVE FLIP-FLOP BERDETAK

DETAK/ CLOCK

J K Q MASTER

Q’ MASTER

Q SLAVE

Q’ SLAVE

Q Q’

0 X X Q Q’

1 0 0 Q Q’

1 1 0 1 0

1 0 1 0 1

1 1 1 TOGGLE/ Q’

Q

CONTOHMASTER-SLAVE FLIP-FLOP BERDETAK

DETAK/ CLOCK

J K Q MASTER

Q’ MASTER

Q SLAVE

Q’ SLAVE

Q Q’

1 0 1

1 0 0

0 1 0

0 0 1

1 1 1

Half adder merupakan untai logika yang keluarannya merupakan jumlah dari 2 bit

full adder merupakan untai logika yang keluarannya merupakan jumlah dari 3 bit

Merupakan n flip-flop yang disusun sebagai penyimpanan

Data biner dapat dipindahkan secara berurutan satu persatu / seridan dapat dipindahkan secara bersamaan / paralel

Ada 4 cara register geser dapat digunakan untuk menyimpan dan memindahkan data yaitu:

1. Masukan seri ke keluaran paralel (SIPO)2. Masukan seri ke keluaran seri (SISO)3. Masukan paralel ke keluaran seri (PISO)4. Masukan paralel ke keluaran paralel (PIPO)

Terdapat masukan bit 1011, lakukan pemindahan secara

a. Serib.Paralel

1011 -> Q1=1, Q2=0, Q3=1, Q4=1KET: MSB ADALAH Q1=1

LSB ADALAH Q4=1

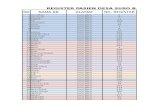

DETAK MASUKAN KELUARAN

bit logika Q1 Q2 Q3 Q4

1 Q4 1 1 0 0 0

2 Q3 1 1 1 0 0

3 Q2 0 0 1 1 0

4 Q4 1 1 0 1 1

DETAK

MASUKAN KELUARAN

D1D2D3D4 Q

1 1011 1011

Digunakan untuk penggeseran isi register satu atau 2 bit kearah kanan atau kiri untuk memanipulasi data dalam operasi matematika

Diketahui bit : 01010Lakukan geser kiri dan geser kanan

dalam register

0 1 0 1 0

0 1 0 1

0 0 1 0 1

Geser bit dari paling kiri ke kanan

Bit yang kosong, isi dengan bit 0

Geser bit dari paling kanan ke kiri

Bit yang kosong, isi dengan bit 0

0 1 0 1 0

0 1 1 0

0 1 1 0 0

Pencacah adalah suatu rangkaian logika sekuensial yang dapat berfungsi untuk menghitung jumlah pulsa yang masuk dan akan dinyatakan dalam bentuk biner.

Pada umumnya counter di bentuk dari beberapa buah flip-flop yang jumlahnya disesuaikan dengan kebutuhan.

Menurut cara pemberian pulsa clock, pencacah dapat di bagi ke dalam : 1. Pencacah tak sinkron 2. Pencacah sinkron

Sedangkan menurut urutan hitungan yang terbentuk pada keluarannya, pencacah dapat di bagi ke dalam : 1. Pencacah naik 2. Pencacah turun 3. Pencacah naik-turun

Pada pencacah tak sinkron, pulsa clock hanya diberikan kepada masukan clock salah satu flip-flop, sedangkan untuk sinyal clock flip-flop yang lainnya di ambil dari keluaran flip-flop sebelumnaya.

Untuk memilih agar rangkaian berfungsi sebagai penghitung naik kita berikan logika Low pada input UP/ DOWN, sedangkan untuk penghitung turun kita berikan logika High.

Penghitung ini melaksanakan hitungan sampai nilai tertentu (N) kemudian secara otomatis mereset semua output menjadi nol.

1. Hitung FF yang menjadi FBJika ada 2 FF maka.. Pencacah 2 pangkat2=4

2. Hitung faktor pembagi dimana pencacah-1Jika pencacah yang didapat adalah 4 (poin 1) maka faktor pembagi adalah 4-1=3 (011)

3. Sehingga didapat pulsa masukan sebanyak 2xfaktor pembagiJika faktor pembagi adalah 3 maka pulsa masukan sebanyak 2x3=6 (110)

Dengan 2 blok feedback

Dalam aplikasi penghitung asinkron kita mendapat masalah dengan penundaan waktu propagasi, yang disebabkan system serial atau ripple.

Untuk perlu penyempurnaan system clock yaitu dengan menerapkan system clock secara serempak pada setiap Flip-flop, system ini sering disebut dengan Penghitung Sinkron.

Penghitung sinkron ini menggunakan D-FF, dimana clock disambungkan jadi satu, output dari D-FF pertama disambungkan ke input D-FF kedua, Output D-FF kedua disambungkan ke input D-FF ketiga, output D-FF ketiga disambungkan ke input D-FF keempat dan output dari D-FF keempat disambungkan balik ke input D-FF pertama.

Penghitung sinkron ini menggunakan D-FF, dimana clock disambungkan jadi satu, output dari D-FF pertama disambungkan ke input D-FF kedua, Output D-FF kedua disambungkan ke input D-FF ketiga, output inverting D-FF ketiga disambungkan ke input D-FF pertama.

Dalam perencanaan suatu sistem digital, terkadang diperlukan suatu alat yang dapat membangkitkan pulsa untuk masukan clock, atau suatu alat yang berfungsi sebagai debuonce switch.

multivibrator di bagi ke dalam tiga jenis, yaitu:

1. Moltivibrator monostabil 2. Multivibrator bistabil 3. Multivibrator astabil

Multivibrator ini mempunyai hanya satu kondisi stabil, pada rangkaian ini diperlukan adanya pulsa trigger dan konstanta waktu pulsa output ditentukan oleh resistor Rx dan kapasitor Cx:

Berdasar gambar diatas pulsa 5 volt berfungsi sebagai inisialisasi monostabil,

dengan adanya pulsa tersebut output Q berubah kondisi dari Low menjadi High.

Pada saat kondisi output Q = High, maka proses pengisian kapasitor dilakukan melalui Rx dan saat kapasitor penuh output Q kembali ke Low.

Untuk menghitung kondisi High output Q dapat dilakukan dengan menggunakan rumus:

tw = 0,45 . Rx . Cx

tw = 0,45 . 100K . 10uF (misal Rx=100K dan Cx=10uF)

tw = 0,45 detik

Tw adalah lebar pulsa Nilai factor konstanta 0,45 tergantung pada tipe IC

yang dipakai untuk itu perlu melihat data book IC misal untuk SN 74121 harga konstantanya adalah 0,70,

Multivibrator ini memiliki 2 output yang masing-masing memiliki kondisi stabil,

satu dalam kondisi Low maka output lainnya berlogika High.

Kedua output tersebut dalam teknik digital sering ditandai dengan notasi Q dan Q’, berikut merupakan tabel kebenaran dari multivibrator ini:

Multivibrator astabil adalah multivibrator yang tiak mempunyai keadaan stabil. Multivibratr jenis ini digunakan sebagai pembangkit pulsa.

Multivibrator astabil yang di bentuk dari dua buah gerbang NAND diperlihatkan dalam gambar 9.2.

Periode pulsa yang dihasilkan rangkaian ini tergantung pada besar-kecilnya resistor dan kapasitor yang dipasangkan, berikut merupakan rumus untuk menghitung frekuensi yang dihasilkan rangkaian menggunakan Ic-LM555:

Contoh: Rangkaian dilengkapi dengan RA = 10K, RB= 50K dan C1 = 0,01 μF. Hitung f?

Jawab:

1. Buatlah pencacah naik sebanyak 12 pulse/clock dengan output Q0, Q1,Q2. dimana Q0 adalah MSB dan Q2 adalah LSB

2. Buatlah pencacah turun sebanyak 12 pulse/clock dengan output Q0, Q1,Q2,Q3. dimana Q3 adalah MSB dan Q0 adalah LSB

3. Buatlah pencacah modulo 16 dengan output Qa, Qb,Qc,Qd. Dimana Qa adalah MSB dan Qd adalah LSB

4. Batlah pencacah dengan Feedback yang terdiri atas FF0, FF1, FF2, FF3. dimana feedback adalah FF3 menuju FF2. tampilkan gambar dan tabel kebenarannya.

5. Diketahui pulse/ clock sebanyak 8 a. Hitunglah ring untuk modulo 6

b. Hitunglah jonhson untuk modulo 8

6. Hitunglah kondisi High output Q multivibrator mono stabil yang memiliki factor konstanta 0,8 dengan Rx=150K dan Cx=15µF

7. Tentukan frekuensi dari multivibrator astabil dengan IC-LM555 dimana RA = 50K, RB= 100K dan C1 = 0,5 μF.