Desain Sistem Prototyping Pembangkit Kode VHDL untuk ...

Transcript of Desain Sistem Prototyping Pembangkit Kode VHDL untuk ...

Desain Sistem Prototyping Pembangkit Kode VHDL untuk KompilatorCode Composer Studio pada FPGA Spartan 3

Debyo Saptono'

tJurusan Teknik Elektro, Fakultas Teknologi Industri, Universitas Gunadarmadebyo@staff. eunadarma. ac. id

Abstrak

Dewasa ini perkembangan implementasi metodologi sistem prototyping telah mengalami kemajuanyang sangat cepat terutama dalam electronic embedded system di bidang telekomunikasi, control, daninstrumentasi. Ketersediaan di tangan konsumen (time to morket) yang lebih cepat menjadi salah satu alasanperancang elektronika mengembangkan pada sistem FPGA dibandingkan menggunakan system ASIC karenalebih mudah dilakukan proses renconJigurable terhadap rancangan yang dihasilkan.

VHDL sebagai salah satu bahasa pemrograman yang digunakan pada FPGA menjadi salah satu pilihansebagai dasar prototyping ( VHDL-based rapid protoptying) dan dikolaborasikan dengan kompilator CodeComposer Studio (CCS) untuk menghasilkan keluaran kode mesin prosesor DSP keluarga Texas Instrument.

Metode desain system prototyping pada model implementasi hanya menggunakan sumber dayaperangkat keras prosesor DSP yang dibutuhkan seperti aplikasi sobel untuk menghasilkan kode VHDL yanglebih ringkas sehingga meminimalkan kebutuhan gates pada FPGA. Dari hasil pengujian sederhana padaspartan3 menunjukkan desain sistem prototyping dapat bekerja dengan baik pada FPGA.

Kata kunci: System Prototyping, VHDL, Code Composer Studio, FPGA

1. Pendahuluan

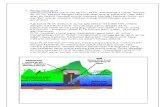

Saat ini sistem prototyping telah mengalamiperubahan alur diagram alir dari model yangpertama kali dirumuskan oleh IEEE. Perubahan inicenderung lebih sederhana dengan hanya didasarkanbeberapa teknik meliputi modelling, evaluation, danAutomated progam generation [4]. Teknik modelingdiperlukan untuk dapat menangkap arsitektur sistemdan sekitarnya yang akan di buat prototypingrya.Teknik evaluation dapat dilalcukan melalui simulasidan pengujian. Terakhir, teknik automated programgeneration yang akan menghasilkan kode hasilsecara otomatis. Sistem prototyping padaperkembangannya menjadi sebuah metodologi yangbanyak diimplementasikan manusia dalam berbagaibidang, salah satunya dalam bidang sistem teftanam( embedded system).Sistem tertanam (Embedded System) di bidangelektronika mempunyai peranan yang penting dalamberbagaijenis aplikasi bidang pengolahan sinyal dancitra secara waktu nyata seperti kendali pemrosesan,telekomunikasi, satelit dan bidang kesehatan. Dalamkurun waktu 10 tahun terakhir, kapasitaspeningkatan teknologi mempunyai peranan pentingdengan kelahirannya System-on-Chrp(SoC). Saatini, teknologi SoC telah hadir di berbagai aspekkarena keuntungan dalam teknik desain yang

memungkinkan penciptaan sistem yang kompleks,terdiri berbagai jenis komponen berbeda-bedadalam sistem chip yang sama [][2][3]. Hal inimemungkinkan peningkatan sangat tinggi didukungpersaingan dan faktor yang sangat kuat sepertibiaya, performansi, dan batasan waktu untukkebutuhan pasar sehingga akan menjadikan faktorpenting untuk keberhasilan suatu produk.Salah satu produk yang banyak digunakan dalamembedded sistem terutama bidang pengolahan sinyaldigital adalah CPU DSP TMS320c62xx. Prosesor inidibuat oleh Texas Instrument dengan menggunakanarsitektur clustered-VllW ( Very Long InstructionWords) dengan berbagai varians yang mendukungoperasi floating-point dan non floating-pointft0].Untuk mengoperasikannya diperlukan kemampuanmelakukan pernrograman bahasa C atau bahasasassembler. Texas Instruments juga menyediakankompilator CCS (Code Composer Studio) yang akanmengubah bahasa sumber tersebut menjadi bahasatarget berupa kode heksadesimal[9].Untuk mengimplementasikan model CPU inikedalam teknologi FPGA (Field ProgrammableGate Array) diperlukan model perterjemah ke dalambahasa pemograman VHDL atau verilog, sehinggatidak diperlukan peralatan fisiknya tetapi cukupmenanfaatkan kompilator CCS tersebut, sehinggamengurangi biaya produksi.

289

Teknologi FPGA dengan kemampuan rekonfigurasidan kemampuan untuk mengintegrasikannya denganmudah telah menjadi satu kunci pemecahan rapidprototyping dalam sistem tertanam[3][4][5]. Dalamhal ini pengguna yang mampu memprogram denganbaik dapat meningkatan desain perangkat kerasuntuk hifga produksi yang lebih rendah secarasignifikan dan mereka memperoleh banyakkeuntungan dari pemecahan dengan teknologiAS[C(Applicotion Specific Integrated Circuit).FPGA menawarkan beberapa rangkaian built-inyang mempunyai keunggulan seperti memori,pengali, dan jalur komunikasi kecepatan tinggi [6].Karakteristik yang paling menarik dari FPGAdengan sifat dapat direkonfigurasi adalahmemungkinkan untuk membuat prototype secarasepat dan berfungsi secara penuh sebagai pemecahanmelalui emulasi dan verifikasi atau bahkanditanamkan dalam sistem akhir. Untuk mendesainSoCs (sysrerzs on chip) dengan pemanfaatan FPGAssaat ini terus mengalami peningkatan.

2. Metode Penelitian

2.1 Flow chart system prototyping

Dalam bagian ini penulis akan mendiskripsikanmetodologi sistem prototyping yang digunakandalam perancangan tools pembangkit kode VHDL.Berdasarkan definisi IEEE mengenai sistemprototyping terbagi menjadi 3 teknik dasar meliputi :1. Teknik modeling

Pada bagian ini tools harus mampu mengenaldengan baik cara kerja kompilator CCS yangdidesain untuk arsitektur clustered-VllWterutama cara kerja decoding instmksi yangterdapat pada kode heksadesimalnya.

2. Teknik evaluationPada bagian ini tools akan melakukan analisis

kode heksadesimal berdasarkan unit-unitfungsional yang terdapat pada CPU, register-register yang digunakan dan jenis instuksi yangdilakukan.

3. Teknik Automated Program GenerationPada bagian ini tools akan membangkitkan kodeVHDL dari hasil evaluasi.

Berikut ini diagram alir menjelaskan metodologisistem protofyping yang diterapkan pada toolspembangkit kode VHDL.

Code Composer Sludio

!!Kode Heksadesimal

!lAnal is is l<ode t iao FL,

{!Elasis data

El6rdasarkan Anal is is l<od€

Gambar l. Diagram alir sistem prototyping berbasisVHDL

2.2 Deskripsi Code Composer Studio (CCS)

Pada bagian ini penulis hanya menjelaskan secarasingkat output dalam bentuk assember dari CCSyang terlihat seperti pada gambar 2 berikut :

Erilr'at msrru6 vlnlil.. llnstruksr l",lnemonrc I -

j , \ \

otrlc{Ll-q.S Ol9oDOiS \n- .Ll --qj--{l0000008'0 0:10_r0J.q ADD .Llf 1B-r.-A-l0co000cs 0:10J0>-s ADD Ll\ :,8'+-4J

! ' t i ,

Itko,J"rnstil;riahr,reG;Aei,m-;l I

F r-q *-"g",k*x, "'".fil;l

Gambar 2. Deskripsi kode assembler hasil kompilasi

Dari output kompilator dapat disusun dalam deretaninstmksi paralel dengan satu alamat VLIW tunggalsebagai berikut

rPsl .u(sr \ , /LlW ke-1

l l20002000 05290c79 000403E2

1iAlamat VLI! J instruksi VLIW ka-2

t Afi;;___lI dalam c I

{l

06 r 329qnti

rst ' i . {s r-1! : ' , . .v <e'3

Masing-masing instmksi VLIW tersebut dalamformat biner tersusun atas beberapa informasipenting,. Insffuksi vLIw ke -l dengan kode heksa :05290079 jika diubah ke biner masing-masing bitmempunyai arti sebagai berikut :

co

oooo oooooooo 0101 0010 1001I

Ib31

Keterangan:

a1 1' t 1001I

I' - bo

:

F

b0 menunjukkan paralisme dengan instruksisebelumnya.

bl..M :menunjukkan unit fungsional yangdigunakan

bs..bl I : menunjukkan jenis operasi yang dikerjakanbl3 .. bl7 : menunjukkan register operand 1bl8 ..b22: menunjukkan register operand 2b23 ..b27 : menunjukkan register tujuanb28.. b3l:menunjukkan register kondisional

eksekusi.

2.3 Implementasi pada FPGA

Board yang digunakan dalam ujicoba inimenggunakan chip seri spartan3 yang dibuat olehDigilent. Beberapa bagian penting yangberhubungan langsung dengan pengujian antara lainChip spartan dengan jumlah gerbang yangdisediakan sebesar 1.000.000 buah gerbang.Semakin banyak gerbang yang disediakan akansemakin baik. Di dalam chip ada beberapakomponen yang penting selain gerbang antara lain :gerbang sel yang setaft 4.320 buah, blok RAMdengan ukuran l8K-bit sebanyak 12 buah, DigitalClock Managers (DCMs) sebanyak 4 buah, danFlash EPROM Xilinx XCFO2S kapasitas 2Mbitdengan I Mbit sebagai memori data non-volatileatau penyimpanan kode aplikasi setelah FPGAdikonfigurasikan. Memori SRAM Aslmchronousberkecepatan tinggi sebesar lM-bye.

Gambar 3. Modul FPGA yang digunakan dalameksperiment

3. Hasil dan Pembahasan

Untuk menghasilkan kode heksadesimal darikompilator CCS diperlukan program aplikasimasukan yang dapat ditulis menggunakan bahasapemogftlman ANSI C. Dalam percobaan ini penulismencoba aplikasi filter sobel dan melakukan analisispenggunaan register-register yang tardapat padamasing-masing unit fungsional CpU DSpTMS320C620l dengan hasil sebagai berikut :

Tabel l. Pemetaan jenis-jenis operasi yangdilakukan oleh masing-masing FU

FU Jenis OperasiLI move, addition, negate, subtraction,

zero valueL2 move, addition, compare, subtraction,

zero. absolute valueS1 Register allocation, Addition, delayS2 move, subtraction, shiftM1 Not usedM2 multiplyD1 read memory, addition, subtractionD2 write memory read memory,addition,

Tabel 2. Pemetaan fungsi register sebagai masukanuntuk masing-masing FU

Tabel 3. Pemetaan fungsi register sebagai keluaranuntuk masing-masing FU

Itrit Firyst-r.lL L

2S1

5I t1 i L

?

I 'aa.B.r.Is

FIA6

RAIlR,Al2

RcAs

I) laaBatk

B

RB1RB2

RB3RE4

REJ

RBl 3

Uill Frrysbn.l

t

L

?

S

t

s2

N

I

I!! f

t

]]

Pad.

Elarfs

A

tiA6

R.gsP.aaB-rf<B

Gambar 4. Model VHDL untuk kompilator CCS.

Tabel 4. Penggunaan resources pada FPGA

4. Kesimpulan dan Saran

Penerapan metodologi sistem protopying sangatberguna untuk menghasilkan tools yang dapatmembantu implementasi sistem embedded padateknologi FPGA. Hal ini mendorong perancangelektronika mengembangkan diri tanpa harusmengetahui lebih dalam pernrograman C danassembler yang banyak digunakan pada sistemembedded.Pengembangan metodologi ini di masa depandiharapkan diterapkan pada sistem multiprosesordengan memanfaatkan perkembangan teknologiFPGA.

Daftar Pustaka:

tll Brost Vincent, Fan Yang, Michel Paindavoine,and Nicolas Famrgi4 "Multiple ModularVLIW Processors Based on FPGA", Joumal ofElecfronic Imaging (SPIE), 16(2):110, April-June 2007.Balakrishnan K, and N.A. Touba, Matrix-based sofiware test data decompression forsystem on a chip, Journal of Systemsarchitecture, Vol.50, pp.247 -256, 2O04.Cesario W, Gauthier et ?1, Object-basedH\I//SW component interconnection model forinterface design in system-on-a chip circuits,The journal of systems and software, No.70,pp229-244"2004.

I4l Fabrice Kordon and Luqi Fellow, AnIntroduction to Rapid System Prototyping,IEEE Transactions on engineering, Vol. 28,No.9, September2002.

t5l Fisher Joshep A, Paolo Faraboschi and CliffYoung, Embedded Computing: A VLIWApproach to Architecture, Elsevier MorganKauftnan, second edition. 2005.

t6] K. Parnell and R. Bryner., Comparing andContrasting FPGA and Microprosessor SystemDesign and Development,Xilirx, July 2004.

t7l Pong P. Chu, FPGA Prototyping By VHDLExamples, A John Wiley and Sons, Inc, 2008.

t8l Saptono Debyo, Vincent Brost, Fan Yang andEri Prasetyo, Design space explorationfor acustom vliw architecture: Direct photo printerhardware setting using vex compiler, In Proc.of the 4th International Conference on SITIS2008, November 2008

t9] Texas Instrument , Code Composer StudioU s er's Gui de, http ://www.ti.com/.

[0] Texas Instrument, tms320c62xx CPU andInstruction Set Reference Guide; http://www.ti.com/

[l] Stefan Bjornander, Microsoft Visual C++Windows Applications by Example, PacktPublishing Ltd, 2008.

I2l

l - r . rI iLr l, l

i

Resources Jumlahdisunakan

Maksimum tersedia

Rasio

Slice 2912 7680 37%Slice Flipflop

1830 15.360 l l Yo

Innut Luts 4800 15.360 3t%UObuffers

t64 173 94%

BlockRAM

5 ai 20%

GCB 8 8 100%DCM 4 4 l00Yo

292