@2014,Eko Didik Elemen Rangkaian Sekuensial · Register Counter/Pencacah Ringkasan Lisensi...

Transcript of @2014,Eko Didik Elemen Rangkaian Sekuensial · Register Counter/Pencacah Ringkasan Lisensi...

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Rangkaian SekuensialKuliah#11 TSK205 Sistem Digital - TA 2013/2014

Eko Didik Widianto

Sistem Komputer - Universitas Diponegoro

23 Maret 2014

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 1

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Umpan Balik

I Sebelumnya dibahas tentang rangkaian kombinasionalyang nilai keluarannya di suatu saat hanya ditentukanoleh nilai-nilai masukannya pada saat itu

I multiplekser, dekoder, demultiplekser, enkoder dan codeconverter

I Peraga 7-segmen

I Teorema ekspansi Shannon untuk mendesain rangkaianlogika menggunakan multiplekser

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 2

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Tentang Kuliah

I Membahas tentang rangkaian sekuensial yang keluarannya tidakhanya tergantung dari masukan saat ini, juga dari nilai keluaransebelumnya

I Rangkaian ini membutuhkan elemen penyimpan nilai darisinyal logika

I Bahasan:

I prinsip rangkaian sekuensialI elemen penyimpan 1 bit latch, yaitu set-reset latch (latch

SR), latch SR tergerbang dan data latch (latch D) sertarangkaian logikanya

I elemen penyimpan 1 bit �ip-�op, meliputi data �ip-�op(DFF), toggle �ip-�op (TFF), JK �ip-�op (JKFF)

I register data n bit dan register geser (shift register)I pencacah naik-turunI pencacah sinkron dan asinkron

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 3

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Kompetensi Dasar

I Setelah mempelajari bab ini, mahasiswa akan mampu:

I [C2] menjelaskan perbedaan antara latch dan �ip-�opI [C4] menganalisis fungsi karakteristik latch set-reset,

latch tergerbang, latch dataI [C4] menganalisis fungsi karakteristik �ip-�op (D, T,

dan JK)I [C3] membedakan perilaku dan rangkaian pencacah

sinkron dan asinkronI [C5] merancang rangkaian n buah �ip-�op menjadi

register data n bit, shift register, pencacah naik/turunsinkron/asinkron serta menganalisisnya

I [C5] merancang dan menganalisis implementasirangkaian sekuensial menggunakan IC TTL

I Link

I Website: http://didik.blog.undip.ac.id/2014/02/25/tkc205-sistem-digital-2013-genap/

I Email: [email protected]

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 4

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

BahasanElemen Penyimpan KeadaanLatch (Pengunci)

Latch SR (Set-Reset)Latch SR TergerbangGated Latch D (Data)IC TTL Latch

Flip-�opFlip-Flop Data (DFF)Flip-�op Toggle (T)Flip-�op JK (JKFF)IC TTL Flip-�op

RegisterRegister DataRegister GeserIC TTL Register

Counter/PencacahPencacah AsinkronPencacah SinkronPencacah Sinkron dengan DFFIC TTL Pencacah

RingkasanLisensi

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 5

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

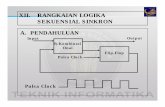

Rangkaian SekuensialElemen Penyimpan dan Statenya

I Rangkaian yang nilai keluarannya tidak hanyatergantung dari masukan saat ini, juga dari nilaikeluaran sebelumnya

I Rangkaian mempunyai elemen penyimpan

I Isi dari elemen penyimpan merepresentasikan keadaan

(state) dari rangkaianI Perubahan nilai masukan dapat menyebabkan keadaan

rangkaian tidak berubah atau berubah ke keadaanbaru

I Rangkaian berubah sesuai urutan keadaan sebagaihasil dari perubahan masukannya

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 6

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Sistem Kontrol Alarm

I Diinginkan rangkaian untuk mengontrol alarm

I Alarm merespon kontrol masukan On/O�

I akan berbunyi saat On/O� = 1I mati saat On/O� = 0

I Alarm berbunyi saat sensor membangkitkan sinyaltegangan positif (Set) jika terjadi event tidak diinginkan

I Diinginkan alarm tetap aktif (berbunyi) walaupunkeluaran sensor tidak aktif (Set=0)

I Alarm dimatikan manual menggunakan kontrol Reset

I Rangkaian ini memerlukan elemen memori untukmengingat bahwa alarm telah aktif hingga datangnyasinyal Reset

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 7

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Elemen Memori

I Menggunakan 2 buah NOT

I mempunyai 2 keadaan yang masing-masing akanberulang tanpa batas, yaitu

I Jika A = 0, maka B = A = 1 dan A = B = 0.Rangkaian selalu menghasilkan B = 1

I Jika A = 1, maka B = A = 0 dan A = B = 1.Rangkaian selalu menghasilkan B = 0

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 8

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Elemen Memori Terkontrol

I Menyediakan mekanisme mengubah keadaan rangkaian

I Load = 0, maka TG2 aktif dan TG1 tidak aktif (feedback)

I Keadaan rangkaian (dan juga keluaran Y) tetap

I Jika Load = 1, maka TG1 aktif dan TG2 tidak aktif (update)

I Masukan Data akan memperbarui nilai A, sehingga nilaikeluaran Y = Data

I Rangkaian berubah keadaannya sesuai Datahttp://didik.blog.undip.ac.id @2014,Eko Didik Widianto 9

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Latch SR(Set-Reset)Latch SRTergerbangGated Latch D(Data)IC TTL Latch

Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Latch

I Elemen memori terkontrol di atas membentuk latch(pengunci)

I Latch merupakan elemen penyimpan 1-bit

I Untuk menyimpan 1-bit data/state diperlukan 1 buahlatch

I Tipe latch berdasarkan fungsinya:

I latch set-reset (SR latch)I SR latch tergerbangI latch data (D latch)

I diaplikasikan untuk mengunci data masukan dan/ataukeluaran suatu rangkaian lain

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 10

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Latch SR(Set-Reset)Latch SRTergerbangGated Latch D(Data)IC TTL Latch

Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Latch SRElemen Memori dengan Gerbang NOR

I Rangkaian latch dapat disusun menggunakan gerbang logika NOR(selain dengan TG)

I Masukannya, Set (S) dan Reset (R), digunakan untukmengubah state/keadaan, Q, dari rangkaian

I Rangkaian tersebut membentuk latch SR

I Perilaku rangkaian:

I Jika R=S=0, maka state tidak berubah (terkunci)I Jika R=1 (S=0 atau S=1), maka state Q=0I Jika R=0 dan S=1, maka state Q=1

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 11

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Latch SR(Set-Reset)Latch SRTergerbangGated Latch D(Data)IC TTL Latch

Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Latch SRRangkaian dan Tabel Karakteristik

I Rangkaian dihubungkan secara cross-coupled

I Saat R=S=0, rangkaian tetap berada di state saat ini

I Baik (Qa = 0 dan Qb = 1) atau (Qa = 1 dan Qb = 0)

I Saat S=1 dan R=0, latch diset ke keadaan dimana Qa = 1 danQb = 0

I Saat S=0 dan R=1, latch diset ke keadaan dimana Qa = 0 danQb = 1

I Saat S=1 dan R=1, Qa = Qb = 0 →Kondisi race

I Terjadi osilasi antara Qa = Qb = 0 dan Qa = Qb = 1http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 12

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Latch SR(Set-Reset)Latch SRTergerbangGated Latch D(Data)IC TTL Latch

Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Analisis Waktu Latch SR

I Jika delay propagasi dari Qa dan Qb sama, osilasi di waktu t10akan berlanjut secara tak terbatas

I Di rangkaian realnya, mungkin terdapat perbedaan dalam delaydan latch berada di salah satu dari 2 keadaan

I Tidak dapat ditentukan (kondisi race), yang lebih cepatmengunci keadaan

I Sehingga, kombinasi S=R=1 merupakan kombinasi yangtidak diijinkan di latch SR

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 13

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Latch SR(Set-Reset)Latch SRTergerbangGated Latch D(Data)IC TTL Latch

Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Recall: Sistem Kontrol Alarm

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 14

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Latch SR(Set-Reset)Latch SRTergerbangGated Latch D(Data)IC TTL Latch

Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Latch SR TergerbangMenambahkan Kontrol Enable

I Latch SR dasar mengubah statenya saat masukannya berubahI Seringkali diinginkan untuk menambah satu sinyal enable ke latch SR

dasar

I Sinyal enable diberikan oleh masukan ClkI Digunakan untuk mengontrol kapan rangkaian dapat mengubah

state-nya

I Saat Clk=0 state tidak berubah, saat Clk=1 statetergantung masukan S dan R

I Disebut sebagai gated SR latch

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 15

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Latch SR(Set-Reset)Latch SRTergerbangGated Latch D(Data)IC TTL Latch

Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Gated SR LatchDiagram Pewaktuan

I Keadaan saat S=R=1 dihindari, menyebabkan keluarantak dapat ditentukan

I Latch set saat Q=1 dan latch reset saat Q=0

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 16

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Latch SR(Set-Reset)Latch SRTergerbangGated Latch D(Data)IC TTL Latch

Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Gated SR LatchRangkaian dengan Gerbang NAND

I Masukan S dan R dibalik dibandingkan denganrangkaian dengan gerbang AND

I Gerbang NAND memerlukan transistor lebih sedikitdaripada gerbang AND

I Akan lebih banyak digunakan daripada Gated SR Latchdengan NOR

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 17

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Latch SR(Set-Reset)Latch SRTergerbangGated Latch D(Data)IC TTL Latch

Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Gated D (Data) LatchI Latch dapat digunakan sebagai elemen memori untuk sistem alarm

di contoh sebelumnya

I Gated latch lainnya adalah D latch

I Mempunyai sebuah masukan data, D

I Tidak akan terjadi kondisi race seperti latch RS

I Menyimpan nilai masukan dengan kontrol berupa sinyalclock

I Digunakan di rangkaian yang perlu menyimpan nilai

I Misalnya 'mengingat' nilai keluaran dari rangkaianadder/substractor

I Latch dapat dikatakan sebagai elemen penyimpan 1 bitdata

I Diimplementasikan dengan 18 transistor CMOS

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 18

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Latch SR(Set-Reset)Latch SRTergerbangGated Latch D(Data)IC TTL Latch

Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Gated D (Data) LatchSimbol, Tabel Karakteristik dan Diagram Pewaktuan

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 19

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Latch SR(Set-Reset)Latch SRTergerbangGated Latch D(Data)IC TTL Latch

Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

IC TTL Latch

Nomor IC Deskripsi

74279 latch set-reset (quad), aktif rendah

74363/74373 latch data transparan dengan keluaran 3 keadaan (oktal)

I IC 74363/74373

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 20

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Latch SR(Set-Reset)Latch SRTergerbangGated Latch D(Data)IC TTL Latch

Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Struktur dan Fungsi 74363/74373

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 21

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Flip-Flop Data(DFF)Flip-�op Toggle(T)Flip-�op JK(JKFF)IC TTL Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Sensitivitas Sinyal

I Sensitivitas elemen storage: Level-sensitive danEdge-triggered

I Level-sensitive: keluaran elemen dikontrol oleh levelmasukan clock (0 atau 1)

I Edge-triggered: keluaran elemen hanya berubah dititik transisi nilai clock

I Positive-edge: transisi sinyal clock dari 0 ke 1I Negative-edge: transisi sinyal clock dari 1 ke 0

I Latch merupakan elemen penyimpan dengan sensitivitaslevel

I Selama clock clk = 1 nilai keluaran akan tergantungdari nilai masukan D

I Dalam satu periode clock bisa terjadi lebih dari 1perubahan state keluaran Q

I Ini akan membedakannya dengan elemen penyimpan�ip-�op yang akan dibahas berikutnya

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 22

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Flip-Flop Data(DFF)Flip-�op Toggle(T)Flip-�op JK(JKFF)IC TTL Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Flip-�op

I Rangkaian latch (gated) merupakan level-sensitive

I State dapat berubah lebih dari sekali selama periode'aktif' dari sinyal clock

I Untuk logika positif, periode aktif adalah saat clk=1.Dan sebaliknya

I Flip-�op

I Elemen penyimpan 1 bitI Statenya berubah hanya sekali dalam satu periode

clockI Tipe: master-slave �ip-�op dan edge-triggered

�ip-�opI Jenis: DFF (data), TFF (toggle) dan JKFF

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 23

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Flip-Flop Data(DFF)Flip-�op Toggle(T)Flip-�op JK(JKFF)IC TTL Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Master-slave D Flip-�opI Dibentuk dari 2 buah gated D latch (38 transistor

CMOS): sebagai master dan slaveI master mengubah statenya saat clock = 1I slave mengubah statenya saat clock = 0

I Analisis diagram pewaktuan

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 24

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Flip-Flop Data(DFF)Flip-�op Toggle(T)Flip-�op JK(JKFF)IC TTL Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Master-slave D Flip-�op: Perilaku

I Saat clock=1, master melihat nilai dari sinyal masukanD, slave tidak berubah

I Qm mengikuti perubahan D, dan Qs konstan

I Saat clock=0, master berhenti mengikuti perubahannilai masukan D, sebaliknya slave merespon masukanQm dan mengubah statenya

I Karena Qm tidak berubah selama clock=0, slave hanyamengubah statenya sekalis aja selama satu siklus clock

I Dari sudut pandang keluaran

I Rangkaian mengubah Qs (keluaran �ip-�op) di titiktransisi negatif sinyal clock (perubahan dari 1→0)

I Disebut negative-edge-triggered D Flip-�op

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 25

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Flip-Flop Data(DFF)Flip-�op Toggle(T)Flip-�op JK(JKFF)IC TTL Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Simbol dan Karakteristik DFF Transisi Turun

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 26

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Flip-Flop Data(DFF)Flip-�op Toggle(T)Flip-�op JK(JKFF)IC TTL Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Efek Delay PropagasiI Sebelumnya efek delay propagasi diabaikan

I Dalam prakteknya, delay ini perlu diperhatikan

I Di master-slave D �ip-�op (negative-edge)

I nilai D harus tidak berubah (stabil) saat clock berubah dari1 ke 0 (transisi turun)

I Waktu minimum dimana sinyal D harus stabil sebelumtransisi clock turun disebut setup time (tsu)

I Waktu minimum dimana sinyal D harus stabil setelahtransisi clock disebut hold time (th)

I Nilai tipikal di CMOS: tsu = 3ns dan th = 2ns

I Untuk positive-edge triggered?http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 27

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Flip-Flop Data(DFF)Flip-�op Toggle(T)Flip-�op JK(JKFF)IC TTL Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Positive-Edge-triggered DFFI Rangkaian berfungsi sama dengan master-slave D �ip-�op dapat

dibentuk dengan 6 gerbang NAND (24 transistor)

I Saat clock = 0, keluaran gerbang 2 dan 3 tinggi

I P1 = P2 = 1, keluaran latch tidak berubah, berada dipresent statenya

I P3 = D dan P4 = D

I Saat clock = 1, nilai P3 dan P4 ditransmisikan lewat gerbang 2dan 3

I P2 = D dan P1 = D, sehingga Q = D dan Q = Dhttp://didik.blog.undip.ac.id @2014,Eko Didik Widianto 28

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Flip-Flop Data(DFF)Flip-�op Toggle(T)Flip-�op JK(JKFF)IC TTL Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Perilaku Positive DFF

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 29

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Flip-Flop Data(DFF)Flip-�op Toggle(T)Flip-�op JK(JKFF)IC TTL Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Disiplin Pewaktuan

I Untuk dapat beroperasi dengan reliabel, P3 dan P4 harusstabel saat clock berubah dari 0 ke 1 (transisi naik)

I Setup time dari �ip-�op sama dengan delay darimasukan D lewat gerbang 4 dan 1 ke P3

I Hold time diberikan oleh delay lewat gerbang 3, sebabsekali P2 stabil, perubahan di D tidak akan berpengaruh(mengubah state)

I Harus dipastikan bahwa setelah clock berubah ke 1, setiapperubahan di D tidak akan mempengaruhi keluaran latchselama clock=1

I Kasus 1: jika D=0 saat transisi naik clock, maka P2=0yang akan membuat keluaran gerbang 4 sama dengan 1selama clock=1, apapun nilai dari masukan D

I Kasus 2: jika D=1 saat transisi naik clock, maka P1=0yang memaksa keluaran gerbang 1 dan 3 sama dengan1, apapun nilai dari masukan D

I Sehingga, �ip-�op akan mengabaikan perubahanmasukan D selama clock=1http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 30

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Flip-Flop Data(DFF)Flip-�op Toggle(T)Flip-�op JK(JKFF)IC TTL Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Edge-triggered Flip-�opPositive-edge dan Negative-edge D Flip-�op

I Dua tipe rangkaian:

I positive-edge triggered D �ip-�op

I rangkaian merespon di transisi positif sinyal clock

I negative-edge triggered D �ip-�op

I rangkaian merespon di transisi negatif sinyal clock

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 31

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Flip-Flop Data(DFF)Flip-�op Toggle(T)Flip-�op JK(JKFF)IC TTL Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Membandingkan Elemen Penyimpan DataLatch, Positive-edge DFF dan Negative-edge DFF

I Elemen storage: Level-sensitive, positive-edge-sensitive,dan negative-edge-sensitive

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 32

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Flip-Flop Data(DFF)Flip-�op Toggle(T)Flip-�op JK(JKFF)IC TTL Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Masukan Preset dan Clear di DFF

I Diinginkan untuk mengeset sebuah �ip-�op (Q = 1) ataumeng-clear-kannya (Q = 0)

I Flip-�op umumnya mempunyai masukan preset danclear

I Input ini asinkron (tidak tergantung dari sinyal clock)

I Keluaran Q berubah seketika saat preset atau clearaktif (active-low)

posedge triggered DFF negedge triggered DFF

I Jika Preset = 0, keluaran Q = 1

I Jika Clear = 0, keluaran Q = 0http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 33

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Flip-Flop Data(DFF)Flip-�op Toggle(T)Flip-�op JK(JKFF)IC TTL Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Masukan Preset dan ClearNegative-edge-trigerred DFF (transisi turun)

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 34

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Flip-Flop Data(DFF)Flip-�op Toggle(T)Flip-�op JK(JKFF)IC TTL Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Simbol DFF Transisi Turun, Preset, Clear

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 35

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Flip-Flop Data(DFF)Flip-�op Toggle(T)Flip-�op JK(JKFF)IC TTL Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Masukan Preset dan ClearPosedge-triggered D Flip-�op with Preset and Clear

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 36

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Flip-Flop Data(DFF)Flip-�op Toggle(T)Flip-�op JK(JKFF)IC TTL Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Simbol DFF Transisi Naik, Preset, Clear

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 37

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Flip-Flop Data(DFF)Flip-�op Toggle(T)Flip-�op JK(JKFF)IC TTL Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Flip-�op Toggle (T)

I Menggunakan sebuah posedge D �ip-�op dan rangkaian logikauntuk mendrive masukannya

I Feedback membuat sinyal masukan D sama dengan nilai Q atauQ di bawah kontrol sinyal T

I Saat T = 1 → state rangkaian 'toggle' saat transisi clocknaik

I Saat T = 0 → statenya tetapI Digunakan sebagai elemen di rangkaian pencacah

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 38

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Flip-Flop Data(DFF)Flip-�op Toggle(T)Flip-�op JK(JKFF)IC TTL Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Rangkaian dan Diagram Pewaktuan TFF

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 39

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Flip-Flop Data(DFF)Flip-�op Toggle(T)Flip-�op JK(JKFF)IC TTL Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Simbol dan Fungsi TFF

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 40

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Flip-Flop Data(DFF)Flip-�op Toggle(T)Flip-�op JK(JKFF)IC TTL Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Flip-�op JK

I Flip-�op JK dapat diturunkan dari �ip-�op D, denganmenggunakan 2 masukan J dan K, sehinggaD = JQ + KQ

I Flip-�op JK mengkombinasikan perilaku �ip-�op SR dan�ip-�op T

I J = S dan K = R untuk semua nilai, kecuali untukJ = K = 1 (�ip-�op SR)

I Jika J=K=1, �ip-�op menbalik (toggle) statenya seperti�ip-�op T

I Dapat digunakan sebagai storage seperti DFF dan SR FF.Dan juga T FF dengan menghubungkan J dan K sebagai T

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 41

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Flip-Flop Data(DFF)Flip-�op Toggle(T)Flip-�op JK(JKFF)IC TTL Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Rangkaian dan Diagram Pewaktuan JKFF

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 42

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Flip-Flop Data(DFF)Flip-�op Toggle(T)Flip-�op JK(JKFF)IC TTL Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Simbol dan Fungsi TFF

I Dapat digunakan sebagai elemen penyimpan 1 bit

I DFF: menghubungkan Data ke masukan J dan Data kemasukan K

I TFF: menghubungkan Toggle ke J dan K

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 43

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Flip-Flop Data(DFF)Flip-�op Toggle(T)Flip-�op JK(JKFF)IC TTL Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

IC TTL Flip-�op

Nomor IC Deskripsi

7474 DFF transisi naik dengan preset dan clear (dual)

7476 JKFF dengan preset dan clear (dual)

7479 DFF (dual)

74112 JKFF transisi turun dengan preset dan clear (dual)

74173 DFF dengan keluaran tiga keadaan (quad)

74174 DFF dengan clear (hex)

74574/74874 DFF dengan keluaran tiga keadaan (oktal)

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 44

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Flip-Flop Data(DFF)Flip-�op Toggle(T)Flip-�op JK(JKFF)IC TTL Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

IC 7474

I Dual D-type Positive-Edge-Trigerred Flip-Flops withPreset and Clear

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 45

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Flip-Flop Data(DFF)Flip-�op Toggle(T)Flip-�op JK(JKFF)IC TTL Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

IC 7474: Rangkaian dan Fungsi

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 46

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Flip-Flop Data(DFF)Flip-�op Toggle(T)Flip-�op JK(JKFF)IC TTL Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

IC 74574: 8 DFF Transisi Naik, Tiga Keadaan

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 47

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Register DataRegister GeserIC TTL Register

Counter/Pencacah

Ringkasan

Lisensi

Register

I Sebuah DFF dapat menyimpan 1 bit data

I Register n bit dibentuk dari n buah DFF

I masukan Clk digunakan secara bersama oleh tiap DFFpenyusunnya

I DFF dapat digunakan untuk membentuk register datadan register geser

I Register data digunakan untuk menyimpan data

I Data yang tersimpan di register bersifat sementara(volatile)

I Register geser digunakan dalam operasi pergeseran bitserta dalam konversi data serial ke paralel dan dataparalel ke serial

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 48

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Register DataRegister GeserIC TTL Register

Counter/Pencacah

Ringkasan

Lisensi

Register Data

I Register Data n-bit tersusun atas n buah �ip-�ipuntuk menyimpan n-bit data

I Perilaku register data n bit transisi naik

I Untuk setiap DFF, Q = D saat transisi naik ClkI Keluaran Q(t + 1) = Q(t) atau tetap saat kondisi Clk

lainnya

I Register data di prosesor: register akumulator, registerstatus, register alamat, register instruksi, register dataserial terima (RX)/kirim (TX)

I Contoh penggunaan register:

I Menahan/menyimpan (hold) sebuah keluaran nilai datadari suatu rangkaian aritmatika

I Menahan/menyimpan (hold) nilai pencacah dalamrangkaian counter/pencacah

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 49

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Register DataRegister GeserIC TTL Register

Counter/Pencacah

Ringkasan

Lisensi

Register Data 4 Bit

I Saat transisi naik Clk , register akan bernilaiQ[3 : 0] = D[3 : 0]

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 50

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Register DataRegister GeserIC TTL Register

Counter/Pencacah

Ringkasan

Lisensi

Register Geser

I Merupakan sebuah register yang dapat menggeser isinyasejauh 1 bit perclock

I Bisa geser ke kanan atau ke kiri

I Register geser kiri

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 51

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Register DataRegister GeserIC TTL Register

Counter/Pencacah

Ringkasan

Lisensi

Register Geser Kiri

I Data digeser ke kiri secaraserial menggunakanmasukan In

I Isi dari tiap �ip-�opditransfer ke �ip-�opberikutnya di tiap transisinaik sinyal clock

Q3 Q2 Q1 Q0 In

t0 0 0 0 0 1

t1 0 0 0 1 0

t2 0 0 1 0 1

t3 0 1 0 1 1

t4 1 0 1 1 1

t5 0 1 1 1 0

t6 1 1 1 0 0

t7 1 1 0 0 0

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 52

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Register DataRegister GeserIC TTL Register

Counter/Pencacah

Ringkasan

Lisensi

Register Geser Kanan dengan Akses Paralel

I Tipe transfer data di sistem komputer

I transfer paralel: trasfer n-bit data sekaligusI transfer serial: transfer 1-bit bit dalam satu waktu

I Untuk mentransfer data secara serial, data diletakkandalam suatu register secara paralel (dalam waktu 1 siklusclock) dan digeser keluar satu bit dalam satu waktu

I Disebut sebagai konversi data parallel-ke-serial

I Jika bit-bit diterima secara serial, setelah n siklus clock,isid ari register dapat diakses secara paralel sebagaisebuah data n-bit

I Disebut sebagai konversi data serial-ke-paralel

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 53

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Register DataRegister GeserIC TTL Register

Counter/Pencacah

Ringkasan

Lisensi

Register Geser dengan Akses Paralel

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 54

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Register DataRegister GeserIC TTL Register

Counter/Pencacah

Ringkasan

Lisensi

IC TTL Register

Nomor IC Deskripsi

74164 register geser 8 bit, keluaran paralel, masukan clear

asinkron

74165 register geser 8 bit, masukan paralel, dengan keluaran

komplementer

74166 register geser 8 bit, masukan paralel

74194/74195 register geser universal dua arah (bidireksional) 4 bit

74198 register geser universal dua arah (bidireksional) 8 bit

74273 register 8 bit dengan reset

74278 register prioritas 4 bit, dapat di-kaskade, masukan

data terkunci

74299 register geser universal dua arah (bidireksional) 8 bit,

keluaran tiga-keadaan

74374 register oktal dengan keluaran tiga-keadaan

74377 register 8 bit dengan kontrol enable detak

74396 register oktal, akses paralelhttp://didik.blog.undip.ac.id @2014,Eko Didik Widianto 55

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Register DataRegister GeserIC TTL Register

Counter/Pencacah

Ringkasan

Lisensi

74164: Register Geser 8 Bit, SerIn/ParOut

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 56

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Register DataRegister GeserIC TTL Register

Counter/Pencacah

Ringkasan

Lisensi

74165/74166: Register Geser 8 Bit, Load Paralel

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 57

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Register DataRegister GeserIC TTL Register

Counter/Pencacah

Ringkasan

Lisensi

74165/74166: Perilaku

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 58

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Register DataRegister GeserIC TTL Register

Counter/Pencacah

Ringkasan

Lisensi

74299: Register Geser Universal 8 Bit

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 59

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Register DataRegister GeserIC TTL Register

Counter/Pencacah

Ringkasan

Lisensi

Operasi IC 74299

1. SIPO (serial-in parallel-out), register diisi dengan data serial 1 bitdalam satu waktu dan data yang tersimpan di register tersediasebagai keluaran paralel

2. SISO (serial-in serial-out), data digeser secara serial dari masukanke keluaran serial, 1 bit dalam satu waktu

3. PISO (parallel-in serial-out), register diisi dengan data paralel n bitdan isi register digeser keluar secara serial 1 bit dalam satu waktu

4. PIPO (parallel-in parallel-out), register diisi dengan data paralel nbit dan isi register dapat tersedia sebagai keluaran paralel

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 60

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Register DataRegister GeserIC TTL Register

Counter/Pencacah

Ringkasan

Lisensi

IC 74374: Register Data 8 Bit

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 61

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Register DataRegister GeserIC TTL Register

Counter/Pencacah

Ringkasan

Lisensi

IC 74374: Register Data 8 Bit

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 62

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

PencacahAsinkronPencacah SinkronPencacah Sinkrondengan DFFIC TTL Pencacah

Ringkasan

Lisensi

Pencacah

I Rangkaian counter ini dapat digunakan melakukanbeberapa fungsi, misalnya

I Menghitung kejadian dari suatu eventI Membangkitkan interval waktu untuk mengontrol

pekerjaan-pekerjaan (task) di sistem digitalI Menghitung waktu mundur antar eventI Menyediakan alamat baru di pencacah program (PC)

I Rangkaian counter yang paling sederhana dapat dibuatdengan menggunakan �ip-�op T

I �ip-�op T secara natural cocok untukdiimplementasikan di operasi pencacahan

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 63

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

PencacahAsinkronPencacah SinkronPencacah Sinkrondengan DFFIC TTL Pencacah

Ringkasan

Lisensi

Pencacah Sinkron dan Asinkron

I Pencacah asinkron dibentuk dengan memberikan sinyalClk ke terminal detak satu �ip-�op

I Masukan detak untuk �ip-�op berikutnya diperoleh darikeluaran �ip-�op sebelumnya (efek serupa RCA)

I Lambat karena sumber Clk merambat dari satu �ip-�opke �ip-�op lainnya

I Pencacah sinkron dibentuk dengan memberikan sinyalClk ke semua �ip-�op di waktu yang sama

I Semua �ip-�op menggunakan sumber detak yang samaI Mempunyai respon yang lebih cepat daripada pencacah

asinkron

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 64

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

PencacahAsinkronPencacah SinkronPencacah Sinkrondengan DFFIC TTL Pencacah

Ringkasan

Lisensi

Pencacah Naik dengan Flip-�op TI Pencacah 3-bit yang dapat mencacah 0 sampai 7 atau pencacah

module-8

I Masukan clock untuk ketiga �ip-�op dikoneksikan secarakaskade

I Flip-�op pertama terkoneksi ke ClockI Flip-�op berikutnya, sinyal clocknya didrive dari

keluaran Q �ip-�op sebelumnyaI Rangkaian seperti ini disebut sebagai pencacah

asinkron atau pencacah ripple

I Masukan T tiap �ip-�op dikoneksikan ke konstan 1

I State tiap �ip-�op akan dibalik (toggle) setiap transisinaik clocknya

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 65

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

PencacahAsinkronPencacah SinkronPencacah Sinkrondengan DFFIC TTL Pencacah

Ringkasan

Lisensi

Diagram Pewaktuan Pencacah Naik

I Nilai Q0 akan toggle setiap clock cycle

I Perubahan terjadi setelah transisi naik sinyal clock

I Nilai Q1 akan toggle setelah transisi turun dari Q0, demikian jugaQ2

I Nilai Q2Q1Q0 menunjukkan nilai pencacahnya

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 66

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

PencacahAsinkronPencacah SinkronPencacah Sinkrondengan DFFIC TTL Pencacah

Ringkasan

Lisensi

Pencacah Turun dengan Flip-�op T

I Mirip dengan rangkaian pencacah naik, kecuali masukanclock �ip-�op kedua dan seterusnya berasal darikeluaran Q �ip-�op sebelumnya

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 67

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

PencacahAsinkronPencacah SinkronPencacah Sinkrondengan DFFIC TTL Pencacah

Ringkasan

Lisensi

Diagram Pewaktuan Pencacah Turun

I Nilai Q0 akan toggle setiap clock cycle

I Perubahan terjadi setelah transisi naik sinyal clock

I Nilai Q1 akan toggle setelah transisi naik dari Q0, demikian jugaQ2

I Nilai Q2Q1Q0 menunjukkan nilai pencacahnya

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 68

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

PencacahAsinkronPencacah SinkronPencacah Sinkrondengan DFFIC TTL Pencacah

Ringkasan

Lisensi

Latihan

I Desain pencacah naik/turun 3-bit menggunakan �ip-�opT. Sebuah masukan kontrol Up/Down harus disertakan.Jika Up/Down = 0 rangkaian berfungsi sebagaipencacah naik. Jika Up/Down = 1 rangkaian berfungsisebagai pencacah turun.

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 69

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

PencacahAsinkronPencacah SinkronPencacah Sinkrondengan DFFIC TTL Pencacah

Ringkasan

Lisensi

Pencacah Sinkron

I Dapat dibentuk dengan TFF

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 70

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

PencacahAsinkronPencacah SinkronPencacah Sinkrondengan DFFIC TTL Pencacah

Ringkasan

Lisensi

Perilaku Pencacah Naik

I masukan T tiap TFF akan bernilai sebagai berikut:

T0 = 1

T1 = Q0

T2 = Q0Q1

T3 = Q0Q1Q2

I Implementasi rangkaian pencacah sinkron tersebut membutuhkangerbang AND.

I Masukan T0 dihubungkan logika 1, sehingga Q0 akanmembalik setiap transisi naik Clk

I Masukan T1 dihubungkan dengan Q0

I Masukan T2 membutuhkan gerbang AND-2 untukmemperoleh Q0Q1

I Masukan T3 membutuhkan gerbang AND-3 untukmemperoleh Q0Q1Q2

I Masalah fan-in: pencacah n bit akan membutuhkan gerbang ANDn − 1

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 71

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

PencacahAsinkronPencacah SinkronPencacah Sinkrondengan DFFIC TTL Pencacah

Ringkasan

Lisensi

Rangkaian

I Faktorisasi untuk mengatasi fan-in

T0 = 1

T1 = Q0

T2 = T1Q1

T3 = T2Q2

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 72

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

PencacahAsinkronPencacah SinkronPencacah Sinkrondengan DFFIC TTL Pencacah

Ringkasan

Lisensi

Diagram Pewaktuan

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 73

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

PencacahAsinkronPencacah SinkronPencacah Sinkrondengan DFFIC TTL Pencacah

Ringkasan

Lisensi

Pencacah Naik n-Bit

I Untuk sebarang pencacah naik n bit, rangkaiannyadapat dibentuk dengan persamaan masukan Ti sebagaiberikut:

T0 = 1

T1 = Q0

T2 = T1Q1

T3 = T2Q2

.

Tn = Tn−1Qn−1

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 74

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

PencacahAsinkronPencacah SinkronPencacah Sinkrondengan DFFIC TTL Pencacah

Ringkasan

Lisensi

Pencacah Sinkron dengan Enable dan Clear

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 75

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

PencacahAsinkronPencacah SinkronPencacah Sinkrondengan DFFIC TTL Pencacah

Ringkasan

Lisensi

Pencacah Sinkron dengan DFF

I Pencacah akan mempunyai urutan nilai 0, 1, 2, 3, · · · , 15, 0, 1, · · ·I Nilai pencacah ini diberikan oleh keluaran DFF Q3Q2Q1Q0

I Pencacah akan aktif saat Enable = 1. Saat Enable = 0 maka nilaipencacah tidak berubah

I Nilai Q0 akan membalik (toggle) setiap transisi naik Clk. Agar Q0

membalik di transisi naik Clk berikutnya, maka nilai D0 harusbernilai Q0 saat Enable = 1 . Persamaannya adalahD0 = Q0 ⊕ Enable

I Nilai Q1 akan membalik setelah nilai Q0 = 1. Agar Q1 membalikdi transisi naik Clk berikutnya, maka nilai D1 harus bernilai Q1

saat Q0 = 1 dan Enable = 1 . Persamaannya adalahD1 = Q1 ⊕ Q0 · Enable

I Nilai Q2 akan membalik setelah nilai Q1Q0 = 11. Agar Q2

membalik di transisi naik Clk berikutnya, maka nilai D2 harusbernilai Q2 saat Q1 = 1, Q0 = 1 dan Enable = 1 . Persamaannyaadalah D2 = Q2 ⊕ Q1 · Q0 · Enable

I Nilai Q3 akan membalik setelah nilai Q2Q1Q0 = 111. Agar Q3

membalik di transisi naik Clk berikutnya, maka nilai D3 harusbernilai Q3 saat Q2 = 1, Q1 = 1, Q0 = 1 dan Enable = 1 .Persamaannya adalah D3 = Q3 ⊕ Q2 · Q1 · Q0 · Enable

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 76

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

PencacahAsinkronPencacah SinkronPencacah Sinkrondengan DFFIC TTL Pencacah

Ringkasan

Lisensi

Pencacah Sinkron dengan DFF

D0 = Q0 ⊕ Enable

D1 = Q1 ⊕ Q0 · EnableD2 = Q2 ⊕ Q1 · Q0 · EnableD3 = Q3 ⊕ Q2 · Q1 · Q0 · Enable

I Untuk pencacah yang lebih besar, masukan D di tiapDFF bernilai Di = Qi ⊕ Qi−1 · Qi−2 · · ·Q1 · Q0 · Enable�> masalah fan-in

D0 = Q0 ⊕ Enable

D1 = Q1 ⊕ Q0 · EnableD2 = Q2 ⊕ Q1 · (Q0 · Enable)D3 = Q3 ⊕ Q2 · (Q1 · Q0 · Enable)

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 77

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

PencacahAsinkronPencacah SinkronPencacah Sinkrondengan DFFIC TTL Pencacah

Ringkasan

Lisensi

Rangkaian Pencacah Sinkron DFF

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 78

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

PencacahAsinkronPencacah SinkronPencacah Sinkrondengan DFFIC TTL Pencacah

Ringkasan

Lisensi

Rangkaian Pencacah Sinkron dengan Load Paralel

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 79

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

PencacahAsinkronPencacah SinkronPencacah Sinkrondengan DFFIC TTL Pencacah

Ringkasan

Lisensi

IC TTL Pencacah

Nomor IC Deskripsi

7493 4-bit binary counter

74161 synchronous 4-bit binary counter with asynchronous clear

74163 synchronous 4-bit binary counter with synchronous clear

74169 synchronous 4-bit up/down binary counter

74177/74197 presettable binary counter/latch

74191 synchronous up/down binary counter

74193 synchronous up/down binary counter with clear

74393 dual 4-bit binary counter

74453 dual binary counter, synchronous

74455 dual binary up/down counter, synchronous, preset input

74461 8-bit presettable binary counter with three-state outputs

74491 10-bit binary up/down counter with limited preset and

three-state outputs

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 80

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

PencacahAsinkronPencacah SinkronPencacah Sinkrondengan DFFIC TTL Pencacah

Ringkasan

Lisensi

IC 74393: Dual Pencacah Asinkron 4 Bit

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 81

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

PencacahAsinkronPencacah SinkronPencacah Sinkrondengan DFFIC TTL Pencacah

Ringkasan

Lisensi

IC 74393: Fungsi Logika

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 82

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

PencacahAsinkronPencacah SinkronPencacah Sinkrondengan DFFIC TTL Pencacah

Ringkasan

Lisensi

IC 74193: Dual Pencacah Sinkron 4 Bit,Naik/Turun

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 83

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

PencacahAsinkronPencacah SinkronPencacah Sinkrondengan DFFIC TTL Pencacah

Ringkasan

Lisensi

IC 74193: Fungsi Logika

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 84

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

PencacahAsinkronPencacah SinkronPencacah Sinkrondengan DFFIC TTL Pencacah

Ringkasan

Lisensi

IC 74193: Perilaku

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 85

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

PencacahAsinkronPencacah SinkronPencacah Sinkrondengan DFFIC TTL Pencacah

Ringkasan

Lisensi

Pencacah Sinkron n x 4 Bit

I Menggunakan 74193

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 86

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Ringkasan Kuliah

I Yang telah kita pelajari hari ini:

I Elemen rangkaian sekuensial berupa latch dan �ip-�op:

I Latch: RS-latch, D-latch, gated latchI Flip-�op: master-slave D �ip-�op, edge-trigerred

�ip-�op, T �ip-�op dan JK �ip-�opI Perbedaan antara latch dan �ip-�op

I Register dan pencacah

I Register data dan register geserI Pencacah asinkron dan sinkron

I Yang akan kita pelajari di pertemuan berikutnya adalahtentang perancangan rangkaian sekuensial menggunakandiagram keadaan (Moore)

I Pelajari: http://didik.blog.undip.ac.id/2014/02/25/tkc205-sistem-digital-2013-genap/

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 87

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

Bacaan Lebih Lanjut

1. Bab 7: Stephen Brown and Zvonko Vranesic, Fundamentalsof Digital Logic with Verilog/VHDL, 2nd Edition,McGraw-Hill, 2005Tentang �ip-�op, register, pencacah dan prosesor sederhana

2. Datasheet CD4043BE (Texas): Quad Latch SR NOR.http://www.ti.com/lit/gpn/CD4043B

3. Datasheet CD4044BE (Texas), 54LS279 , 74LS279: QuadLatch SR NAND. http://www.ti.com/lit/gpn/CD4044B

4. Datasheet SN74LS74A: Dual D-type Positive-Edge-TrigerredFlip-Flops with Preset and Clear.http://www.ti.com/lit/gpn/SN74LS74A

http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 88

RangkaianSekuensial

@2014,Eko DidikWidianto

ElemenPenyimpanKeadaan

Latch (Pengunci)

Flip-�op

Register

Counter/Pencacah

Ringkasan

Lisensi

LisensiCreative Common Attribution-ShareAlike 3.0 Unported (CC BY-SA3.0)

I Anda bebas:I untuk Membagikan � untuk menyalin, mendistribusikan,

dan menyebarkan karya, danI untuk Remix � untuk mengadaptasikan karya

I Di bawah persyaratan berikut:I Atribusi � Anda harus memberikan atribusi karya sesuai

dengan cara-cara yang diminta oleh pembuat karya tersebutatau pihak yang mengeluarkan lisensi. Atribusi yangdimaksud adalah mencantumkan alamat URL di bawahsebagai sumber.

I Pembagian Serupa � Jika Anda mengubah, menambah,atau membuat karya lain menggunakan karya ini, Andahanya boleh menyebarkan karya tersebut hanya denganlisensi yang sama, serupa, atau kompatibel.

I Lihat: Creative Commons Attribution-ShareAlike 3.0 UnportedLicense

I Alamat URL: http://didik.blog.undip.ac.id/2014/02/25/tkc205-sistem-digital-2013-genap/http://didik.blog.undip.ac.id @2014,Eko Didik Widianto 89