13-KEL03-TT2D-AJIE

-

Upload

ajie-rachmat-aditya -

Category

Documents

-

view

5 -

download

3

description

Transcript of 13-KEL03-TT2D-AJIE

I. JUDUL : RANGKAIAN FLIP FLOP

II. TUJUAN:Dengan melaksanakan praktikum ini diharapkan mahasiswa dapat melakukan : Merangkai dan mengamati kerja rangkaian dasar flip flop. Merangkai dan mengoperasikan IC D FF, 7474 dan IC JK FF, 7476. Membuktikan table kebenaran masing masing flip-flop.

III. DASAR TEORI:Sistem digital umumnya dibangun dengan menggunakan rangkaian rangkaian kombinatorial dan elemen elemen memory. Elemen memory yang paling banyak digunakan adalah flip flop (FF) . FF merupakan suatu rangkaian logika dengan 2 output, yang satu merupakan kebalikan dari yang lainnya (biasanya adalah Q dan Q). output Q disebut output FF normal, sedangkan Q adalah output FF inverse.Berbagai macam flip flop yang sering digunakan adalah SR flip flop yand biasanya terdiri dari rangkaian dasar NOR atau NAND gate, sedangkan JK flip flop dibangun dari 2 buah clock RS FF yang disambungkan menjadi satu. Jenis lainnya yaitu : T FF, D FF, yang juga merupakan modifikasi dari SR FF.Gambar berikut ini merupakan symbol dari berbagai macam flip flop beserta table kebenarannya.

1.1. SR FF dengan NOR GateTabel 2.1 Tabel Kebenaran SR Flip-FlopS QFFC QINPUTOUTPUT

SRQQ

00MEMORI

1010

0101

11TERLARANG

1.2. SR FF dengan NAND GateTabel 2.2 Tabel Kebenaran SR Flip-FlopINPUTOUTPUT

S QFFC QSRQQ

00TERLARANG

1001

0110

11MEMORI

1.3. JK FLIP-FLOP Tabel 2.3 Tabel Keebenaran JK Flip-FlopJ QFFK QINPUTOUTPUT

SRQQ

00MEMORI

1001

0110

11TOGGLE

1.4. D FLIP-FLOP

Tabel 2.4 Tabel Kebenaran D Flip-Flop

D QFF Q QINPUTOUTPUT

DQQ

101

010

IV. ALAT YANG DIPERGUNAKAN:

NOALAT ALAT DAN BAHANJUMLAH

1IC 7400 (Quad 2 input NAND Gate)IC 7402 (Quad 2 input NOR Gate)IC 7474 (D FF)IC 7476 (Dual JK FF)1111

2Power supply 1

3Multimeter1

4Protoboard1

5Banana to banana cable2

6Resistor2

7LED2

8Kabel jumper10

V. LANGKAH KERJA:Langkah-langkah dalam melakukan percobaan adalah sebagai berikut :1. Memperhatikan kaki IC 7400 pada gambar 4.1, di mana notasi A dan B menunjukan input sedangkan Y adalah output, lengkapi Tabel 6.1.

2. Membuat rangkaian seperti Gambar 4.2.

3. Mengatur power supply pada 5 volt.4. Memberikan masukan S dan R sesuai Tabel 6.2. Mencatat hasil pada Tabel 6.25. Memperhatikan kaki IC 7402 pada Gambar 4.3, di mana notasi A dan B menunjukan input sedangkan Y adalah output. Melengkapi Tabel 6.3.

6. Membuat rangkaian seperti Gambar 4.4.

7. Memberikan masukan S dan R sesuai Tabel 6.4. Mencatat hasil pada Tabel 6.4.8. Memperhatikan kaki IC 7474 pada Gambar 4.5. Melengkapi Tabel 6.5.

9. Membuat rangkaian seperti Gambar 4.6.

10. Memberikan masukan sesuai sesuai Tabel 6.6. Mencatat hasil pada Tabel 6.6.11. Memperhatikan kaki IC 7476 pada Tabel 4.7. Melengkapi Tabel 6.7.12. Membuat rangkaian seperti gambar 4.8 berikut.

13. Memberikan masukan sesuai Tabel 6.8. Mencatat hasil pada Tabel 6.8

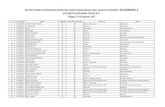

VI. DATA HASIL PERCOBAAN:Tabel 6.1 Identifikasi Kaki IC 7400NoGerbang Ke-Input 1Input 2Output

11123

22456

331098

44131211

Tabel 6.2 RS-FF Input Aktif Rendah (NAND Gate)InputOutput

SRQ

0011

0110

1110

1001

1101

Tabel 6.3. Identifikasi Kaki IC 7402NoGerbang Ke-Input 1Input 2Output

11231

22564

338910

44111213

Tabel 6.4 RS-FF Input Aktif Tinggi (NOR Gate)InputOutput

SRQ

1100

1010

0010

0101

0001

Tabel 6.5. Identifikasi Kaki IC 7474 D-FFNoInputOutput

PRECLRClockDQ

1412356

21013111238

Tabel 6.6 Tabel Kebenaran IC 7474 D-FFInputOutput

PRECLRClockDQ

00XX11

01XX10

10XX01

11001

11110

Tabel 6.7. Identifikasi Kaki IC 7476 D-FFNoInputOutput

PRECLRCLKJKQ

12314161514

27869121110

Tabel Kebenaran IC 7476 JK-FFInputOutput

PRECLRCLKKJQ

00XXX11

01XXX10

10XXX01

110001

110101

110001

1111 toggle 1 0

111010

110010

1111toggle1 0

VII. ANALISA:

Pada tabel 6.2 RS-FF Input Aktif Rendah (NAND Gate) dapat diketahui bahwaInput R = 1 dan S = 0 maka output Q menyala. (aktif)input R = 0 dan S = 0 maka output Q menghasilkan memoryinput R = 1 dan S = 1 maka output Q menghasilkan output terlaranginput R = 0 dan = 0 maka output Q akan mati (tidak aktif)RS-FF Input Aktif Rendah (NAND Gate) yaitu rangkaian yang akan aktif jika inputnya diberikan logic 0. Pada tabel 6.4 RS-FF Input Aktif Tinggi (NOR Gate) dapat diketahui bahwainput R = 1 dan S = 0 maka output Q menyala. (aktif)input R = 1 dan S = 1 maka output Q menghasilkan terlarangInput R = 0 dan S = 0 maka output Q menghasilkan output memoryInput R = 0 dan S = 1 maka output Q akan mati (tidak aktif)RS-FF Input Aktif Tinggi (NOR Gate) yaitu rangkaian yang akan aktif jika inputnya diberikan logic 1. Pada tabel 6.6 IC D-FF 7474 dapat diketahui bahwa input preset = 1 dan clear = 0 maka output Q menyala. (aktif)input preset = 1 dan clear = 1 maka output Q menghasilkan memoryinput preset = 0 dan clear = 0 maka output Q menghasilkan output terlaranginput preset = 0 dan clear = 1 maka output Q akan mati (tidak aktif) Pada tabel 6.8 IC JK-FF 7476dapat diketahui bahwaPreset berlogik 0 dan input Clear berlogic 1. (Q aktif)Preset , Clear, dan J berlogik 1, dan input K berlogik 0. (Q aktif)sedangkan pada saat,Preset berlogik 1 dan input Clear berlogic 0.(Q tidak aktif)Preset , Clear, berlogik 1, input J berlogik 0 dan K berlogik 1. (Q tidak aktif)

TIMING DIAGRAM 1

TIMING DIAGRAM 2

VIII. KESIMPULAN:Dari percobaan yang telah di lakukan, dapat di simpulkan bahwa: IC D FF 7474 merupakan IC yang aktif tinggi, sedangkan IC JK FF 7476 merupakan IC yang aktif rendah. Pada JK-FF jika input pada J berlogik 0 maka output Q pasti akan berlogik 0 sedangkan ketika J berlogik 1 maka output Q pasti akan berlogik 1. Clock di pasang pada rangkaian untuk mengetahui timing diagramnya.

IX. PERTANYAAN DAN TUGAS:

1. Pada rangkaian FF mempergunakan gerbang NAND, kondisi input bagaimana output aktif (menyala)?2. Peda rangkaian FF mempergunakan gerbang NOR, kondisi input bagaimana output aktif (menyala)?3. Apa yang dimaksud dengan input aktif rendah dan input aktif tinggi?4. Pada rangakain D-FF, kondisi input bagaimana output aktif (menyala)?5. Pada rangkaia JK-FF, kondisi input bagaimana output aktif (menyala)?6. Apa fungsi input Preset dan Clear pada IC 7474 dan 7476 ?7. Apa perbedaan input sinkron dengan input asinkron pada FF?

JAWABAN:

1. Output aktif menyala pada saat R = 1 dan S = 0.2. Output aktif menyala pada saat R = 1 dan S = 0.3. Input aktif rendah merupakan rangkaian yang outputnya akan aktif jika inputnya 0.Input aktif tinggi merupakan rangkaian yang outputnya akan aktif jika inputnya 1.4. Pada saat input preset berlogik 0 dan input clear berlogik 1, dan pada saat input preset, clear dan D berlogik 1.5. Output menyala pada kondisi input :Preset berlogik 0 dan input Clear berlogic 1.Preset , Clear, dan J berlogik 1, dan input K berlogik 0.6. Preset : merubah / mengaktifkan output jika input logic merupakan 1.Clear : merubah / mengaktifkan output yang inputnya bernilai 0.7. input sinkron merupakan input yang clocknya bekerja secara bersamaan. sedangkan pada input asinkron input clocknya bekerja secara bertahap